不揮発性半導体記憶装置及びその製造方法

【課題】制御性の高い不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、第1のメモリセルアレイ層と、第1のメモリセルアレイ層の上に形成された第1の絶縁層と、第1の絶縁層の上に形成された第2のメモリセルアレイ層と、第1の絶縁層を介して上下に位置する第1及び第2の浮遊ゲートの第1の方向の両側面にゲート間絶縁層を介して形成され、第1の方向と直交する第2の方向に延びる制御ゲートと、第1の絶縁層を介して上下に位置する第1及び第2の選択ゲートの第1の方向の両側面にゲート間絶縁層を介して形成され、第2の方向に延び、第1及び第2の半導体層並びに第1及び第2のゲート絶縁層と共に補助トランジスタを形成する補助ゲートとを備える。

【解決手段】不揮発性半導体記憶装置は、第1のメモリセルアレイ層と、第1のメモリセルアレイ層の上に形成された第1の絶縁層と、第1の絶縁層の上に形成された第2のメモリセルアレイ層と、第1の絶縁層を介して上下に位置する第1及び第2の浮遊ゲートの第1の方向の両側面にゲート間絶縁層を介して形成され、第1の方向と直交する第2の方向に延びる制御ゲートと、第1の絶縁層を介して上下に位置する第1及び第2の選択ゲートの第1の方向の両側面にゲート間絶縁層を介して形成され、第2の方向に延び、第1及び第2の半導体層並びに第1及び第2のゲート絶縁層と共に補助トランジスタを形成する補助ゲートとを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本明細書記載の技術は、不揮発性半導体記憶装置及びその製造方法に関する。

【背景技術】

【0002】

電気的に書き換え可能で且つ高集積化が可能な不揮発性半導体記憶装置として、NAND型フラッシュメモリが知られている。従来のNAND型フラッシュメモリのメモリトランジスタは絶縁膜を介して電荷蓄積層(浮遊ゲート)と制御ゲートが積層されたスタックゲート構造をしている。複数個のメモリトランジスタを、隣接するもの同士でソース若しくはドレインを共有するような形で列方向に直列接続させ、その両端に選択ゲートトランジスタを配置して、NANDセルユニットが構成される。NANDセルユニットの一端はビット線に接続され、他端はソース線に接続される。NANDセルユニットをマトリクス状に配置することにより、メモリセルアレイが構成される。また、行方向に並ぶNANDセルユニットをNANDセルブロックと呼ぶ。同一行に並ぶ選択ゲートトランジスタのゲートは、同一の選択ゲート線に接続され、同一行に並ぶメモリトランジスタの制御ゲートは、同一のワード線に接続される。NANDセルユニット内にN個のメモリトランジスタが直列接続されている場合、1つのNANDセルブロック内に含まれるワード線はN本となる。

【0003】

このようなNAND型フラッシュメモリにおいては、微細化に伴うゲート長縮小と隣接トランジスタ間隔が狭まることで、以下に述べる種々の課題が生じている。例えば、(a)近接ゲート間などの寄生容量の増大、ショートチャネル効果(SCE)などに起因した制御ゲートの電界によるドレイン電流制御性の低下、(b)隣接ゲート間干渉効果の増大、(c)隣接電極間リークの増大、(d)ゲート電極の高アスペクト化に起因したゲート加工時のパターンヨレ・倒壊、(e)電荷蓄積層に蓄積できる電子数(ビット当たりの電子数)の大幅減少に起因したデータリテンション特性の劣化、などの課題である。このため従来のNAND型フラッシュメモリでは、メモリセルの書込み/消去ウィンドウが大幅に低下し、微細化の物理限界に到達しつつある。

【0004】

今後の高集積化の方法の一手法として、メモリセルトランジスタを立体的に何層も積んでいく「3次元積層型」のメモリがある。具体的には、窒化膜トラップ型(SONOS、MONOS)セルを積層する構造が論文等で多く提案されているが、窒化膜トラップ型セル構造は、加工(積層化)が容易であるというメリットがあるものの、窒化膜に電子をトラップさせる特性上、消去特性とデータリテンション特性が浮遊ゲート型セルに比べて悪い事が大きな課題である。

【0005】

一方、従来の様な浮遊ゲート電極に電荷を蓄積する浮遊ゲート型メモリセル構造は、制御ゲート電極とIPD膜(インターポリ絶縁膜またはゲート間絶縁膜)を浮遊ゲート電極の上面だけでなく側面にも沿って這わせる事で制御ゲート電極の駆動力(カップリング比)を確保するEB(エッチバック)構造を有するため、加工難易度が高く、積層化が難しい。また、メモリセルの書込み/消去ウィンドウを広げるために、カップリング比をより高く設定する場合には、一つの方法として浮遊ゲート電極を厚くする必要があるが、このEB構造では、浮遊ゲート電極の上にIPD膜と制御ゲート電極とをスタックした構造であるため、結果的にワードライン自身が高くなり、高アスペクト化するため、上記課題(d)が顕在化し、カップリング比の向上も容易ではない。

【0006】

そこで、このような加工難易度を極端に上げることなくカップリング比を確保するセル構造の一つとしてスタックゲート構造でなく、ワードライン方向に対して浮遊ゲート間にゲート間絶縁膜を介した制御ゲート電極を埋め込んで書き込み対象のセルの電位を両脇の制御ゲート電極で持ち上げることによりカップリング比を確保するという構造が提案されている。

【0007】

しかし、これらのメモリセルにおいて、単純な積層化は工程数の単純増加となるため、コスト増に見合うセル容量の増大を確保して、ビットコストを低減することが難しい。単純な積層化では、ビットコストシュリンク率=1/積層段数で段数の割り算でしか効かず、積層数を増やした場合のシュリンク率が小さく、ビットコストが高くなりやすい。このため、積層化によるシュリンクを目指すセル構造においては、工程数およびコストを低く抑える事が実用上の課題である。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2007−266143号公報

【特許文献2】特開2004−319948号公報

【特許文献3】特開2005−100501号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

本発明は、制御性の高い不揮発性半導体記憶装置およびその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0010】

実施形態に係る不揮発性半導体記憶装置は、第1の方向に直列接続された複数の第1のメモリセル、複数の第1のメモリセルとソース線との間に接続された第1のソース線側選択ゲートトランジスタ及び複数の第1のメモリセルとビット線との間に接続された第1のビット線側選択ゲートトランジスタを具備する第1のNANDセルユニットを有し、第1のメモリセルが、第1の半導体層と、第1の半導体層の上に形成された第1のゲート絶縁層と、第1のゲート絶縁層の上に形成された第1の浮遊ゲートとを有し、第1のソース線側選択ゲートトランジスタ及び第1のビット線側選択ゲートトランジスタが、第1の半導体層と、第1のゲート絶縁層と、第1のゲート絶縁層の上に形成された第1の選択ゲートとを有する第1のメモリセルアレイ層と、第1のメモリセルアレイ層の上に形成された第1の絶縁層と、第1の絶縁層の上に形成され、第1の方向に直列接続された複数の第2のメモリセル、複数の第2のメモリセルとソース線との間に接続された第2のソース線側選択ゲートトランジスタ及び複数の第2のメモリセルとビット線との間に接続された第2のビット線側選択ゲートトランジスタを具備する第2のNANDセルユニットを有し、第2のメモリセルが、第2の浮遊ゲートと、第2の浮遊ゲートの上に形成された第2のゲート絶縁層と、第2のゲート絶縁層の上に形成された第2の半導体層とを有し、第2のソース線側選択ゲートトランジスタ及び第2のビット線側選択ゲートトランジスタが、第2の半導体層と、第2のゲート絶縁層と、第2のゲート絶縁層の上に形成された第2の選択ゲートを有する第2のメモリセルアレイ層と、第1の絶縁層を介して上下に位置する第1及び第2の浮遊ゲートの第1の方向の両側面にゲート間絶縁層を介して形成され、第1の方向と直交する第2の方向に延びる制御ゲートと、第1の絶縁層を介して上下に位置する第1及び第2の選択ゲートの第1の方向の両側面にゲート間絶縁層を介して形成され、第2の方向に延び、第1及び第2の半導体層並びに第1及び第2のゲート絶縁層と共に補助トランジスタを形成する補助ゲートとを備える。

【図面の簡単な説明】

【0011】

【図1】第1の実施形態に係る不揮発性半導体記憶装置の全体構成を示すブロック図である。

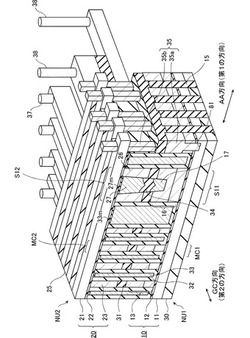

【図2】同不揮発性半導体記憶装置のメモリセルアレイ構造を示す斜視図である。

【図3】同メモリセルアレイの構造を示すGC方向の断面図である。

【図4】図2のA−A′,B−B′及びC−C′の切断断面図である。

【図5】同メモリセルアレイの等価回路図である。

【図6】同不揮発性半導体記憶装置の書き込み動作を示す概略図である。

【図7】同不揮発性半導体記憶装置の読み出し動作を示す概略図である。

【図8】同不揮発性半導体記憶装置の消去動作を示す概略図である。

【図9】同メモリセルアレイの製造工程を示す断面図である。

【図10】同メモリセルアレイの製造工程を示す断面図である。

【図11】同メモリセルアレイの製造工程を示す断面図である。

【図12】同メモリセルアレイの製造工程を示す断面図である。

【図13】同メモリセルアレイの製造工程を示す断面図である。

【図14】同メモリセルアレイの製造工程を示す断面図である。

【図15】同メモリセルアレイの製造工程を示す断面図である。

【図16】同メモリセルアレイの製造工程を示す断面図である。

【図17】同メモリセルアレイの製造工程を示す断面図である。

【図18】同メモリセルアレイの製造工程を示す断面図である。

【図19】同メモリセルアレイの製造工程を示す断面図である。

【図20】同メモリセルアレイの製造工程を示す断面図である。

【図21】同メモリセルアレイの製造工程を示す断面図である。

【図22】同メモリセルアレイの製造工程を示す断面図である。

【図23】同メモリセルアレイの製造工程を示す断面図である。

【図24】同メモリセルアレイの製造工程を示す断面図である。

【図25】同メモリセルアレイの製造工程を示す断面図である。

【図26】同メモリセルアレイの製造工程を示す断面図である。

【図27】同メモリセルアレイの製造工程を示す断面図である。

【図28】第2の実施形態に係る不揮発性半導体記憶装置の消去動作を示す概略図である。

【図29】比較例のNAND型フラッシュメモリのメモリセルアレイの構造を示す図である。

【図30】比較例のNAND型フラッシュメモリのメモリセルアレイの等価回路図である。

【発明を実施するための形態】

【0012】

以下、添付の図面を参照して実施の形態について説明する。

【0013】

[基本となるメモリセルアレイ構造]

まず、第1の実施形態の説明に先立ち、本実施形態に係る不揮発性半導体記憶装置の基本となるNAND型フラッシュメモリのメモリセル構造について説明する。

【0014】

本実施形態では、浮遊ゲートと制御ゲートのカップリングを確保するセル構造の一つとしてスタックゲート構造でなく、浮遊ゲートの両側面に制御ゲートを埋め込んで、浮遊ゲートとその両側の制御ゲートとをカップリングさせるゲート構造を有する。

【0015】

図29は、この構造を採用した比較例のNAND型フラッシュメモリのメモリセルアレイ1の構造を示す図、図30は同メモリセルアレイ1の等価回路図である。

【0016】

メモリセルアレイ50は、電気的書き換え可能なM個の不揮発性メモリセルMC0−MCM−1が直列接続されたNANDストリングと、このNANDストリングの両端に接続される選択ゲートトランジスタS1,S2を備えるNANDセルユニットNUが複数配列されている。NANDセルユニットNUの一端(選択ゲートトランジスタS1側)はビット線BLに、他端(選択ゲートトランジスタS2側)は共通ソース線CELSRCに接続される。選択ゲートトランジスタS1、S2のゲート電極は選択ゲート線SGD、SGSに接続される。また、メモリセルMC0〜MCM−1の両側に配置された制御ゲート電極はそれぞれワード線WL0〜WLMに接続されている。ビット線BLは、センスアンプ回路60に接続され、ワード線WL0〜WLM及び選択ゲート線SGD、SGSは、ロウデコーダ回路70に接続されている。

【0017】

基板に形成されたp型ウェル51にはメモリセルMCを構成するMOSFETのソース、ドレインとして機能するn型拡散層52が形成されている。またウェル51の上にはトンネル絶縁膜として機能するゲート絶縁膜53を介して浮遊ゲート(FG)54が形成され、この浮遊ゲート54の両側面にはゲート間絶縁層(IPD)55を介して制御ゲート(CG)56が形成されている。制御ゲート56は、ワード線WLを構成する。また、選択ゲートトランジスタS1、S2は、ウェル51の上にゲート絶縁層53を介して選択ゲート57を有している。選択ゲート57は、選択ゲート線SGS,SGDを構成する。メモリセルMCと選択ゲートトランジスタS1,S2とは、隣接するもの同士でドレインおよびソースを共有する形でNAND接続されている。

【0018】

1つのメモリセルMCに1ビットのデータが記憶される1ビット/セルの場合、NANDセルユニットNUに交差するワード線WLに沿って形成されるメモリセルMCに1ページのデータが記憶される。また、1つのメモリセルMCに2ビットのデータが記憶される2ビット/セルの場合、ワード線WLに沿って形成されるメモリセルMCに、2ページ(上位ページUPPER、下位ページLOWER)のデータが記憶される。

【0019】

1つのブロックBLKは、ワード線WLを共有する複数のNANDセルユニットNUを含む。1つのブロックBLKは、データ消去動作の一単位を形成する。1つのメモリセルアレイ1において1つのブロックBLK中のワード線WLの数は、M+1本であり、1ブロック中のページ数は、2ビット/セルの場合、M×2=128ページとなる。

【0020】

書き込み対象のメモリセルMCにデータを書き込む場合には、浮遊ゲート54の両側の制御ゲート56の電圧を所定の書き込み電圧まで引き上げ、その両側から両端までの制御ゲート56が交互に低電圧及び高電圧となるように順次電圧値を低くしていくことにより、非選択メモリセルに誤書き込みが生じるのを防止する。

【0021】

[第1の実施形態]

[全体構成]

図1は、本発明の第1の実施の形態に係る不揮発性半導体記憶装置のブロック図である。

【0022】

この不揮発性半導体記憶装置は、複数のメモリセルMCがNAND接続されたNANDストリングを複数備えたメモリセルアレイ1を備える。

【0023】

メモリセルアレイ1のビット線BL方向に隣接する位置には、メモリセルアレイ1のビット線BLを制御し、メモリセルのデータ消去、メモリセルへのデータ書き込み、及びメモリセルからのデータ読み出しを行うカラム制御回路2が設けられている。

【0024】

また、メモリセルアレイ1のワード線WL方向に隣接する位置には、メモリセルアレイ1のワード線WLを選択し、メモリセルのデータ消去、メモリセルへのデータ書き込み、及びメモリセルからのデータ読み出しに必要な電圧を印加するロウ制御回路3が設けられている。

【0025】

データ入出力バッファ4は、外部のホスト9にI/O線を介して接続され、書き込みデータの受け取り、消去命令の受け取り、読み出しデータの出力、アドレスデータやコマンドデータの受け取りを行う。データ入出力バッファ4は、受け取った書き込みデータをカラム制御回路2に送り、カラム制御回路2から読み出したデータを受け取って外部に出力する。外部からデータ入出力バッファ4に供給されたアドレスは、アドレスレジスタ5を介してカラム制御回路2及びロウ制御回路3に送られる。

【0026】

また、ホスト9からデータ入出力バッファ4に供給されたコマンドは、コマンド・インターフェイス6に送られる。コマンド・インターフェイス6は、ホスト9からの外部制御信号を受け、データ入出力バッファ4に入力されたデータが書き込みデータかコマンドかアドレスかを判断し、コマンドであれば受け取りコマンド信号としてステートマシン7に転送する。

【0027】

ステートマシン7は、この不揮発性メモリ全体の管理を行うもので、ホスト9からのコマンドをコマンド・インターフェイス6を介して受け付け、読み出し、書き込み、消去、データの入出力管理等を行う。

【0028】

また、外部のホスト9は、ステートマシン7が管理するステータス情報を受け取り、動作結果を判断することも可能である。また、このステータス情報は書き込み、消去の制御にも利用される。

【0029】

また、ステートマシン7によって電圧生成回路10が制御される。この制御により、電圧生成回路10は任意の電圧、任意のタイミングのパルスを出力することが可能となる。

【0030】

ここで、形成されたパルスはカラム制御回路2及びロウ制御回路3で選択された任意の配線へ転送することが可能である。

【0031】

[メモリセルアレイの構造]

次に、第1の実施形態に係るメモリセルアレイ構造について説明する。

【0032】

図2は、第1の実施形態に係るメモリセルアレイ構造の斜視図、図3は図1のGC(ゲート)方向から見た断面図、図4は図3のA−A′,B−B′及びC−C′の各線で切断し、図2のAA(アクティブエリア)方向から見た断面図である。なお、内部構造を視認可能とするために、一部構成を省略して図示している。

【0033】

このメモリセルアレイ構造は、図29及び図30に示したメモリセルアレイ構造を上下反転させて積層すると共に、上下のメモリセルアレイ層で制御ゲートを共有するようにしたものである。

【0034】

すなわち、図2に示すように、絶縁体のベース30の上に、チャネルを形成するボディとなる第1の半導体層11及び第2の半導体層21が上下に配置され、その間に第1のゲート絶縁層12を介して第1の半導体層11の上面に対向する第1の浮遊ゲート13と第2のゲート絶縁層22を介して第2の半導体層21の下面に対向する第2の浮遊ゲート23が第1の絶縁層31を介して上下に積層されている。これら半導体層11,21、ゲート絶縁層12,22及び浮遊ゲート13,23は、図3(a)のA−A′断面からも明らかなように、AA方向(第1の方向)に延びる層間絶縁層15,25を介してGC方向(第2の方向)に互いに絶縁分離されている。

【0035】

浮遊ゲート13,23の積層構造体は、NAND配列を形成するように、半導体層11,21に沿ってAA方向に所定間隔で複数形成されている。各浮遊ゲート13,23の積層体のAA方向の両側には、ゲート間絶縁層(IPD:インターポリ絶縁層)32を介してGC方向に延びる制御ゲート33が形成されている。制御ゲート33は、上下の浮遊ゲート13,23に側面からカップリングするように、これら浮遊ゲート13,23に共通に設けられている。制御ゲート33と第2のゲート絶縁層22との間には、マスク材33mが設けられている。そして、下側の第1の半導体層11、第1のゲート絶縁層12、第1の浮遊ゲート13、ゲート間絶縁層32及び制御ゲート33が、下側の第1のメモリセルMC1の構成に含まれる。また、上側の第2の半導体層21、第2のゲート絶縁層22、第2の浮遊ゲート23、ゲート間絶縁層32及び制御ゲート33が、上側の第2のメモリセルMC2の構成に含まれる。

【0036】

浮遊ゲート13,23の積層構造体の配列方向の両端の制御ゲート33に隣接する位置には、選択ゲートトランジスタS11,S12,S21,S22(図3)を形成する第1の選択ゲート16及び第2の選択ゲート26が配置されている。これら選択ゲート16,26は、第1の絶縁層31を介して上下に積層され、それぞれゲート絶縁層12,22を介して半導体層11,21に対向している。第1の選択ゲート16にはGC方向に延びる第1の選択ゲート線17が埋め込まれ、第2の選択ゲート26にはGC方向に延びる第2の選択ゲート線27とマスク材27mとが埋め込まれている。これら選択ゲート線17,27は、層間絶縁層34を介して互いに絶縁分離されている。

【0037】

そして、下側の第1のNANDセルユニットNU1には下側のNAND接続されたメモリセルMC1と選択ゲートトランジスタS11,S21を含み、第1のメモリセルアレイ層10は第1の素子分離絶縁層15を介してGC方向に配列された複数のNANDセルユニットNU1を含む。また、上側の第2のNANDセルユニットNU2には上側のNAND接続されたメモリセルMC2と選択ゲートトランジスタS12,S22を含み、第2のメモリセルアレイ層20にはGC方向に配列された複数のNANDセルユニットNU2を含む。

【0038】

以上の構成によれば、図5に等価回路を示すように、上下のNANDセルユニットNU1,NU2の上下に対応するメモリセルMC1,MC2の浮遊ゲート13,23は、両側のワード線WLとのカップリングによって同時に駆動され、共通のビット線BLと接続される。これに対し、選択ゲートトランジスタS11〜S22は、上下のビット線BLに対してそれぞれ独立して設けられ、いずれか一方が選択状態にされることにより、NANDセルユニットNU1,NU2を選択的にアクティブにすることができる。

【0039】

[補助トランジスタ]

図3に示す通り、本実施形態に係る不揮発性半導体記憶装置は、ソース線コンタクト36とソース線側選択ゲートトランジスタS21,S22との間に第1の補助ゲート91eを有しており、第1の半導体層11との間に第1の下部補助トランジスタ91aを、第2の半導体層21との間に第1の上部補助トランジスタ91bを形成する。同様に、ソース線側選択ゲートトランジスタS21,S22と、第1、第2の浮遊ゲート13、23との間に第2の補助ゲート92eを、第1、第2の浮遊ゲート13、23とビット線側選択ゲートトランジスタS11,S12との間に第3の補助ゲート93eを、ビット線側選択ゲートトランジスタS11,S12とビット線コンタクト35との間に第4の補助ゲート94eをそれぞれ有している。第1の半導体層11及び第2の半導体層21との間に第2の下部補助トランジスタ92aと第2の上部補助トランジスタ92b、第3の下部補助トランジスタ93aと第3の上部補助トランジスタ93b、及び第4の下部補助トランジスタ94a及び第4の上部補助トランジスタ94bを形成する。

【0040】

[コンタクト]

NANDセルユニットNU1,NU2の一端の半導体層11,21には、これらに共通の上下に延びて図示しないビット線BLにつながるビット線コンタクト35が形成されている。また、NANDセルユニットNU1,NU2の他端の半導体層11,21には、これらに共通の上下に延びて図示しないソース線につながるソース線コンタクト36が形成されている。更に、制御ゲート33の端部にはワード線コンタクト37(図2)が形成され、選択ゲート線17,27の端部には選択ゲート線コンタクト38(図2)が接続されている。

【0041】

ビット線コンタクト35は下部コンタクト35a及び上部コンタクト35bを備える。下部コンタクト35aは、第1のゲート絶縁層12に設けられた第1の溝81を介して第1の半導体層11に接続されている。本実施形態における下部コンタクト35aは、後述のとおり第1の浮遊ゲート13と同時に形成される。従って、下部コンタクト35aと第1の半導体層11のGC方向における幅は略一致している。又、下部コンタクト35aは第1の浮遊ゲート13と同一の素材から形成されており、第1の素子分離絶縁層15を介して第1の半導体層11と同一の間隔で同一直線状に形成されている。又、上部コンタクト35bは、第2の半導体層21、第2のゲート絶縁層22、第1の絶縁層31を介して下部コンタクト35aの上部に形成された、第2の浮遊ゲート23と同一の素材により形成されている上部コンタクト層、第1の絶縁層31及び下部コンタクト35aの上部を貫通する様に設けられたビアホールを介して埋め込まれている。

【0042】

[動作方法]

次に、本実施形態に係る不揮発性半導体記憶装置の動作方法について説明する。チャネル(ボディ)、浮遊ゲート、ビット線やソース線等の電極のうち、ある電極(第1の電極)が第1の電位、他の電極(第2の電極)が第1の電位と異なる第2の電位である時、第1の電極と第2の電極の間に生じた電位差が一定値を超えると、GIDL(Gate Induced Drain Leadage)やSCE等の誤動作が生じる事がある。この様な問題は、上記電極間に設けられた絶縁膜の薄膜化に伴って顕著に発生する様になる。

【0043】

本実施形態に係る不揮発性半導体記憶装置は、第1〜第4の補助ゲート91e〜94eのうち、第1の電極及び第2の電極に絶縁層を介して隣接するもの(第3の電極)に第1の電極と第2の電極との間に生じた電位差を緩和させる第3の電圧を印加する。この第3の電圧の印加によって、GIDLやSCE等の誤動作を抑制することが可能となる。尚、第3の電圧は、第1の電圧値と第2の電圧値との間の値に設定することが考えられる。

【0044】

[書き込み動作]

図6は、本実施形態に係る不揮発性半導体記憶装置の書き込み動作について説明する為の概略図である。以下、書き込み動作の対象となる選択メモリセルMCselectを含む選択NANDセルユニットをNU12、第1の絶縁層31を介してNANDセルユニットNU12と接続される非選択NANDセルユニットをNU11、NANDセルユニットNU11及びNU12と素子分離絶縁膜15及び25(図4)を介してGC方向に隣接し、同一のソース線SLに接続されている非選択NANDセルユニットを、それぞれNU21及びNU22とする。

【0045】

書き込み動作に際しては、まず、選択NANDセルユニットNU12に接続されている選択ビット線BL1に選択ビット線電圧VBL_select(例えば0V)を、非選択ビット線BL2に非選択ビット線電圧VBL_inhibit(例えばVdd)を印加する。又、ソース線SLにはソース線電圧VSL_write(例えば0V)を印加する。

【0046】

又、第4の上部補助トランジスタ94b、ビット線側選択ゲートトランジスタS12及び第3の上部補助トランジスタ93bを導通状態とし、ソース線側選択ゲートトランジスタS22をカットオフ状態とする。これによって、選択NANDセルユニットのチャネル(ボディ)として動作する第2の半導体層21に選択ビット線電圧VBL_selectを転送する。更に、選択メモリセルMCselectの第2の浮遊ゲート23にAA方向の両側から隣接する一対の制御ゲート33に書き込み電圧Vpgmを印加して選択メモリセルMCselectの浮遊ゲート23の電位を上昇させ、浮遊ゲート23と第2の半導体層21との電位差によって書き込み動作を行う。

【0047】

上記書き込み動作において、制御ゲートと容量結合している非選択NANDセルユニットNU11、NU21及びNU22のチャネル(ボディ)電位と、ソース線側選択ゲートトランジスタS21及びS22のゲート(選択ゲート線17及び27)に印加される電圧VSG_OFF_pgmとの差が所定の電圧値を超えると、非選択NANDセルユニットNU11、NU21及びNU22のソース線側選択ゲートトランジスタのチャネル(ボディ)においてGIDLを生じ、誤動作の原因となる事がある。そこで、本実施形態においては、更に第2の補助ゲート92eに、選択NANDセルユニットをNU12の選択ゲートトランジスタのゲートに印加される電圧VSG_ON_pgmと電圧VSG_OFF_pgmとの間の電圧VGate_2を印加することによってと非選択NANDセルユニットNU11、NU21及びNU22のボディ電位電圧VSG_OFF_pgmとの電位差を緩和し、上記問題を回避している。

【0048】

又、本実施形態においては、第1の上部補助トランジスタ91b、ビット線コンタクト35を介して選択NANDセルユニットNU12にAA方向から隣接するNANDセルユニットの第4の上部補助トランジスタ94b´及びソース線コンタクト36を介して選択NANDセルユニットNU12にAA方向から隣接するNANDセルユニットの第1の上部補助トランジスタ91b´をカットオフ状態とするための電位を補助ゲート91e、94e’及び91’に与えて、SCEの発生を防いでいる。

【0049】

[読出し動作]

図7は、本実施形態に係る不揮発性半導体記憶装置の読み出し動作について説明する為の概略図である。尚、図7においては、NANDセルユニットNU12及びNU22に対して読み出し動作を行う例について説明する。

【0050】

読出し動作に際しては、まず、選択ビット線BL1及びBL2に読出し電圧VBL_readを印加し、ソース線SLにソース線電圧VSL_readを印加する。又、第4の上部補助トランジスタ94b、ビット線側選択ゲートトランジスタS12、第3の上部補助トランジスタ93b、第2の上部補助トランジスタ92b、ソース線側選択ゲートトランジスタS22及び第1の上部補助トランジスタ91bを導通状態とする。更に、浮遊ゲート23にAA方向の両側から隣接する一対の制御ゲート33に読出し電圧Vreadを、それ以外の制御ゲートにはメモリセルMCが導通状態となる電圧Vpassを印加して読出し動作を行う。

【0051】

上記読み出し動作においては、ビット線BL1及びBL2に印加された読み出し電圧VBL_readと、ビット線コンタクト35を介して選択NANDセルユニットNU12にAA方向から隣接するNANDセルユニットのビット線側選択ソース線27´に印加された電圧VSG_OFF_readとの差が所定の電圧値を超えると、ビット線側選択ゲートトランジスタS12´においてGIDLを生じ、誤動作の原因となる事がある。そこで、本実施形態においては、更に第4の補助ゲート94´eに、読み出し電圧VBL_readと電圧VSG_OFF_readとの間の電圧VGate_1´を印加することによって読み出し電圧VBL_readと電圧VSG_OFF_readとの電位差を緩和し、上記問題を回避している。

【0052】

又、本実施形態においては、第1の上部補助トランジスタ91b´をカットオフ状態とし、SCEの発生を防いでいる。

【0053】

[消去動作]

図8は、本実施形態に係る不揮発性半導体記憶装置の消去動作について説明する為の概略図である。尚、図8においては、NANDセルユニットNU12及びNU22に対して消去動作を行う例について説明する。

【0054】

消去動作に際しては、まず、図示しないシリコン基板に設けられたp型半導体層に消去電圧Veraseを与える。ビット線コンタクト35及びソース線コンタクト36は浮遊ゲート13及び23と同様にn型半導体を用いて構成されている為、オープン状態のビット線BL1及びBL2は電圧VBL_eraseまで充電される。又、ワード線(制御ゲート線33)には電圧VWLを印加し、第2のビット線側選択ゲート線27はフローティング状態とする。

【0055】

又、第4の補助ゲート94eに消去電圧VBL_eraseよりも低い電位VGate_4を印加してGIDLを発生させ、GIDLによって発生した正孔(ホール)h+によって第2の半導体層21の電位を上昇させる。半導体層21の電位が一定以上上昇すると、各制御ゲート線33と容量結合した各浮遊ゲート23から電子が引き抜かれ、消去動作が完了する。

【0056】

上記消去動作においては、第2のビット線側選択ゲート線27の電位が第4の補助ゲート94eとの容量結合によって引き下げられるが、第2の半導体層21との電位差が所定の値を超えると、第1のビット線側選択ゲート線17と第2の半導体層21との間で絶縁破壊を生じる恐れがある。そこで、本実施形態においては第3の上部補助ゲート93eに電位VGate_3を印加して第2のビット線側選択ゲート線27の電位を引き上げることによって第2の半導体層21との電位差を緩和し、上記問題を回避している。

【0057】

[メモリセルアレイ構造の製造方法]

次に、本実施形態のメモリセルアレイ構造の製造方法について説明する。

【0058】

まず、周辺回路領域の形成は、幾つかのバリエーションが考えられるが、バルクのシリコン基板上に作り込む場合、周辺回路を先に形成する必要がある。この際、同時にバルクのシリコン基板上に本実施形態のメモリセルアレイを同時形成しても良い。本実施の形態は、立体的にNANDセルユニットNU1、NU2を設けているため、シリコン基板上にNANDセルユニットNU1、NU2が形成される例について説明する。周辺回路トランジスタの形成方法は、一般的な方法と同一である。すなわち、まず、シリコン基板上にチャネル形成、ゲート酸化膜(Low Voltage酸化膜とHigh Voltage酸化膜の両者)を形成、ゲート電極およびAA(アクティブエリア)加工マスク材を積層した後、STI溝を形成する。次にSTI溝を埋め込んだ後、GC(ゲート)加工マスク材を積層し、GC電極加工、サイドウォール絶縁膜の形成を行った後、ソース・ドレイン拡散層を形成、GC間絶縁膜を埋め込み、平坦化する。

【0059】

周辺回路形成した後、この上層に本実施形態のメモリセルアレイを作り込む。図9〜図27は、本実施形態に係るメモリセルアレイの形成方法を示す図である。

【0060】

まず、図9に示すように、図示しないシリコン基板上にSiO2を用いた絶縁層30Aを形成し、その上にポリシリコンを用いた第1の半導体層11A、SiO2を用いた第1のゲート絶縁層12A、ポリシリコンを用いた第1のゲート形成層13aAを順次積層する。チャネル(ボディ)となる第1の半導体層11Aは、基本的にはポリシリコンを用いて形成しているが、単結晶シリコンを用いても良い。本実施形態ではチャネル(ボディ)にポリシリコンを用い、SOI構造とすることにより、シリコン基板にSTIを形成する必要が無く、より積層化に向いたセル構造とすることが可能である。ゲート絶縁層12Aの形成は、ポリシリコンを用いた半導体層11A上のため、熱酸化膜ではなく、CVD(Chemical Vapor Deposition)やALD(atomic layer deposition)酸化膜を用いる。なお、第1の半導体層11Aは、上記のように成膜で形成しているが、シリコン基板をそのまま利用しても良い。

【0061】

次に、図10に示す通り、第1のゲート形成層13aA、第1のゲート絶縁層12A及び第1の半導体層11A表面に、GC方向に延びる第1の溝81を設ける。次に、図11に示す通り、第1の浮遊ゲート形成層13aA及び第1の半導体層11A表面のうち、第1の溝81によって露出した部分に第2のゲート形成層13bAを形成する。

【0062】

第2のゲート形成層13bAまで形成した後は、図12に示す通り、その上にAAパターン加工用の例えばSiN、SiO2を用いたマスク材41,42をパターン形成する。次に、図13に示す通りマスク材41,42を用いたRIE(Reactive Ion Etching)によって、積層体を絶縁層30Aの下まで選択的にエッチングして第2の溝を設け、AAパターンを加工する。これにより、浮遊ゲート形成層13B、第1のゲート絶縁層12、第1の半導体層11及び絶縁層30が形成される。

【0063】

次に、図14に示すように、AAパターン加工により形成された溝にSiO2を用いた第1の素子分離絶縁層15を埋め、第1のゲート形成層13Bを形成するポリシリコンをストッパとしてCMP(Chemical Mechanical Polishing)による平坦化を行い、更にエッチバックによって第1の素子分離絶縁層15の上面を後退させる。次に、図15に示すように、第1の素子分離絶縁層15及び第1のゲート形成層13Bの上に上層と下層とを分離する第1の絶縁層31を形成し、その上にポリシリコンを用いた第3のゲート成形層23Aを形成する。

【0064】

続いて、図16に示すように、第3のゲート形成層23Aの上に、GCパターン加工用の例えばSiN、SiO2を用いたマスク材43,44をパターン形成する。そして、図17に示すように、マスク材43,44を用いたRIEによって、積層体をゲート絶縁層12の上まで選択的にエッチングして第3の溝を形成し、GCパターンを形成する。これにより、第1の浮遊ゲート13、第3のゲート形成層23B、第1の選択ゲート形成層16A、第2の選択ゲート形成層26A、下部コンタクト35a及び36aが形成される。このGCパターン加工は、下層のゲート絶縁層12と高い選択比を有するエッチングにより行い、下層の半導体層11をエッチングしないようにする事が望ましい。

【0065】

続いて、図18に示すように、SiO2を用いたゲート間絶縁層(IPD)32を成膜したのち、GCパターン間に制御ゲート形成層33Aを埋め込む。制御ゲート形成層33Aとしては、ポリシリコン又はメタル(Wなど)、メタルシリサイド(WSiなど)を用いることができる。

【0066】

次に、図19に示すように、制御ゲート形成層33Aに対し、RIEにてエッチバックを行うことで、制御ゲート33及び補助ゲート91e〜94eを形成する。その上に図20に示すように、CVD酸化膜や塗布酸化膜などを用いたマスク材33mを埋め込み、SiNを用いたマスク43をストッパとしてCMPにて上面を平坦化する。さらにその後、選択ゲート形成層16A,26Aや図示しないロウデコーダ部のトランジスタを形成するため、EI(Etching Inter Poly)溝に相当する選択ゲート溝加工をRIEなどにより行い、図21に示すように、第2の選択ゲート形成層26B、第1の絶縁層31及び第1の選択ゲート16に至る第4の溝17Aを形成する。

【0067】

次に、上層セル、下層セルのそれぞれに独立した選択ゲートトランジスタS11〜S22を形成するために、図22に示すように、選択ゲート溝17Aに第1の選択ゲート線17、層間絶縁層34及び第2の選択ゲート線27を、埋め込みとエッチバックとを繰り返しながら順次形成していく。選択ゲート線17,27としては、制御ゲート33及び補助ゲート91e〜94eと同様、ポリシリコン又はメタル(Wなど)、メタルシリサイド(WSiなど)を用いることができる。第2の選択ゲート線27の上のエッチバックされた部分には、キャップ絶縁層27mが埋め込まれ、その上面はマスク材43をストッパとするCMPにより平坦化される。図23(a),(b),(c)は、図22のそれぞれA−A′断面、B−B′断面、C−C′断面である。

【0068】

次に、図24に示すように、第3のゲート形成層23BをストッパとしてCMPによる平坦化を実施し、その上にSiO2を用いた第2のゲート絶縁層22A、ポリシリコンを用いた第2の半導体層21Aを順次成膜する。尚、CMPは、制御ゲート33をストッパとして行っても良い。図25(a),(b),(c)は、図24のそれぞれA−A′断面、B−B′断面、C−C′断面である。

【0069】

続いて、図26に示すように、上層の第2の半導体層21A、第2のゲート絶縁層22A、第3のゲート形成層23B及び第2の選択ゲート形成層26Bに対してAAパターン加工を行うため、第2の半導体層21Aの上にAAパターン加工用のSiNを用いたマスク材45をパターン形成し、RIEにてAAパターン加工を行う。図27(a),(b),(c)は、図26のそれぞれA−A′断面、B−B′断面、C−C′断面である。以上の工程で、第2の浮遊ゲート23が形成されると共に、この第2の浮遊ゲート23に対して第2のゲート絶縁層22及び第2の半導体層21が自己整合的に形成される。

【0070】

次に、上層のAAパターンの溝に第2の素子分離絶縁層25(図1、図3)を埋め込む。最後に、第2の半導体層、第2のゲート絶縁層、上部コンタクト層、第1の絶縁層及び前記下部コンタクトにビアホールを形成し、形成したビアホールに上部コンタクトを埋め込む。ビアコンタクト形成の際には、ビアホールは第1の絶縁層を貫通し、下部のコンタクトの上面が露出する様に設ける。

【0071】

本実施形態のように、制御ゲート線33を形成する工程と共通する工程を用いて、補助ゲート91e及び94eを形成することができ、製造工程数の削減を図ることが可能となる。

【0072】

[第2の実施形態]

次に、第2の実施形態に係る不揮発性半導体記憶装置の消去動作について説明する。図28は、本実施形態に係る不揮発性半導体記憶装置の消去動作を説明する為の概略図である。本実施形態に係る不揮発性半導体記憶装置の消去動作は、基本的には第1の実施形態と同様であるが、以下の点において異なっている。即ち、本実施形態においては、第4の上部補助トランジスタ94bを導通状態とし、第2のビット線側選択ゲート線27に消去電圧VBL_eraseよりも低い電圧VSG_eraseを印加してGIDLを発生させ、GIDLによって発生した正孔(ホール)h+によって第2の半導体層21の電位を上昇させる。尚、電圧VSG_eraseは、第2の選択ゲート線27−第2の半導体層21間及び第2の選択ゲート線27−第1の選択ゲート線17において絶縁破壊が生じないような値に設定する。

[その他の実施形態]

以上、本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これらの新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0073】

10…第1のメモリセルアレイ層、11…第1の半導体層、12…第1のゲート絶縁層、13…第1の浮遊ゲート、15…第1の素子分離絶縁層、16…第1の選択ゲート、17…第1の選択ゲート線、20…第2のメモリセルアレイ層、21…第2の半導体層、22…第2のゲート絶縁層、23…第2の浮遊ゲート、25…第2の素子分離絶縁層、26…第2の選択ゲート、27…第2の選択ゲート線、31…第1の絶縁層、32…ゲート間絶縁層、33…制御ゲート、34…第2の絶縁層、35…ビット線コンタクト、36…ソース線コンタクト、37…ワード線コンタクト、38…選択ゲート線コンタクト、91e…第1の補助ゲート、92e…第2の補助ゲート、93e…第3の補助ゲート、94e…第4の補助ゲート、91a…第1の下部補助トランジスタ、92a…第2の下部補助トランジスタ、93a…第3の下部補助トランジスタ、94a…第4の下部補助トランジスタ、91b…第1の上部補助トランジスタ、92b…第2の上部補助トランジスタ、93b…第3の上部補助トランジスタ、94b…第4の上部補助トランジスタ。

【技術分野】

【0001】

本明細書記載の技術は、不揮発性半導体記憶装置及びその製造方法に関する。

【背景技術】

【0002】

電気的に書き換え可能で且つ高集積化が可能な不揮発性半導体記憶装置として、NAND型フラッシュメモリが知られている。従来のNAND型フラッシュメモリのメモリトランジスタは絶縁膜を介して電荷蓄積層(浮遊ゲート)と制御ゲートが積層されたスタックゲート構造をしている。複数個のメモリトランジスタを、隣接するもの同士でソース若しくはドレインを共有するような形で列方向に直列接続させ、その両端に選択ゲートトランジスタを配置して、NANDセルユニットが構成される。NANDセルユニットの一端はビット線に接続され、他端はソース線に接続される。NANDセルユニットをマトリクス状に配置することにより、メモリセルアレイが構成される。また、行方向に並ぶNANDセルユニットをNANDセルブロックと呼ぶ。同一行に並ぶ選択ゲートトランジスタのゲートは、同一の選択ゲート線に接続され、同一行に並ぶメモリトランジスタの制御ゲートは、同一のワード線に接続される。NANDセルユニット内にN個のメモリトランジスタが直列接続されている場合、1つのNANDセルブロック内に含まれるワード線はN本となる。

【0003】

このようなNAND型フラッシュメモリにおいては、微細化に伴うゲート長縮小と隣接トランジスタ間隔が狭まることで、以下に述べる種々の課題が生じている。例えば、(a)近接ゲート間などの寄生容量の増大、ショートチャネル効果(SCE)などに起因した制御ゲートの電界によるドレイン電流制御性の低下、(b)隣接ゲート間干渉効果の増大、(c)隣接電極間リークの増大、(d)ゲート電極の高アスペクト化に起因したゲート加工時のパターンヨレ・倒壊、(e)電荷蓄積層に蓄積できる電子数(ビット当たりの電子数)の大幅減少に起因したデータリテンション特性の劣化、などの課題である。このため従来のNAND型フラッシュメモリでは、メモリセルの書込み/消去ウィンドウが大幅に低下し、微細化の物理限界に到達しつつある。

【0004】

今後の高集積化の方法の一手法として、メモリセルトランジスタを立体的に何層も積んでいく「3次元積層型」のメモリがある。具体的には、窒化膜トラップ型(SONOS、MONOS)セルを積層する構造が論文等で多く提案されているが、窒化膜トラップ型セル構造は、加工(積層化)が容易であるというメリットがあるものの、窒化膜に電子をトラップさせる特性上、消去特性とデータリテンション特性が浮遊ゲート型セルに比べて悪い事が大きな課題である。

【0005】

一方、従来の様な浮遊ゲート電極に電荷を蓄積する浮遊ゲート型メモリセル構造は、制御ゲート電極とIPD膜(インターポリ絶縁膜またはゲート間絶縁膜)を浮遊ゲート電極の上面だけでなく側面にも沿って這わせる事で制御ゲート電極の駆動力(カップリング比)を確保するEB(エッチバック)構造を有するため、加工難易度が高く、積層化が難しい。また、メモリセルの書込み/消去ウィンドウを広げるために、カップリング比をより高く設定する場合には、一つの方法として浮遊ゲート電極を厚くする必要があるが、このEB構造では、浮遊ゲート電極の上にIPD膜と制御ゲート電極とをスタックした構造であるため、結果的にワードライン自身が高くなり、高アスペクト化するため、上記課題(d)が顕在化し、カップリング比の向上も容易ではない。

【0006】

そこで、このような加工難易度を極端に上げることなくカップリング比を確保するセル構造の一つとしてスタックゲート構造でなく、ワードライン方向に対して浮遊ゲート間にゲート間絶縁膜を介した制御ゲート電極を埋め込んで書き込み対象のセルの電位を両脇の制御ゲート電極で持ち上げることによりカップリング比を確保するという構造が提案されている。

【0007】

しかし、これらのメモリセルにおいて、単純な積層化は工程数の単純増加となるため、コスト増に見合うセル容量の増大を確保して、ビットコストを低減することが難しい。単純な積層化では、ビットコストシュリンク率=1/積層段数で段数の割り算でしか効かず、積層数を増やした場合のシュリンク率が小さく、ビットコストが高くなりやすい。このため、積層化によるシュリンクを目指すセル構造においては、工程数およびコストを低く抑える事が実用上の課題である。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2007−266143号公報

【特許文献2】特開2004−319948号公報

【特許文献3】特開2005−100501号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

本発明は、制御性の高い不揮発性半導体記憶装置およびその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0010】

実施形態に係る不揮発性半導体記憶装置は、第1の方向に直列接続された複数の第1のメモリセル、複数の第1のメモリセルとソース線との間に接続された第1のソース線側選択ゲートトランジスタ及び複数の第1のメモリセルとビット線との間に接続された第1のビット線側選択ゲートトランジスタを具備する第1のNANDセルユニットを有し、第1のメモリセルが、第1の半導体層と、第1の半導体層の上に形成された第1のゲート絶縁層と、第1のゲート絶縁層の上に形成された第1の浮遊ゲートとを有し、第1のソース線側選択ゲートトランジスタ及び第1のビット線側選択ゲートトランジスタが、第1の半導体層と、第1のゲート絶縁層と、第1のゲート絶縁層の上に形成された第1の選択ゲートとを有する第1のメモリセルアレイ層と、第1のメモリセルアレイ層の上に形成された第1の絶縁層と、第1の絶縁層の上に形成され、第1の方向に直列接続された複数の第2のメモリセル、複数の第2のメモリセルとソース線との間に接続された第2のソース線側選択ゲートトランジスタ及び複数の第2のメモリセルとビット線との間に接続された第2のビット線側選択ゲートトランジスタを具備する第2のNANDセルユニットを有し、第2のメモリセルが、第2の浮遊ゲートと、第2の浮遊ゲートの上に形成された第2のゲート絶縁層と、第2のゲート絶縁層の上に形成された第2の半導体層とを有し、第2のソース線側選択ゲートトランジスタ及び第2のビット線側選択ゲートトランジスタが、第2の半導体層と、第2のゲート絶縁層と、第2のゲート絶縁層の上に形成された第2の選択ゲートを有する第2のメモリセルアレイ層と、第1の絶縁層を介して上下に位置する第1及び第2の浮遊ゲートの第1の方向の両側面にゲート間絶縁層を介して形成され、第1の方向と直交する第2の方向に延びる制御ゲートと、第1の絶縁層を介して上下に位置する第1及び第2の選択ゲートの第1の方向の両側面にゲート間絶縁層を介して形成され、第2の方向に延び、第1及び第2の半導体層並びに第1及び第2のゲート絶縁層と共に補助トランジスタを形成する補助ゲートとを備える。

【図面の簡単な説明】

【0011】

【図1】第1の実施形態に係る不揮発性半導体記憶装置の全体構成を示すブロック図である。

【図2】同不揮発性半導体記憶装置のメモリセルアレイ構造を示す斜視図である。

【図3】同メモリセルアレイの構造を示すGC方向の断面図である。

【図4】図2のA−A′,B−B′及びC−C′の切断断面図である。

【図5】同メモリセルアレイの等価回路図である。

【図6】同不揮発性半導体記憶装置の書き込み動作を示す概略図である。

【図7】同不揮発性半導体記憶装置の読み出し動作を示す概略図である。

【図8】同不揮発性半導体記憶装置の消去動作を示す概略図である。

【図9】同メモリセルアレイの製造工程を示す断面図である。

【図10】同メモリセルアレイの製造工程を示す断面図である。

【図11】同メモリセルアレイの製造工程を示す断面図である。

【図12】同メモリセルアレイの製造工程を示す断面図である。

【図13】同メモリセルアレイの製造工程を示す断面図である。

【図14】同メモリセルアレイの製造工程を示す断面図である。

【図15】同メモリセルアレイの製造工程を示す断面図である。

【図16】同メモリセルアレイの製造工程を示す断面図である。

【図17】同メモリセルアレイの製造工程を示す断面図である。

【図18】同メモリセルアレイの製造工程を示す断面図である。

【図19】同メモリセルアレイの製造工程を示す断面図である。

【図20】同メモリセルアレイの製造工程を示す断面図である。

【図21】同メモリセルアレイの製造工程を示す断面図である。

【図22】同メモリセルアレイの製造工程を示す断面図である。

【図23】同メモリセルアレイの製造工程を示す断面図である。

【図24】同メモリセルアレイの製造工程を示す断面図である。

【図25】同メモリセルアレイの製造工程を示す断面図である。

【図26】同メモリセルアレイの製造工程を示す断面図である。

【図27】同メモリセルアレイの製造工程を示す断面図である。

【図28】第2の実施形態に係る不揮発性半導体記憶装置の消去動作を示す概略図である。

【図29】比較例のNAND型フラッシュメモリのメモリセルアレイの構造を示す図である。

【図30】比較例のNAND型フラッシュメモリのメモリセルアレイの等価回路図である。

【発明を実施するための形態】

【0012】

以下、添付の図面を参照して実施の形態について説明する。

【0013】

[基本となるメモリセルアレイ構造]

まず、第1の実施形態の説明に先立ち、本実施形態に係る不揮発性半導体記憶装置の基本となるNAND型フラッシュメモリのメモリセル構造について説明する。

【0014】

本実施形態では、浮遊ゲートと制御ゲートのカップリングを確保するセル構造の一つとしてスタックゲート構造でなく、浮遊ゲートの両側面に制御ゲートを埋め込んで、浮遊ゲートとその両側の制御ゲートとをカップリングさせるゲート構造を有する。

【0015】

図29は、この構造を採用した比較例のNAND型フラッシュメモリのメモリセルアレイ1の構造を示す図、図30は同メモリセルアレイ1の等価回路図である。

【0016】

メモリセルアレイ50は、電気的書き換え可能なM個の不揮発性メモリセルMC0−MCM−1が直列接続されたNANDストリングと、このNANDストリングの両端に接続される選択ゲートトランジスタS1,S2を備えるNANDセルユニットNUが複数配列されている。NANDセルユニットNUの一端(選択ゲートトランジスタS1側)はビット線BLに、他端(選択ゲートトランジスタS2側)は共通ソース線CELSRCに接続される。選択ゲートトランジスタS1、S2のゲート電極は選択ゲート線SGD、SGSに接続される。また、メモリセルMC0〜MCM−1の両側に配置された制御ゲート電極はそれぞれワード線WL0〜WLMに接続されている。ビット線BLは、センスアンプ回路60に接続され、ワード線WL0〜WLM及び選択ゲート線SGD、SGSは、ロウデコーダ回路70に接続されている。

【0017】

基板に形成されたp型ウェル51にはメモリセルMCを構成するMOSFETのソース、ドレインとして機能するn型拡散層52が形成されている。またウェル51の上にはトンネル絶縁膜として機能するゲート絶縁膜53を介して浮遊ゲート(FG)54が形成され、この浮遊ゲート54の両側面にはゲート間絶縁層(IPD)55を介して制御ゲート(CG)56が形成されている。制御ゲート56は、ワード線WLを構成する。また、選択ゲートトランジスタS1、S2は、ウェル51の上にゲート絶縁層53を介して選択ゲート57を有している。選択ゲート57は、選択ゲート線SGS,SGDを構成する。メモリセルMCと選択ゲートトランジスタS1,S2とは、隣接するもの同士でドレインおよびソースを共有する形でNAND接続されている。

【0018】

1つのメモリセルMCに1ビットのデータが記憶される1ビット/セルの場合、NANDセルユニットNUに交差するワード線WLに沿って形成されるメモリセルMCに1ページのデータが記憶される。また、1つのメモリセルMCに2ビットのデータが記憶される2ビット/セルの場合、ワード線WLに沿って形成されるメモリセルMCに、2ページ(上位ページUPPER、下位ページLOWER)のデータが記憶される。

【0019】

1つのブロックBLKは、ワード線WLを共有する複数のNANDセルユニットNUを含む。1つのブロックBLKは、データ消去動作の一単位を形成する。1つのメモリセルアレイ1において1つのブロックBLK中のワード線WLの数は、M+1本であり、1ブロック中のページ数は、2ビット/セルの場合、M×2=128ページとなる。

【0020】

書き込み対象のメモリセルMCにデータを書き込む場合には、浮遊ゲート54の両側の制御ゲート56の電圧を所定の書き込み電圧まで引き上げ、その両側から両端までの制御ゲート56が交互に低電圧及び高電圧となるように順次電圧値を低くしていくことにより、非選択メモリセルに誤書き込みが生じるのを防止する。

【0021】

[第1の実施形態]

[全体構成]

図1は、本発明の第1の実施の形態に係る不揮発性半導体記憶装置のブロック図である。

【0022】

この不揮発性半導体記憶装置は、複数のメモリセルMCがNAND接続されたNANDストリングを複数備えたメモリセルアレイ1を備える。

【0023】

メモリセルアレイ1のビット線BL方向に隣接する位置には、メモリセルアレイ1のビット線BLを制御し、メモリセルのデータ消去、メモリセルへのデータ書き込み、及びメモリセルからのデータ読み出しを行うカラム制御回路2が設けられている。

【0024】

また、メモリセルアレイ1のワード線WL方向に隣接する位置には、メモリセルアレイ1のワード線WLを選択し、メモリセルのデータ消去、メモリセルへのデータ書き込み、及びメモリセルからのデータ読み出しに必要な電圧を印加するロウ制御回路3が設けられている。

【0025】

データ入出力バッファ4は、外部のホスト9にI/O線を介して接続され、書き込みデータの受け取り、消去命令の受け取り、読み出しデータの出力、アドレスデータやコマンドデータの受け取りを行う。データ入出力バッファ4は、受け取った書き込みデータをカラム制御回路2に送り、カラム制御回路2から読み出したデータを受け取って外部に出力する。外部からデータ入出力バッファ4に供給されたアドレスは、アドレスレジスタ5を介してカラム制御回路2及びロウ制御回路3に送られる。

【0026】

また、ホスト9からデータ入出力バッファ4に供給されたコマンドは、コマンド・インターフェイス6に送られる。コマンド・インターフェイス6は、ホスト9からの外部制御信号を受け、データ入出力バッファ4に入力されたデータが書き込みデータかコマンドかアドレスかを判断し、コマンドであれば受け取りコマンド信号としてステートマシン7に転送する。

【0027】

ステートマシン7は、この不揮発性メモリ全体の管理を行うもので、ホスト9からのコマンドをコマンド・インターフェイス6を介して受け付け、読み出し、書き込み、消去、データの入出力管理等を行う。

【0028】

また、外部のホスト9は、ステートマシン7が管理するステータス情報を受け取り、動作結果を判断することも可能である。また、このステータス情報は書き込み、消去の制御にも利用される。

【0029】

また、ステートマシン7によって電圧生成回路10が制御される。この制御により、電圧生成回路10は任意の電圧、任意のタイミングのパルスを出力することが可能となる。

【0030】

ここで、形成されたパルスはカラム制御回路2及びロウ制御回路3で選択された任意の配線へ転送することが可能である。

【0031】

[メモリセルアレイの構造]

次に、第1の実施形態に係るメモリセルアレイ構造について説明する。

【0032】

図2は、第1の実施形態に係るメモリセルアレイ構造の斜視図、図3は図1のGC(ゲート)方向から見た断面図、図4は図3のA−A′,B−B′及びC−C′の各線で切断し、図2のAA(アクティブエリア)方向から見た断面図である。なお、内部構造を視認可能とするために、一部構成を省略して図示している。

【0033】

このメモリセルアレイ構造は、図29及び図30に示したメモリセルアレイ構造を上下反転させて積層すると共に、上下のメモリセルアレイ層で制御ゲートを共有するようにしたものである。

【0034】

すなわち、図2に示すように、絶縁体のベース30の上に、チャネルを形成するボディとなる第1の半導体層11及び第2の半導体層21が上下に配置され、その間に第1のゲート絶縁層12を介して第1の半導体層11の上面に対向する第1の浮遊ゲート13と第2のゲート絶縁層22を介して第2の半導体層21の下面に対向する第2の浮遊ゲート23が第1の絶縁層31を介して上下に積層されている。これら半導体層11,21、ゲート絶縁層12,22及び浮遊ゲート13,23は、図3(a)のA−A′断面からも明らかなように、AA方向(第1の方向)に延びる層間絶縁層15,25を介してGC方向(第2の方向)に互いに絶縁分離されている。

【0035】

浮遊ゲート13,23の積層構造体は、NAND配列を形成するように、半導体層11,21に沿ってAA方向に所定間隔で複数形成されている。各浮遊ゲート13,23の積層体のAA方向の両側には、ゲート間絶縁層(IPD:インターポリ絶縁層)32を介してGC方向に延びる制御ゲート33が形成されている。制御ゲート33は、上下の浮遊ゲート13,23に側面からカップリングするように、これら浮遊ゲート13,23に共通に設けられている。制御ゲート33と第2のゲート絶縁層22との間には、マスク材33mが設けられている。そして、下側の第1の半導体層11、第1のゲート絶縁層12、第1の浮遊ゲート13、ゲート間絶縁層32及び制御ゲート33が、下側の第1のメモリセルMC1の構成に含まれる。また、上側の第2の半導体層21、第2のゲート絶縁層22、第2の浮遊ゲート23、ゲート間絶縁層32及び制御ゲート33が、上側の第2のメモリセルMC2の構成に含まれる。

【0036】

浮遊ゲート13,23の積層構造体の配列方向の両端の制御ゲート33に隣接する位置には、選択ゲートトランジスタS11,S12,S21,S22(図3)を形成する第1の選択ゲート16及び第2の選択ゲート26が配置されている。これら選択ゲート16,26は、第1の絶縁層31を介して上下に積層され、それぞれゲート絶縁層12,22を介して半導体層11,21に対向している。第1の選択ゲート16にはGC方向に延びる第1の選択ゲート線17が埋め込まれ、第2の選択ゲート26にはGC方向に延びる第2の選択ゲート線27とマスク材27mとが埋め込まれている。これら選択ゲート線17,27は、層間絶縁層34を介して互いに絶縁分離されている。

【0037】

そして、下側の第1のNANDセルユニットNU1には下側のNAND接続されたメモリセルMC1と選択ゲートトランジスタS11,S21を含み、第1のメモリセルアレイ層10は第1の素子分離絶縁層15を介してGC方向に配列された複数のNANDセルユニットNU1を含む。また、上側の第2のNANDセルユニットNU2には上側のNAND接続されたメモリセルMC2と選択ゲートトランジスタS12,S22を含み、第2のメモリセルアレイ層20にはGC方向に配列された複数のNANDセルユニットNU2を含む。

【0038】

以上の構成によれば、図5に等価回路を示すように、上下のNANDセルユニットNU1,NU2の上下に対応するメモリセルMC1,MC2の浮遊ゲート13,23は、両側のワード線WLとのカップリングによって同時に駆動され、共通のビット線BLと接続される。これに対し、選択ゲートトランジスタS11〜S22は、上下のビット線BLに対してそれぞれ独立して設けられ、いずれか一方が選択状態にされることにより、NANDセルユニットNU1,NU2を選択的にアクティブにすることができる。

【0039】

[補助トランジスタ]

図3に示す通り、本実施形態に係る不揮発性半導体記憶装置は、ソース線コンタクト36とソース線側選択ゲートトランジスタS21,S22との間に第1の補助ゲート91eを有しており、第1の半導体層11との間に第1の下部補助トランジスタ91aを、第2の半導体層21との間に第1の上部補助トランジスタ91bを形成する。同様に、ソース線側選択ゲートトランジスタS21,S22と、第1、第2の浮遊ゲート13、23との間に第2の補助ゲート92eを、第1、第2の浮遊ゲート13、23とビット線側選択ゲートトランジスタS11,S12との間に第3の補助ゲート93eを、ビット線側選択ゲートトランジスタS11,S12とビット線コンタクト35との間に第4の補助ゲート94eをそれぞれ有している。第1の半導体層11及び第2の半導体層21との間に第2の下部補助トランジスタ92aと第2の上部補助トランジスタ92b、第3の下部補助トランジスタ93aと第3の上部補助トランジスタ93b、及び第4の下部補助トランジスタ94a及び第4の上部補助トランジスタ94bを形成する。

【0040】

[コンタクト]

NANDセルユニットNU1,NU2の一端の半導体層11,21には、これらに共通の上下に延びて図示しないビット線BLにつながるビット線コンタクト35が形成されている。また、NANDセルユニットNU1,NU2の他端の半導体層11,21には、これらに共通の上下に延びて図示しないソース線につながるソース線コンタクト36が形成されている。更に、制御ゲート33の端部にはワード線コンタクト37(図2)が形成され、選択ゲート線17,27の端部には選択ゲート線コンタクト38(図2)が接続されている。

【0041】

ビット線コンタクト35は下部コンタクト35a及び上部コンタクト35bを備える。下部コンタクト35aは、第1のゲート絶縁層12に設けられた第1の溝81を介して第1の半導体層11に接続されている。本実施形態における下部コンタクト35aは、後述のとおり第1の浮遊ゲート13と同時に形成される。従って、下部コンタクト35aと第1の半導体層11のGC方向における幅は略一致している。又、下部コンタクト35aは第1の浮遊ゲート13と同一の素材から形成されており、第1の素子分離絶縁層15を介して第1の半導体層11と同一の間隔で同一直線状に形成されている。又、上部コンタクト35bは、第2の半導体層21、第2のゲート絶縁層22、第1の絶縁層31を介して下部コンタクト35aの上部に形成された、第2の浮遊ゲート23と同一の素材により形成されている上部コンタクト層、第1の絶縁層31及び下部コンタクト35aの上部を貫通する様に設けられたビアホールを介して埋め込まれている。

【0042】

[動作方法]

次に、本実施形態に係る不揮発性半導体記憶装置の動作方法について説明する。チャネル(ボディ)、浮遊ゲート、ビット線やソース線等の電極のうち、ある電極(第1の電極)が第1の電位、他の電極(第2の電極)が第1の電位と異なる第2の電位である時、第1の電極と第2の電極の間に生じた電位差が一定値を超えると、GIDL(Gate Induced Drain Leadage)やSCE等の誤動作が生じる事がある。この様な問題は、上記電極間に設けられた絶縁膜の薄膜化に伴って顕著に発生する様になる。

【0043】

本実施形態に係る不揮発性半導体記憶装置は、第1〜第4の補助ゲート91e〜94eのうち、第1の電極及び第2の電極に絶縁層を介して隣接するもの(第3の電極)に第1の電極と第2の電極との間に生じた電位差を緩和させる第3の電圧を印加する。この第3の電圧の印加によって、GIDLやSCE等の誤動作を抑制することが可能となる。尚、第3の電圧は、第1の電圧値と第2の電圧値との間の値に設定することが考えられる。

【0044】

[書き込み動作]

図6は、本実施形態に係る不揮発性半導体記憶装置の書き込み動作について説明する為の概略図である。以下、書き込み動作の対象となる選択メモリセルMCselectを含む選択NANDセルユニットをNU12、第1の絶縁層31を介してNANDセルユニットNU12と接続される非選択NANDセルユニットをNU11、NANDセルユニットNU11及びNU12と素子分離絶縁膜15及び25(図4)を介してGC方向に隣接し、同一のソース線SLに接続されている非選択NANDセルユニットを、それぞれNU21及びNU22とする。

【0045】

書き込み動作に際しては、まず、選択NANDセルユニットNU12に接続されている選択ビット線BL1に選択ビット線電圧VBL_select(例えば0V)を、非選択ビット線BL2に非選択ビット線電圧VBL_inhibit(例えばVdd)を印加する。又、ソース線SLにはソース線電圧VSL_write(例えば0V)を印加する。

【0046】

又、第4の上部補助トランジスタ94b、ビット線側選択ゲートトランジスタS12及び第3の上部補助トランジスタ93bを導通状態とし、ソース線側選択ゲートトランジスタS22をカットオフ状態とする。これによって、選択NANDセルユニットのチャネル(ボディ)として動作する第2の半導体層21に選択ビット線電圧VBL_selectを転送する。更に、選択メモリセルMCselectの第2の浮遊ゲート23にAA方向の両側から隣接する一対の制御ゲート33に書き込み電圧Vpgmを印加して選択メモリセルMCselectの浮遊ゲート23の電位を上昇させ、浮遊ゲート23と第2の半導体層21との電位差によって書き込み動作を行う。

【0047】

上記書き込み動作において、制御ゲートと容量結合している非選択NANDセルユニットNU11、NU21及びNU22のチャネル(ボディ)電位と、ソース線側選択ゲートトランジスタS21及びS22のゲート(選択ゲート線17及び27)に印加される電圧VSG_OFF_pgmとの差が所定の電圧値を超えると、非選択NANDセルユニットNU11、NU21及びNU22のソース線側選択ゲートトランジスタのチャネル(ボディ)においてGIDLを生じ、誤動作の原因となる事がある。そこで、本実施形態においては、更に第2の補助ゲート92eに、選択NANDセルユニットをNU12の選択ゲートトランジスタのゲートに印加される電圧VSG_ON_pgmと電圧VSG_OFF_pgmとの間の電圧VGate_2を印加することによってと非選択NANDセルユニットNU11、NU21及びNU22のボディ電位電圧VSG_OFF_pgmとの電位差を緩和し、上記問題を回避している。

【0048】

又、本実施形態においては、第1の上部補助トランジスタ91b、ビット線コンタクト35を介して選択NANDセルユニットNU12にAA方向から隣接するNANDセルユニットの第4の上部補助トランジスタ94b´及びソース線コンタクト36を介して選択NANDセルユニットNU12にAA方向から隣接するNANDセルユニットの第1の上部補助トランジスタ91b´をカットオフ状態とするための電位を補助ゲート91e、94e’及び91’に与えて、SCEの発生を防いでいる。

【0049】

[読出し動作]

図7は、本実施形態に係る不揮発性半導体記憶装置の読み出し動作について説明する為の概略図である。尚、図7においては、NANDセルユニットNU12及びNU22に対して読み出し動作を行う例について説明する。

【0050】

読出し動作に際しては、まず、選択ビット線BL1及びBL2に読出し電圧VBL_readを印加し、ソース線SLにソース線電圧VSL_readを印加する。又、第4の上部補助トランジスタ94b、ビット線側選択ゲートトランジスタS12、第3の上部補助トランジスタ93b、第2の上部補助トランジスタ92b、ソース線側選択ゲートトランジスタS22及び第1の上部補助トランジスタ91bを導通状態とする。更に、浮遊ゲート23にAA方向の両側から隣接する一対の制御ゲート33に読出し電圧Vreadを、それ以外の制御ゲートにはメモリセルMCが導通状態となる電圧Vpassを印加して読出し動作を行う。

【0051】

上記読み出し動作においては、ビット線BL1及びBL2に印加された読み出し電圧VBL_readと、ビット線コンタクト35を介して選択NANDセルユニットNU12にAA方向から隣接するNANDセルユニットのビット線側選択ソース線27´に印加された電圧VSG_OFF_readとの差が所定の電圧値を超えると、ビット線側選択ゲートトランジスタS12´においてGIDLを生じ、誤動作の原因となる事がある。そこで、本実施形態においては、更に第4の補助ゲート94´eに、読み出し電圧VBL_readと電圧VSG_OFF_readとの間の電圧VGate_1´を印加することによって読み出し電圧VBL_readと電圧VSG_OFF_readとの電位差を緩和し、上記問題を回避している。

【0052】

又、本実施形態においては、第1の上部補助トランジスタ91b´をカットオフ状態とし、SCEの発生を防いでいる。

【0053】

[消去動作]

図8は、本実施形態に係る不揮発性半導体記憶装置の消去動作について説明する為の概略図である。尚、図8においては、NANDセルユニットNU12及びNU22に対して消去動作を行う例について説明する。

【0054】

消去動作に際しては、まず、図示しないシリコン基板に設けられたp型半導体層に消去電圧Veraseを与える。ビット線コンタクト35及びソース線コンタクト36は浮遊ゲート13及び23と同様にn型半導体を用いて構成されている為、オープン状態のビット線BL1及びBL2は電圧VBL_eraseまで充電される。又、ワード線(制御ゲート線33)には電圧VWLを印加し、第2のビット線側選択ゲート線27はフローティング状態とする。

【0055】

又、第4の補助ゲート94eに消去電圧VBL_eraseよりも低い電位VGate_4を印加してGIDLを発生させ、GIDLによって発生した正孔(ホール)h+によって第2の半導体層21の電位を上昇させる。半導体層21の電位が一定以上上昇すると、各制御ゲート線33と容量結合した各浮遊ゲート23から電子が引き抜かれ、消去動作が完了する。

【0056】

上記消去動作においては、第2のビット線側選択ゲート線27の電位が第4の補助ゲート94eとの容量結合によって引き下げられるが、第2の半導体層21との電位差が所定の値を超えると、第1のビット線側選択ゲート線17と第2の半導体層21との間で絶縁破壊を生じる恐れがある。そこで、本実施形態においては第3の上部補助ゲート93eに電位VGate_3を印加して第2のビット線側選択ゲート線27の電位を引き上げることによって第2の半導体層21との電位差を緩和し、上記問題を回避している。

【0057】

[メモリセルアレイ構造の製造方法]

次に、本実施形態のメモリセルアレイ構造の製造方法について説明する。

【0058】

まず、周辺回路領域の形成は、幾つかのバリエーションが考えられるが、バルクのシリコン基板上に作り込む場合、周辺回路を先に形成する必要がある。この際、同時にバルクのシリコン基板上に本実施形態のメモリセルアレイを同時形成しても良い。本実施の形態は、立体的にNANDセルユニットNU1、NU2を設けているため、シリコン基板上にNANDセルユニットNU1、NU2が形成される例について説明する。周辺回路トランジスタの形成方法は、一般的な方法と同一である。すなわち、まず、シリコン基板上にチャネル形成、ゲート酸化膜(Low Voltage酸化膜とHigh Voltage酸化膜の両者)を形成、ゲート電極およびAA(アクティブエリア)加工マスク材を積層した後、STI溝を形成する。次にSTI溝を埋め込んだ後、GC(ゲート)加工マスク材を積層し、GC電極加工、サイドウォール絶縁膜の形成を行った後、ソース・ドレイン拡散層を形成、GC間絶縁膜を埋め込み、平坦化する。

【0059】

周辺回路形成した後、この上層に本実施形態のメモリセルアレイを作り込む。図9〜図27は、本実施形態に係るメモリセルアレイの形成方法を示す図である。

【0060】

まず、図9に示すように、図示しないシリコン基板上にSiO2を用いた絶縁層30Aを形成し、その上にポリシリコンを用いた第1の半導体層11A、SiO2を用いた第1のゲート絶縁層12A、ポリシリコンを用いた第1のゲート形成層13aAを順次積層する。チャネル(ボディ)となる第1の半導体層11Aは、基本的にはポリシリコンを用いて形成しているが、単結晶シリコンを用いても良い。本実施形態ではチャネル(ボディ)にポリシリコンを用い、SOI構造とすることにより、シリコン基板にSTIを形成する必要が無く、より積層化に向いたセル構造とすることが可能である。ゲート絶縁層12Aの形成は、ポリシリコンを用いた半導体層11A上のため、熱酸化膜ではなく、CVD(Chemical Vapor Deposition)やALD(atomic layer deposition)酸化膜を用いる。なお、第1の半導体層11Aは、上記のように成膜で形成しているが、シリコン基板をそのまま利用しても良い。

【0061】

次に、図10に示す通り、第1のゲート形成層13aA、第1のゲート絶縁層12A及び第1の半導体層11A表面に、GC方向に延びる第1の溝81を設ける。次に、図11に示す通り、第1の浮遊ゲート形成層13aA及び第1の半導体層11A表面のうち、第1の溝81によって露出した部分に第2のゲート形成層13bAを形成する。

【0062】

第2のゲート形成層13bAまで形成した後は、図12に示す通り、その上にAAパターン加工用の例えばSiN、SiO2を用いたマスク材41,42をパターン形成する。次に、図13に示す通りマスク材41,42を用いたRIE(Reactive Ion Etching)によって、積層体を絶縁層30Aの下まで選択的にエッチングして第2の溝を設け、AAパターンを加工する。これにより、浮遊ゲート形成層13B、第1のゲート絶縁層12、第1の半導体層11及び絶縁層30が形成される。

【0063】

次に、図14に示すように、AAパターン加工により形成された溝にSiO2を用いた第1の素子分離絶縁層15を埋め、第1のゲート形成層13Bを形成するポリシリコンをストッパとしてCMP(Chemical Mechanical Polishing)による平坦化を行い、更にエッチバックによって第1の素子分離絶縁層15の上面を後退させる。次に、図15に示すように、第1の素子分離絶縁層15及び第1のゲート形成層13Bの上に上層と下層とを分離する第1の絶縁層31を形成し、その上にポリシリコンを用いた第3のゲート成形層23Aを形成する。

【0064】

続いて、図16に示すように、第3のゲート形成層23Aの上に、GCパターン加工用の例えばSiN、SiO2を用いたマスク材43,44をパターン形成する。そして、図17に示すように、マスク材43,44を用いたRIEによって、積層体をゲート絶縁層12の上まで選択的にエッチングして第3の溝を形成し、GCパターンを形成する。これにより、第1の浮遊ゲート13、第3のゲート形成層23B、第1の選択ゲート形成層16A、第2の選択ゲート形成層26A、下部コンタクト35a及び36aが形成される。このGCパターン加工は、下層のゲート絶縁層12と高い選択比を有するエッチングにより行い、下層の半導体層11をエッチングしないようにする事が望ましい。

【0065】

続いて、図18に示すように、SiO2を用いたゲート間絶縁層(IPD)32を成膜したのち、GCパターン間に制御ゲート形成層33Aを埋め込む。制御ゲート形成層33Aとしては、ポリシリコン又はメタル(Wなど)、メタルシリサイド(WSiなど)を用いることができる。

【0066】

次に、図19に示すように、制御ゲート形成層33Aに対し、RIEにてエッチバックを行うことで、制御ゲート33及び補助ゲート91e〜94eを形成する。その上に図20に示すように、CVD酸化膜や塗布酸化膜などを用いたマスク材33mを埋め込み、SiNを用いたマスク43をストッパとしてCMPにて上面を平坦化する。さらにその後、選択ゲート形成層16A,26Aや図示しないロウデコーダ部のトランジスタを形成するため、EI(Etching Inter Poly)溝に相当する選択ゲート溝加工をRIEなどにより行い、図21に示すように、第2の選択ゲート形成層26B、第1の絶縁層31及び第1の選択ゲート16に至る第4の溝17Aを形成する。

【0067】

次に、上層セル、下層セルのそれぞれに独立した選択ゲートトランジスタS11〜S22を形成するために、図22に示すように、選択ゲート溝17Aに第1の選択ゲート線17、層間絶縁層34及び第2の選択ゲート線27を、埋め込みとエッチバックとを繰り返しながら順次形成していく。選択ゲート線17,27としては、制御ゲート33及び補助ゲート91e〜94eと同様、ポリシリコン又はメタル(Wなど)、メタルシリサイド(WSiなど)を用いることができる。第2の選択ゲート線27の上のエッチバックされた部分には、キャップ絶縁層27mが埋め込まれ、その上面はマスク材43をストッパとするCMPにより平坦化される。図23(a),(b),(c)は、図22のそれぞれA−A′断面、B−B′断面、C−C′断面である。

【0068】

次に、図24に示すように、第3のゲート形成層23BをストッパとしてCMPによる平坦化を実施し、その上にSiO2を用いた第2のゲート絶縁層22A、ポリシリコンを用いた第2の半導体層21Aを順次成膜する。尚、CMPは、制御ゲート33をストッパとして行っても良い。図25(a),(b),(c)は、図24のそれぞれA−A′断面、B−B′断面、C−C′断面である。

【0069】

続いて、図26に示すように、上層の第2の半導体層21A、第2のゲート絶縁層22A、第3のゲート形成層23B及び第2の選択ゲート形成層26Bに対してAAパターン加工を行うため、第2の半導体層21Aの上にAAパターン加工用のSiNを用いたマスク材45をパターン形成し、RIEにてAAパターン加工を行う。図27(a),(b),(c)は、図26のそれぞれA−A′断面、B−B′断面、C−C′断面である。以上の工程で、第2の浮遊ゲート23が形成されると共に、この第2の浮遊ゲート23に対して第2のゲート絶縁層22及び第2の半導体層21が自己整合的に形成される。

【0070】

次に、上層のAAパターンの溝に第2の素子分離絶縁層25(図1、図3)を埋め込む。最後に、第2の半導体層、第2のゲート絶縁層、上部コンタクト層、第1の絶縁層及び前記下部コンタクトにビアホールを形成し、形成したビアホールに上部コンタクトを埋め込む。ビアコンタクト形成の際には、ビアホールは第1の絶縁層を貫通し、下部のコンタクトの上面が露出する様に設ける。

【0071】

本実施形態のように、制御ゲート線33を形成する工程と共通する工程を用いて、補助ゲート91e及び94eを形成することができ、製造工程数の削減を図ることが可能となる。

【0072】

[第2の実施形態]

次に、第2の実施形態に係る不揮発性半導体記憶装置の消去動作について説明する。図28は、本実施形態に係る不揮発性半導体記憶装置の消去動作を説明する為の概略図である。本実施形態に係る不揮発性半導体記憶装置の消去動作は、基本的には第1の実施形態と同様であるが、以下の点において異なっている。即ち、本実施形態においては、第4の上部補助トランジスタ94bを導通状態とし、第2のビット線側選択ゲート線27に消去電圧VBL_eraseよりも低い電圧VSG_eraseを印加してGIDLを発生させ、GIDLによって発生した正孔(ホール)h+によって第2の半導体層21の電位を上昇させる。尚、電圧VSG_eraseは、第2の選択ゲート線27−第2の半導体層21間及び第2の選択ゲート線27−第1の選択ゲート線17において絶縁破壊が生じないような値に設定する。

[その他の実施形態]

以上、本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これらの新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0073】

10…第1のメモリセルアレイ層、11…第1の半導体層、12…第1のゲート絶縁層、13…第1の浮遊ゲート、15…第1の素子分離絶縁層、16…第1の選択ゲート、17…第1の選択ゲート線、20…第2のメモリセルアレイ層、21…第2の半導体層、22…第2のゲート絶縁層、23…第2の浮遊ゲート、25…第2の素子分離絶縁層、26…第2の選択ゲート、27…第2の選択ゲート線、31…第1の絶縁層、32…ゲート間絶縁層、33…制御ゲート、34…第2の絶縁層、35…ビット線コンタクト、36…ソース線コンタクト、37…ワード線コンタクト、38…選択ゲート線コンタクト、91e…第1の補助ゲート、92e…第2の補助ゲート、93e…第3の補助ゲート、94e…第4の補助ゲート、91a…第1の下部補助トランジスタ、92a…第2の下部補助トランジスタ、93a…第3の下部補助トランジスタ、94a…第4の下部補助トランジスタ、91b…第1の上部補助トランジスタ、92b…第2の上部補助トランジスタ、93b…第3の上部補助トランジスタ、94b…第4の上部補助トランジスタ。

【特許請求の範囲】

【請求項1】

第1の方向に直列接続された複数の第1のメモリセル、前記複数の第1のメモリセルとソース線との間に接続された第1のソース線側選択ゲートトランジスタ及び前記複数の第1のメモリセルとビット線との間に接続された第1のビット線側選択ゲートトランジスタを具備する第1のNANDセルユニットを有し、前記第1のメモリセルが、第1の半導体層と、前記第1の半導体層の上に形成された第1のゲート絶縁層と、前記第1のゲート絶縁層の上に形成された第1の浮遊ゲートとを有し、前記第1のソース線側選択ゲートトランジスタ及び第1のビット線側選択ゲートトランジスタが、前記第1の半導体層と、前記第1のゲート絶縁層と、前記第1のゲート絶縁層の上に形成された第1の選択ゲートとを有する第1のメモリセルアレイ層と、

前記第1のメモリセルアレイ層の上に形成された第1の絶縁層と、

前記第1の絶縁層の上に形成され、前記第1の方向に直列接続された複数の第2のメモリセル、前記複数の第2のメモリセルとソース線との間に接続された第2のソース線側選択ゲートトランジスタ及び前記複数の第2のメモリセルとビット線との間に接続された第2のビット線側選択ゲートトランジスタを具備する第2のNANDセルユニットを有し、前記第2のメモリセルが、第2の浮遊ゲートと、前記第2の浮遊ゲートの上に形成された第2のゲート絶縁層と、前記第2のゲート絶縁層の上に形成された第2の半導体層とを有し、前記第2のソース線側選択ゲートトランジスタ及び前記第2のビット線側選択ゲートトランジスタが、第2の選択ゲートと、前記第2のゲート絶縁層と、前記第2のゲート絶縁層の上に形成された前記第2の半導体層を有する第2のメモリセルアレイ層と、

前記第1の絶縁層を介して上下に位置する前記第1及び前記第2の浮遊ゲートの前記第1の方向の両側面にゲート間絶縁層を介して形成され、前記第1の方向と直交する第2の方向に延びる制御ゲートと、

前記第1の絶縁層を介して上下に位置する前記第1及び第2の選択ゲートの前記第1の方向の両側面に前記ゲート間絶縁層を介して形成され、前記第2の方向に延び、前記第1及び第2の半導体層並びに前記第1及び第2のゲート絶縁層と共に補助トランジスタを形成する補助ゲートと

を備え、

前記補助ゲートは、

前記ソース線と前記ソース線側の前記第1及び第2の選択ゲートとの間にゲート間絶縁層を介して形成され、前記第2の方向に延び、第1の補助トランジスタのゲートとなる第1の補助ゲートと、

前記ソース線側の前記第1及び第2の選択ゲートと前記複数の第1及び第2のメモリセルとの間にゲート間絶縁層を介して形成され、前記第2の方向に延び、第2の補助トランジスタのゲートとなる第2の補助ゲートと、

前記複数の第1及び第2のメモリセルと前記ビット線側の前記第1及び第2の選択ゲートとの間にゲート間絶縁層を介して形成され、前記第2の方向に延び、第3の補助トランジスタのゲートとなる第3の補助ゲートと、

前記ビット線側の前記第1及び第2の選択ゲートと前記ビット線との間にゲート間絶縁層を介して形成され、前記第2の方向に延び、第4の補助トランジスタのゲートとなる第4の補助ゲートと

を備え、

書き込み動作時に、記第1の補助ゲートに前記第1の補助トランジスタをオフする第1の電圧を印加し、前記第3及び第4の補助ゲートに前記第3及び第4の補助トランジスタをオンする第2の電圧を印加し、前記第2の補助ゲートに前記第1の電圧と前記第2の電圧の中間の電圧を印加し、

読出し動作又は書き込み動作時に、前記読出し動作又は書き込み動作の対象となる前記NANDセルユニットと前記ソース線を介して隣接するNANDセルユニットの前記第1の補助トランジスタをオフ状態にする

事を特徴とする不揮発性半導体記憶装置。

【請求項2】

第1の方向に直列接続された複数の第1のメモリセル、前記複数の第1のメモリセルとソース線との間に接続された第1のソース線側選択ゲートトランジスタ及び前記複数の第1のメモリセルとビット線との間に接続された第1のビット線側選択ゲートトランジスタを具備する第1のNANDセルユニットを有し、前記第1のメモリセルが、第1の半導体層と、前記第1の半導体層の上に形成された第1のゲート絶縁層と、前記第1のゲート絶縁層の上に形成された第1の浮遊ゲートとを有し、前記第1のソース線側選択ゲートトランジスタ及び第1のビット線側選択ゲートトランジスタが、前記第1の半導体層と、前記第1のゲート絶縁層と、前記第1のゲート絶縁層の上に形成された第1の選択ゲートとを有する第1のメモリセルアレイ層と、

前記第1のメモリセルアレイ層の上に形成された第1の絶縁層と、

前記第1の絶縁層の上に形成され、前記第1の方向に直列接続された複数の第2のメモリセル、前記複数の第2のメモリセルとソース線との間に接続された第2のソース線側選択ゲートトランジスタ及び前記複数の第2のメモリセルとビット線との間に接続された第2のビット線側選択ゲートトランジスタを具備する第2のNANDセルユニットを有し、前記第2のメモリセルが、第2の浮遊ゲートと、前記第2の浮遊ゲートの上に形成された第2のゲート絶縁層と、前記第2のゲート絶縁層の上に形成された第2の半導体層とを有し、前記第2のソース線側選択ゲートトランジスタ及び前記第2のビット線側選択ゲートトランジスタが、第2の選択ゲートと、前記第2のゲート絶縁層と、前記第2のゲート絶縁層の上に形成された前記第2の半導体層を有する第2のメモリセルアレイ層と、

前記第1の絶縁層を介して上下に位置する前記第1及び前記第2の浮遊ゲートの前記第1の方向の両側面にゲート間絶縁層を介して形成され、前記第1の方向と直交する第2の方向に延びる制御ゲートと、

前記第1の絶縁層を介して上下に位置する前記第1及び第2の選択ゲートの前記第1の方向の両側面に前記ゲート間絶縁層を介して形成され、前記第2の方向に延び、前記第1及び第2の半導体層並びに前記第1及び第2のゲート絶縁層と共に補助トランジスタを形成する補助ゲートと

を備えることを特徴とする不揮発性半導体記憶装置。

【請求項3】

前記補助ゲートは、

前記ソース線と前記ソース線側の前記第1及び第2の選択ゲートとの間にゲート間絶縁層を介して形成され、前記第2の方向に延び、第1の補助トランジスタのゲートとなる第1の補助ゲートと、

前記ソース線側の前記第1及び第2の選択ゲートと前記複数の第1及び第2のメモリセルとの間にゲート間絶縁層を介して形成され、前記第2の方向に延び、第2の補助トランジスタのゲートとなる第2の補助ゲートと、

前記複数の第1及び第2のメモリセルと前記ビット線側の前記第1及び第2の選択ゲートとの間にゲート間絶縁層を介して形成され、前記第2の方向に延び、第3の補助トランジスタのゲートとなる第3の補助ゲートと、

前記ビット線側の前記第1及び第2の選択ゲートと前記ビット線との間にゲート間絶縁層を介して形成され、前記第2の方向に延び、第4の補助トランジスタのゲートとなる第4の補助ゲートと

を備えることを特徴とする請求項2記載の不揮発性半導体記憶装置。

【請求項4】

書き込み動作時に、記第1の補助ゲートに前記第1の補助トランジスタをオフする第1の電圧を印加し、前記第3及び第4の補助ゲートに前記第3及び第4の補助トランジスタをオンする第2の電圧を印加し、前記第2の補助ゲートに前記第1の電圧と前記第2の電圧の中間の電圧を印加する

ことを特徴とする請求項2又は3記載の不揮発性半導体記憶装置。

【請求項5】

読出し動作又は書き込み動作時に、前記読出し動作又は書き込み動作の対象となる前記NANDセルユニットと前記ソース線を介して隣接するNANDセルユニットの前記第1の補助トランジスタをオフ状態にする

事を特徴とする請求項3記載の不揮発性半導体記憶装置。

【請求項6】

第1の半導体層の上に第1のゲート絶縁層及び浮遊ゲート形成層を形成し、

前記浮遊ゲート形成層、前記第1のゲート絶縁層及び前記第1の半導体層に第1の方向に直交する第の2方向に所定の間隔で前記第1の方向に延びる溝を形成して第1の素子分離絶縁層を埋め込み、

前記浮遊ゲート形成層及び前記第1の素子分離絶縁層の上に第1の絶縁層を形成し、

前記第1の絶縁層の上に更に浮遊ゲート形成層を形成し、

前記第1の絶縁層及び前記第1の絶縁層を介して形成された前記浮遊ゲート形成層に前記第2の方向に延びる複数の溝を形成してゲート間絶縁層で覆い、

前記ゲート間絶縁層に制御ゲート及び補助ゲートを埋め込む

ことを特徴とする不揮発性半導体装置の製造方法。

【請求項1】

第1の方向に直列接続された複数の第1のメモリセル、前記複数の第1のメモリセルとソース線との間に接続された第1のソース線側選択ゲートトランジスタ及び前記複数の第1のメモリセルとビット線との間に接続された第1のビット線側選択ゲートトランジスタを具備する第1のNANDセルユニットを有し、前記第1のメモリセルが、第1の半導体層と、前記第1の半導体層の上に形成された第1のゲート絶縁層と、前記第1のゲート絶縁層の上に形成された第1の浮遊ゲートとを有し、前記第1のソース線側選択ゲートトランジスタ及び第1のビット線側選択ゲートトランジスタが、前記第1の半導体層と、前記第1のゲート絶縁層と、前記第1のゲート絶縁層の上に形成された第1の選択ゲートとを有する第1のメモリセルアレイ層と、

前記第1のメモリセルアレイ層の上に形成された第1の絶縁層と、

前記第1の絶縁層の上に形成され、前記第1の方向に直列接続された複数の第2のメモリセル、前記複数の第2のメモリセルとソース線との間に接続された第2のソース線側選択ゲートトランジスタ及び前記複数の第2のメモリセルとビット線との間に接続された第2のビット線側選択ゲートトランジスタを具備する第2のNANDセルユニットを有し、前記第2のメモリセルが、第2の浮遊ゲートと、前記第2の浮遊ゲートの上に形成された第2のゲート絶縁層と、前記第2のゲート絶縁層の上に形成された第2の半導体層とを有し、前記第2のソース線側選択ゲートトランジスタ及び前記第2のビット線側選択ゲートトランジスタが、第2の選択ゲートと、前記第2のゲート絶縁層と、前記第2のゲート絶縁層の上に形成された前記第2の半導体層を有する第2のメモリセルアレイ層と、

前記第1の絶縁層を介して上下に位置する前記第1及び前記第2の浮遊ゲートの前記第1の方向の両側面にゲート間絶縁層を介して形成され、前記第1の方向と直交する第2の方向に延びる制御ゲートと、

前記第1の絶縁層を介して上下に位置する前記第1及び第2の選択ゲートの前記第1の方向の両側面に前記ゲート間絶縁層を介して形成され、前記第2の方向に延び、前記第1及び第2の半導体層並びに前記第1及び第2のゲート絶縁層と共に補助トランジスタを形成する補助ゲートと

を備え、

前記補助ゲートは、

前記ソース線と前記ソース線側の前記第1及び第2の選択ゲートとの間にゲート間絶縁層を介して形成され、前記第2の方向に延び、第1の補助トランジスタのゲートとなる第1の補助ゲートと、

前記ソース線側の前記第1及び第2の選択ゲートと前記複数の第1及び第2のメモリセルとの間にゲート間絶縁層を介して形成され、前記第2の方向に延び、第2の補助トランジスタのゲートとなる第2の補助ゲートと、

前記複数の第1及び第2のメモリセルと前記ビット線側の前記第1及び第2の選択ゲートとの間にゲート間絶縁層を介して形成され、前記第2の方向に延び、第3の補助トランジスタのゲートとなる第3の補助ゲートと、

前記ビット線側の前記第1及び第2の選択ゲートと前記ビット線との間にゲート間絶縁層を介して形成され、前記第2の方向に延び、第4の補助トランジスタのゲートとなる第4の補助ゲートと

を備え、

書き込み動作時に、記第1の補助ゲートに前記第1の補助トランジスタをオフする第1の電圧を印加し、前記第3及び第4の補助ゲートに前記第3及び第4の補助トランジスタをオンする第2の電圧を印加し、前記第2の補助ゲートに前記第1の電圧と前記第2の電圧の中間の電圧を印加し、

読出し動作又は書き込み動作時に、前記読出し動作又は書き込み動作の対象となる前記NANDセルユニットと前記ソース線を介して隣接するNANDセルユニットの前記第1の補助トランジスタをオフ状態にする

事を特徴とする不揮発性半導体記憶装置。

【請求項2】

第1の方向に直列接続された複数の第1のメモリセル、前記複数の第1のメモリセルとソース線との間に接続された第1のソース線側選択ゲートトランジスタ及び前記複数の第1のメモリセルとビット線との間に接続された第1のビット線側選択ゲートトランジスタを具備する第1のNANDセルユニットを有し、前記第1のメモリセルが、第1の半導体層と、前記第1の半導体層の上に形成された第1のゲート絶縁層と、前記第1のゲート絶縁層の上に形成された第1の浮遊ゲートとを有し、前記第1のソース線側選択ゲートトランジスタ及び第1のビット線側選択ゲートトランジスタが、前記第1の半導体層と、前記第1のゲート絶縁層と、前記第1のゲート絶縁層の上に形成された第1の選択ゲートとを有する第1のメモリセルアレイ層と、

前記第1のメモリセルアレイ層の上に形成された第1の絶縁層と、

前記第1の絶縁層の上に形成され、前記第1の方向に直列接続された複数の第2のメモリセル、前記複数の第2のメモリセルとソース線との間に接続された第2のソース線側選択ゲートトランジスタ及び前記複数の第2のメモリセルとビット線との間に接続された第2のビット線側選択ゲートトランジスタを具備する第2のNANDセルユニットを有し、前記第2のメモリセルが、第2の浮遊ゲートと、前記第2の浮遊ゲートの上に形成された第2のゲート絶縁層と、前記第2のゲート絶縁層の上に形成された第2の半導体層とを有し、前記第2のソース線側選択ゲートトランジスタ及び前記第2のビット線側選択ゲートトランジスタが、第2の選択ゲートと、前記第2のゲート絶縁層と、前記第2のゲート絶縁層の上に形成された前記第2の半導体層を有する第2のメモリセルアレイ層と、

前記第1の絶縁層を介して上下に位置する前記第1及び前記第2の浮遊ゲートの前記第1の方向の両側面にゲート間絶縁層を介して形成され、前記第1の方向と直交する第2の方向に延びる制御ゲートと、

前記第1の絶縁層を介して上下に位置する前記第1及び第2の選択ゲートの前記第1の方向の両側面に前記ゲート間絶縁層を介して形成され、前記第2の方向に延び、前記第1及び第2の半導体層並びに前記第1及び第2のゲート絶縁層と共に補助トランジスタを形成する補助ゲートと

を備えることを特徴とする不揮発性半導体記憶装置。

【請求項3】

前記補助ゲートは、

前記ソース線と前記ソース線側の前記第1及び第2の選択ゲートとの間にゲート間絶縁層を介して形成され、前記第2の方向に延び、第1の補助トランジスタのゲートとなる第1の補助ゲートと、

前記ソース線側の前記第1及び第2の選択ゲートと前記複数の第1及び第2のメモリセルとの間にゲート間絶縁層を介して形成され、前記第2の方向に延び、第2の補助トランジスタのゲートとなる第2の補助ゲートと、

前記複数の第1及び第2のメモリセルと前記ビット線側の前記第1及び第2の選択ゲートとの間にゲート間絶縁層を介して形成され、前記第2の方向に延び、第3の補助トランジスタのゲートとなる第3の補助ゲートと、

前記ビット線側の前記第1及び第2の選択ゲートと前記ビット線との間にゲート間絶縁層を介して形成され、前記第2の方向に延び、第4の補助トランジスタのゲートとなる第4の補助ゲートと

を備えることを特徴とする請求項2記載の不揮発性半導体記憶装置。

【請求項4】

書き込み動作時に、記第1の補助ゲートに前記第1の補助トランジスタをオフする第1の電圧を印加し、前記第3及び第4の補助ゲートに前記第3及び第4の補助トランジスタをオンする第2の電圧を印加し、前記第2の補助ゲートに前記第1の電圧と前記第2の電圧の中間の電圧を印加する

ことを特徴とする請求項2又は3記載の不揮発性半導体記憶装置。

【請求項5】

読出し動作又は書き込み動作時に、前記読出し動作又は書き込み動作の対象となる前記NANDセルユニットと前記ソース線を介して隣接するNANDセルユニットの前記第1の補助トランジスタをオフ状態にする

事を特徴とする請求項3記載の不揮発性半導体記憶装置。

【請求項6】

第1の半導体層の上に第1のゲート絶縁層及び浮遊ゲート形成層を形成し、

前記浮遊ゲート形成層、前記第1のゲート絶縁層及び前記第1の半導体層に第1の方向に直交する第の2方向に所定の間隔で前記第1の方向に延びる溝を形成して第1の素子分離絶縁層を埋め込み、

前記浮遊ゲート形成層及び前記第1の素子分離絶縁層の上に第1の絶縁層を形成し、

前記第1の絶縁層の上に更に浮遊ゲート形成層を形成し、

前記第1の絶縁層及び前記第1の絶縁層を介して形成された前記浮遊ゲート形成層に前記第2の方向に延びる複数の溝を形成してゲート間絶縁層で覆い、

前記ゲート間絶縁層に制御ゲート及び補助ゲートを埋め込む

ことを特徴とする不揮発性半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【公開番号】特開2013−110265(P2013−110265A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2011−253928(P2011−253928)

【出願日】平成23年11月21日(2011.11.21)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願日】平成23年11月21日(2011.11.21)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]