Fターム[5F083PR41]の内容

Fターム[5F083PR41]の下位に属するFターム

Fターム[5F083PR41]に分類される特許

1 - 20 / 88

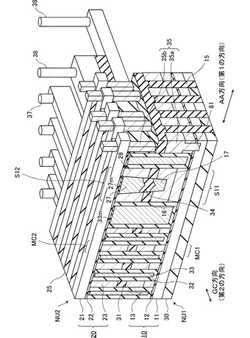

不揮発性半導体記憶装置及びその製造方法

【課題】制御性の高い不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、第1のメモリセルアレイ層と、第1のメモリセルアレイ層の上に形成された第1の絶縁層と、第1の絶縁層の上に形成された第2のメモリセルアレイ層と、第1の絶縁層を介して上下に位置する第1及び第2の浮遊ゲートの第1の方向の両側面にゲート間絶縁層を介して形成され、第1の方向と直交する第2の方向に延びる制御ゲートと、第1の絶縁層を介して上下に位置する第1及び第2の選択ゲートの第1の方向の両側面にゲート間絶縁層を介して形成され、第2の方向に延び、第1及び第2の半導体層並びに第1及び第2のゲート絶縁層と共に補助トランジスタを形成する補助ゲートとを備える。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】製造の容易な不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、第1のメモリセルアレイ層と、第1のメモリセルアレイ層の上に形成された第1の絶縁層と、第2のメモリセルを具備する第2のNANDセルユニットを有する第2のメモリセルアレイ層と、第1の絶縁層を介して上下に位置する第1及び第2の浮遊ゲートの第1の方向の両側面にゲート間絶縁層を介して形成され、第1の方向と直交する第2の方向に延びる制御ゲートと、第1のNANDセルユニットの両端に位置し、第1の浮遊ゲートと同層に形成され、第1の半導体層と接続される下部コンタクトと、第2のNANDセルユニットの両端に位置し、第2の半導体層と下部コンタクトとを接続する上部コンタクトとを備える。

(もっと読む)

半導体記憶装置の製造方法

【課題】スループットの向上を図る。

【解決手段】半導体記憶装置の製造方法は、基板上に、不純物濃度が第1濃度である第1シリコン層35、不純物濃度が第1濃度より低い第2濃度である第1犠牲層、不純物濃度が第1濃度である第2シリコン層35、および不純物濃度が第2濃度である第2犠牲層が順に積層された積層体を形成する工程と、積層体上に、第1絶縁膜を形成する工程と、積層体および第1絶縁膜内に、溝22を形成する工程と、溝内に、不純物濃度が第1濃度より低く、第2濃度より高い第3濃度である第3犠牲層90を埋め込む工程と、ウェットエッチングにより、溝内の第3犠牲層を上面から後退させて除去することで、第1犠牲層および第2犠牲層の端面を後退させる工程と、第1シリコン層および第2シリコン層の端面を第1犠牲層および第2犠牲層の端面に沿ってエッチングする工程とを具備する。

(もっと読む)

半導体装置の製造方法

【課題】埋込ワード線の高さにばらつきのない半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、複数の素子分離領域を形成すると共に、素子分離領域間に素子形成領域を形成する工程と、素子形成領域に交差する第1の方向に延在するゲート電極溝を形成する工程と、ゲート電極溝の内壁にゲート絶縁膜を形成する工程と、ゲート電極溝の内壁にゲート絶縁膜を介して第1導電膜を形成する工程と、ゲート電極溝内を埋め込むように第2導電膜を形成する工程と、第2導電膜上に平坦化膜を形成する工程と、第2導電膜が露出するように平坦化膜をエッチングして除去する第1のエッチング工程と、第2導電膜がゲート電極溝の下部に残留するように第2導電膜をエッチングする第2のエッチング工程と、第1導電膜が前記ゲート電極溝の下部に残留するように第1導電膜をエッチングする第3のエッチング工程と、を有することを特徴とする。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】STIの形成によるウェル拡散層の不純物濃度の変化を抑制し、かつ、ウェル拡散層のドーズロスを抑制した半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体記憶装置は、半導体基板を備える。メモリセル領域には、複数のメモリセルが半導体基板上に形成されている。周辺回路領域には、複数のメモリ素子を制御する複数の半導体素子が形成されている。素子分離領域は、複数のメモリセル間を分離し、あるいは、複数の半導体素子間を分離する。周辺回路領域において半導体素子が形成されているアクティブエリアの不純物濃度は、半導体基板の表面に対して水平方向に素子分離領域の側面からアクティブエリアの内部へ向かって低下している。

(もっと読む)

三次元半導体装置及びその製造方法

【課題】導電層とコンタクトの十分な接続を確保可能な三次元半導体装置及びその製造方法を提供する。

【解決手段】三次元半導体装置は、半導体基板上に導電層と絶縁層とが交互に複数積層され、前記複数の導電層は、それらの端部の位置が上層から下層にかけて徐々にずれた階段部を形成し、前記階段部の各ステップに、積層方向に延びるコンタクトがそれぞれ接続されたものであり、前記階段部が、少なくとも最上層から所定の導電層までは、上層の導電層ほど前記ステップの幅が広くなるように形成されている。

(もっと読む)

信号処理回路

【課題】新たな構成の不揮発性の記憶回路を用いた信号処理回路を提供する。

【解決手段】演算部と、メモリと、演算部及びメモリを制御する制御部と、を有し、制御部は、揮発性の記憶回路と揮発性の記憶回路に保持されたデータを記憶するための第1の不揮発性の記憶回路との組を複数有し、メモリは、第2の不揮発性の記憶回路を複数有し、第1の不揮発性の記憶回路及び第2の不揮発性の記憶回路は、チャネルが酸化物半導体層に形成されるトランジスタと、トランジスタがオフ状態となることによってフローティングとなるノードに一対の電極のうちの一方が電気的に接続された容量素子とを有する。

(もっと読む)

半導体装置および配線レイアウト方法

【課題】配線間のピッチを縮小可能にした半導体装置を提供する。

【解決手段】半導体基板に形成された複数のトランジスタと、第1の方向に延在する第1の配線を備えた第1の配線層と、第1の配線層よりも上層に設けられ、第1の方向と交差する第2の方向に延在し、第1の配線と電気的に接続された第2の配線を備えた第2の配線層と、半導体基板と第1の配線層との間に設けられ、複数のトランジスタに接続する第1の中継配線と、第1の中継配線が形成された第1の中継配線層と第1の配線層との間に設けられ、第1の配線と複数のトランジスタのうちの一つとを接続する第2の中継配線とを有する構成である。

(もっと読む)

半導体装置及びその製造方法

【課題】キャパシタの高容量化と面積の低減を可能とした半導体装置及びその製造方法を提供する。

【解決手段】EEPROMメモリセル50は、シリコン基板1のメモリセル領域に設けられたN-層21aと、トンネル絶縁膜13aと、浮遊ゲート電極15aと、電極間絶縁膜

17aと、制御ゲート電極19aと、を有する。また、キャパシタ60は、シリコン基板1のキャパシタ領域に設けられた下部電極層24aと、第1の誘電体膜13cと、共通電極15cと、第2の誘電体膜17cと、上部電極19cと、を有する。下部電極層24aと第1の誘電体膜13cと共通電極15cとにより第1のキャパシタ61が構成されると共に、共通電極15cと第2の誘電体膜17cと上部電極19cとにより第2のキャパシタ62が構成されており、第1のキャパシタ61と第2のキャパシタ62とが並列に接続されている。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】選択ゲート電極および当該選択ゲート電極に隣接する他のゲート電極間の間隔を所望の距離に調整できるようにした不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】複数本のラインパターンのうち選択ゲート電極の形成領域のラインパターンから他のゲート電極の形成領域のラインパターンにかけてマスクした条件にて複数本のラインパターンの側壁面をスリミングし、選択ゲート電極の形成領域のラインパターンから他のゲート電極の形成領域のラインパターンにかけてパターン間膜を埋込むと共にスリミングされたラインパターンの側壁面に沿ってパターン間膜を形成し、選択ゲート電極の形成領域のラインパターンをマスクした条件にて当該ラインパターン以外のラインパターンを除去しマスクされたラインパターンを残留させ、パターン間膜および残留したラインパターンをマスクとして第1膜を異方性エッチングし、第1膜をマスクとして導電膜をエッチングする不揮発性半導体記憶装置の製造方法を提供する。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置を高い歩留りで製造し得る半導体装置の製造方法を提供する。

【解決手段】ゲート配線16aを形成するのと同時に形成された位置合わせマーク16fに対して位置合わせして、コンタクトホールの第1の部分パターン61a1をゲート配線の一部と重なり合うようにフォトレジスト膜に露光する工程と、活性領域11bを形成するのと同時に形成された位置合わせマーク11fに対して位置合わせして、コンタクトホールの第2の部分パターン61a2を活性領域の一部と重なり合うようにフォトレジスト膜に露光する工程と、フォトレジスト膜を現像し、第1の部分パターンと第2の部分パターンとが露光された箇所に開口部を形成する工程と、フォトレジスト膜をマスクとして絶縁膜をエッチングし、ゲート配線とソース/ドレイン拡散層20とに達するコンタクトホールを形成する工程とを有している。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、メモリセルアレイを有する半導体装置において、直列に接続された第1乃至第mのメモリセルに含まれる各ノードに生じる寄生容量の値を同等の値とすることで、安定して動作可能な半導体装置とする。

(もっと読む)

半導体装置の製造方法

【課題】 メモリセルアレイ領域と周辺回路領域との配線溝の深さを最適化する。

【解決手段】 本発明の一態様の半導体装置の製造方法によれば、レジストパターンをマスクとして芯材膜を加工する工程と、前記芯材膜上に被加工膜とエッチング選択比がある側壁膜を形成する工程と、前記側壁膜を異方性エッチング工程により加工する工程と、前記芯材膜を前記側壁膜と選択的に除去する工程と、第1領域の前記側壁膜上および前記被加工膜上に絶縁膜を第1の膜厚を有するように形成し、第2領域の前記被加工膜上に前記絶縁膜を第2の膜厚を有するように形成する工程と、を備えている。さらに、前記第2領域においてフォトリソグラフィ工程によりレジストパターンを形成する工程と、前記第1領域における前記側壁膜と前記第2領域における前記レジストパターンとをマスクとして前記絶縁膜および前記被加工膜を加工し、前記被加工膜に配線溝を形成する工程と、を備えている。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】動作マージンを確保した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリセル及び前記複数のメモリセルを選択する複数の選択配線を有するセルアレイを複数積層してなるセルアレイブロックと、第1高さから第2高さまで積層方向に延び、前記セルアレイブロックの選択配線のうちの所定の第1配線が側面に接続された柱状の第1ビアと、前記第1高さから第2高さまで積層方向に延び、前記セルアレイブロックの選択配線のうち前記第1配線よりも上層の所定の第2配線が側面に接続された柱状の第2ビアとを備え、前記第2配線は、前記第1配線よりも積層方向に厚く、且つ、前記第1配線よりも抵抗率が高いことを特徴とする。

(もっと読む)

半導体装置

【課題】ゲートコンタクトプラグ形成のためのコンタクトホールの深さを適切に制御可能とする。

【解決手段】半導体装置1は、活性領域ARを囲む第1の絶縁体ピラー21と、第1の絶縁体ピラー21の活性領域AR側の側面21sとy方向に相対向する側面22sを有する第2の絶縁体ピラー22と、第1及び第2の絶縁体ピラー21,22の上面を覆う絶縁膜31と、第1のゲート電極16と電気的に接続し、かつ少なくとも側面21s,22sを覆う第2のゲート電極23と、底面に絶縁膜31及び第2のゲート電極23が露出したコンタクトホールの内部に設けられ、かつ第2のゲート電極23の上面と電気的に接続するゲートコンタクトプラグ42とを備え、側面21s,22s間の距離は、ゲートコンタクトプラグ42のx方向の長さより短く、ゲートコンタクトプラグ42は側面21s,22s間の領域で第2のゲート電極23と電気的に接続する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】歩留まりに優れた構造を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、基板と、基板上に形成されており、配線および絶縁層により構成された配線層が複数積層された多層配線層と、平面視において、基板内の記憶回路領域に形成されており、多層配線層内に埋め込まれた少なくとも1以上の容量素子および周辺回路を有する記憶回路と、平面視において、基板内の憶回路領域とは異なる領域である論理回路領域に形成された論理回路と、を備え、容量素子は、下部電極、容量絶縁膜、上部電極、埋設電極および、上部接続配線で構成されており、上部接続配線と埋設電極とは、同一の材料かつ一体に構成されており、上部接続配線と下部電極との間には、論理回路を構成する前記配線が少なくとも1以上設けられており、上部接続配線の上面と、上部接続配線と同じ配線層に形成された論理回路を構成する配線の上面とが、同一面を構成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量素子の平面形状を大きくせずに、その容量を大きくすることができ、かつ容量素子のリーク電流が増大することを抑制する。

【解決手段】下部電極410は、表層に、厚さが2nm以下の金属含有酸化層414を有している。金属含有酸化層414は、下部電極410の表面を酸化することにより形成されている。そして誘電膜420は、バルク状態において常温で出現する第1相と、バルク状態において第1相より高温で出現する第2相と、を含んでいる。第2相は第1相より比誘電率が高い。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ロジック回路のコンタクト抵抗の増加を抑制しつつ、メモリ回路のキャパシタ容量を最大限に高めることが実現される半導体装置の構造およびその製造方法を提供する。

【解決手段】半導体装置においては、ロジック回路を構成する配線を有する配線層の層数をMとし、メモリ回路を構成する配線を有する配線層の層数をNとしたとき(MおよびNは自然数であって、M>N)、(M−N)層あるいは(M−N+1)層の配線層にわたって、容量素子150が設けられている。

(もっと読む)

半導体記憶装置

【課題】メモリセルの面積を縮小しつつ、選択トランジスタや周辺トランジスタの特性を良好にし、且つ製造方法を容易にすることが可能な半導体装置。

【解決手段】半導体記憶装置は、基板101と、基板上に順に形成された第1のゲート絶縁膜、第1の浮遊ゲート、第2のゲート絶縁膜、第2の浮遊ゲート、ゲート間絶縁膜、及び制御ゲートを含み、第1及び第2のゲート絶縁膜は、FN(Fowler-Nordheim)トンネル膜として機能し、ゲート間絶縁膜は、電荷ブロック膜として機能するセルトランジスタ201と、基板上に順に形成されたゲート絶縁膜及びゲート電極を含む選択又は周辺トランジスタ301とを備え、ゲート絶縁膜及びゲート電極は、基板上に形成された第1絶縁膜と、第1絶縁膜上に順に形成され、それぞれ第1の浮遊ゲート、第2のゲート絶縁膜、第2の浮遊ゲート、ゲート間絶縁膜、及び制御ゲートと同じ材料層から形成される。

(もっと読む)

半導体装置の製造方法

【課題】偽下部電極および下部電極となる導電膜を形成し、下部電極の内径を十分に大きくすることができ、しかも、境界領域から周辺回路領域にわたって空洞が形成されることを防止できる微細化に対応可能な半導体装置の製造方法を提供する。

【解決手段】層間絶縁膜24に、キャパシタの形状を規定するシリンダ孔91と偽下部電極51aの形状を規定する偽下部電極溝91aとを形成する工程と、シリンダ孔91内および偽下部電極溝91a内に導電膜51bを形成する工程と、導電膜51bをストッパとしてウエットエッチングすることにより、偽下部電極溝91aのメモリセル領域側に設けられている層間絶縁膜24を除去するウエットエッチング工程と、導電膜51bを薄膜化する薄膜化工程とを備える半導体装置の製造方法とする。

(もっと読む)

1 - 20 / 88

[ Back to top ]