Fターム[5F083PR28]の内容

Fターム[5F083PR28]の下位に属するFターム

セルフアライン (364)

Fターム[5F083PR28]に分類される特許

1 - 14 / 14

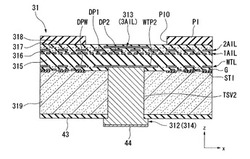

半導体装置

【課題】とりわけ表面マークの下部に配線タングステンパッドがある場合でも、表面マークのコントラスト低下を抑制する。

【解決手段】メモリチップ31は、配線タングステン階層WTL、第1、第2、第3アルミニウム配線階層1AlL,2AlL,3AlLを備える多層配線構造を備える。各配線層の間には、第1、第2、第3層間絶縁膜315,316,317がそれぞれ形成され、第3アルミニウム配線階層3AlLとポリイミド膜PIとの間には、第4層間絶縁膜318が形成されている。第1のダミーパターンDP1は、第1アルミニウム配線階層1AlLに形成され、第2層間絶縁膜316に覆われている。第2のダミーパターンDP2は、第2アルミニウム配線階層2AlLに形成され、第3層間絶縁膜317に覆われている。第2ダミーパターンDP2は、第1ダミーパターンDP1よりも幅が長い。

(もっと読む)

半導体装置の製造方法

【課題】ホールパターンの寸法のばらつきを抑え、ホールパターンの未開口の発生を抑制する半導体装置の製造方法を提供する。

【解決手段】一つの実施形態によれば、半導体装置の製造方法は、第1と第2のレジストパターン形成工程を含む。第1のレジストパターン形成工程では、コンタクトホール形成領域に、開口パターン111を有する第1のレジストパターン11を形成する。第2のレジストパターン形成工程では、コンタクトホール形成領域の第1の領域R1に開口パターン112を有し、第2の領域R2に第3の開口パターン112を有する第2のレジストパターン12を形成する。第2と第3の開口パターン112は、1本おきの活性領域3上に配列した形状を有するが、互いに異なる活性領域3上に形成される。そして、先に行う第1または第2のレジストパターン形成工程では、後のリソグラフィ処理で耐性を有するレジストの不溶化処理が行われる。

(もっと読む)

不揮発性半導体記憶装置

【課題】デポジッション膜を形成することなく、ゲートとコンタクトのショートを抑制する不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置1のコントロールゲート14を、フローティングゲート13側に位置する第1側面と、第1側面の反対に位置する第2側面と、コントロールゲート14の第1側面側の上部に形成されたシリサイド領域22と、コントロールゲート14の第2側面側の上部に形成された突出部8とを含むように構成する。そのサイドウォール絶縁膜21は、シリサイド領域22を覆うことなく突出部8の少なくとも一部を被覆する第1部分と、第1部分から連続的に設けられ、第2側面に接触して第2側面を被覆する第2部分とを含むものとする。

(もっと読む)

位置合わせマーク、半導体装置の製造方法およびマスクセット

【課題】少ないマスク数でメモリセルの積層を行うことができる位置合わせマークを提供すること。

【解決手段】位置合わせマークは、積層型クロスポイントメモリを形成する第1のマスクを用いてメモリセルとともに形成され、ビット線BL2を形成する際の位置合わせに用いられる位置合わせマークPa1と、ワード線WL3を形成する際の位置合わせとして位置検出信号が照射された場合に、第2のマスクによって形成されてワード線WL2を形成する際の位置合わせに用いられた位置合わせマークPb1の影響を受けないよう位置合わせマークPb1からの位置検出信号の乱反射を抑えるベタパターンPa2とを備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】エッチングストッパ膜を有し、配線間容量の増大を抑制可能な半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体基板11と、半導体基板11の表面上部に配設された層間絶縁膜29と、層間絶縁膜29に埋め込まれ、半導体基板11に対向する上面が層間絶縁膜29の上面と面一に配設され、互いに離間して配置された複数のビアプラグ31と、層間絶縁膜29及びビアプラグ31の表面上部に配設された層間絶縁膜39と、層間絶縁膜39によって分離され、ビアプラグ31と接続され、ビアプラグ31に対向する上面が層間絶縁膜39の上面と面一に配設され、層間絶縁膜39を挟んで相対向する側面に、層間絶縁膜29の側から順に、層間絶縁膜29とはエッチング性が異なり且つ層間絶縁膜39より比誘電率の高い側壁絶縁膜35、及び側壁絶縁膜35とはエッチング性が異なる側壁絶縁膜37を有する複数の第2配線33とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化を進める際に製造容易な構造を提供する。

【解決手段】基板の平面方向において連続して配置されるMOSトランジスタを有する半導体装置において、ゲート電極および該ゲート電極間を接続する配線部(矢印13で図示する箇所)が、拡散層14が形成される基板10の表面より下層に埋め込まれている。基板10の表面には、ソース・ドレイン領域として機能する拡散層14どうしを分離するSTI構造の第一の素子分離領域12が形成されている。そして該第一の素子分離領域12が存在する層より下の層に、隣接するMOSトランジスタのチャネル領域どうしを分離するSTI構造の第二の素子分離領域11が形成されている。

(もっと読む)

半導体記憶装置及びその製造方法と半導体記憶装置の動作方法

【課題】書込み速度の向上と、かつ読出しディスターブの抑制を両立させることが可能な半導体記憶装置を提供する。

【解決手段】半導体層上に電荷蓄積膜とゲート電極105を形成し、ゲート電極105の下部に形成されたチャネル領域の両側の半導体層に2つの第1導電型の拡散領域A及びBを形成する。チャネル領域は、一方の拡散領域Aが接する側のチャネル幅Waよりも他方の拡散領域Bが接する側のチャネル幅Wbの方が大きく形成される。記憶動作時には一方の拡散領域Aへ他方の拡散領域Bよりも高い電圧を印加し、読出し時には他方の拡散領域Bへ一方の拡散領域Aよりも高い電圧を印加する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】積層時の加工寸法のバラツキや合せズレが生じても、抵抗の増大やショートの発生等を防止できる、メモリセルを三次元的に積層した不揮発性半導体記憶装置を提供する。

【解決手段】基板と、第1の柱状半導体を有する第1の選択トランジスタと、前記第1の柱状半導体上に形成された第2の柱状半導体と、前記第2の柱状半導体の周りに形成された第1の絶縁膜と、前記第1の絶縁膜の周りに形成された電荷蓄積層と、前記電荷蓄積層の周りに形成された第2の絶縁膜と、前記第2の絶縁膜の周りに形成された平板状の第1乃至第nの電極(nは2以上の自然数)とを有する複数のメモリセルと、第3の柱状半導体を有する第2の選択トランジスタと、を有するメモリストリングスを複数備え、前記メモリストリングスは前記第1乃至第nの電極を2次元的に共有し、前記第1の柱状半導体の接続部のみが前記第2の柱状半導体の径よりも大きい不揮発性半導体記憶装置。

(もっと読む)

半導体装置の製造方法

【課題】

下層合わせマークとホトレジストの間に、可視光に対し不透明な金属膜が介在した場合、下層合わせマークが検出できなくなり、パターン形成を困難にする問題を解決する。

【解決手段】

合わせマークの下に絶縁膜が位置する構成とし、マークホール内に合わせマークと絶縁膜の多層膜から成る、段差が拡大された合わせマークを自己整合で予め形成しておき、その上に対象とする金属膜を形成する。金属膜自身が合わせマークを反映する段差を有しているので、確実な合わせを可能とする。

(もっと読む)

自己整合プロセスを用いて形成された相変化メモリ

【課題】自己整合プロセスを用いて、メモリセルサイズを微細化することができる相変化メモリを提供する。

【解決手段】メモリは、複数のトランジスタが複数の行および複数の列をなしたアレイと、上記アレイと交差して複数の列をなす複数の導電線112と、上記導電線112と接触し、且つ該導電線112に合わせて自己整合している相変化素子107とを備えている。さらに、上記メモリは、上記相変化素子と接触している複数の下部電極240を備えており、各下部電極240は、或る1つの上記導電線112に合わせて自己整合しており、且つ或る1つの上記トランジスタのソース−ドレイン経路の一方の側と結合している。

(もっと読む)

半導体素子の構造及びその製造方法

【課題】自己整合シリサイド膜のシリサイドマスクパターンの形成工程で工程余裕度を向上させ、半導体素子の信頼性と収率を向上させた半導体素子の構造とその製造方法を提供する。

【解決手段】ゲート電極52aとキャパシタ上部電極52bとの間の間隔を狭くして、スペーサ絶縁膜54aをエッチングして側壁スペーサ53aを形成する時、ゲート電極52aとキャパシタ上部電極52bとの間に残留スペーサ絶縁膜53b、54bを残して、シリコン基板40を露出させない。これにより、後工程で自己整合シリサイド膜56を形成するためにシリサイドマスクパターン55を形成する時、工程余裕度を向上させることができ、従来、シリサイドマスクパターン55の整合不良に起因して発生するコンタクトホールのエッチングによるゲート電極の損傷や、ゲートとキャパシタとの間での電流漏洩などの不良を防止し、半導体素子の信頼性と収率を向上させることができる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】 ゲート電極の側壁部に電荷蓄積部を配置してなる不揮発性メモリセルにおいて、アライメントずれによる特性バラツキを抑制し、メモリセル面積の縮小化を図る。

【解決手段】 半導体基板2上に形成されたゲート絶縁膜5、ゲート絶縁膜5上に形成されたゲート電極6、ゲート電極6の行方向の両側壁部に形成された電荷蓄積部7、ゲート電極6と電荷蓄積部7の下方に位置するチャネル領域3、及び、チャネル領域3の行方向に両側の半導体基板2表面に埋め込み拡散層で形成された2つの拡散層領域4を備え、行方向に隣接する2つのメモリセルのゲート電極6が、2つの拡散層領域4と電荷蓄積部7の上方を通過して相互に接続して行方向に延伸するゲート電極配線6aを形成し、2つの拡散層領域4がゲート電極配線6aの下方に位置し、列方向に隣接する2つのメモリセルの各拡散層領域4が相互に接続して、列方向に延伸する埋め込み拡散配線4aを形成する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】 ゲート電極の側壁部に電荷蓄積部を配置してなる不揮発性メモリセルにおいて、アライメントずれによる特性バラツキを抑制し、書き込み時間の短縮を図る。

【解決手段】 半導体基板2上に形成されたゲート絶縁膜5とトンネル絶縁膜8、ゲート絶縁膜5上に形成されたゲート電極6、ゲート電極6の行方向の両側壁部のトンネル絶縁膜8上に半導体基板2の表面と平行な平板状に形成された電荷蓄積部7、ゲート電極6と電荷蓄積部7の下方に位置するチャネル領域3、及び、チャネル領域3の行方向に両側の半導体基板2表面に埋め込み拡散層で形成された2つの拡散層領域4を備え、行方向に隣接する2つのメモリセルのゲート電極6が、2つの拡散層領域4と電荷蓄積部7の上方を行方向に延伸するゲート電極配線6aで相互に接続され、ゲート電極配線6aはその下面が電荷蓄積部7の上面と絶縁膜を介して近接するように形成されている。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】微細化を実現しつつリーク電流を抑制することができ、かつ、多くの容量を保持することができるDRAM混載半導体装置を提供する。

【解決手段】本発明の半導体記憶装置のキャパシタは、ストレージノードホール9の底面を覆い、側面を第2の層間絶縁膜8の上面の高さよりも低い高さまで覆う下部電極10と、下部電極の上を覆う容量絶縁膜11と、容量絶縁膜11の上を覆う上部電極12とを備える。この構造では、ビット線コンタクト14を形成するための開口17がずれてキャパシタにまで達しても、容量が蓄積される部分の容量絶縁膜が露出することがない。そのため、リーク電流の発生を抑制することができる。また、ストレージノードホール9と開口17との間にマージンを設ける必要がないので、微細化を実現することができると共に、メモリセルサイズが一定のままで保持できる容量を多くすることができる。

(もっと読む)

1 - 14 / 14

[ Back to top ]