Fターム[5F101BD21]の内容

不揮発性半導体メモリ (42,765) | 素子構造 (12,113) | 組合せ (2,046)

Fターム[5F101BD21]の下位に属するFターム

アドレスゲートトランジスタ (1,487)

書込、消去用トランジスタ (42)

CMOS構造 (117)

BiCMOS構造 (2)

EDMOS (2)

高耐圧トランジスタ(周辺回路の) (275)

Fターム[5F101BD21]に分類される特許

1 - 20 / 121

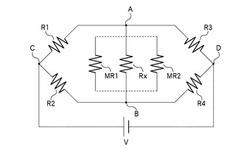

半導体装置

【課題】抵抗素子を有する半導体装置に関し、集積度を低下することなく低消費電力化と高い回路精度とを実現しうる半導体装置を提供する。

【解決手段】半導体材料により形成された複数の抵抗素子と、複数の抵抗素子の近傍に配置された加熱用抵抗素子と、対向する2つの接続ノード間に加熱用抵抗素子が接続され、対向する他の2つの接続ノード間に電源線が接続された抵抗ブリッジ回路とを有する。

(もっと読む)

ICカード表示システム

【課題】カード所有者がカード内に蓄積された情報を知りたい場合等に、外部のカード読取装置を用いてカード内に蓄積された情報を解読し、カード読取装置に搭載されているディスプレイ上に前記の蓄積情報を読み出さなければならないという不便さがあった。

【解決手段】ICカード本体と、ICカード本体における外部からの機械的な変形を電力に変換するセルフ電源装置と、ICカード本体の外側へ露出して表示を行うディスプレイ面を有し、セルフ電源装置で発生した電力の供給を受けてディスプレイ面に情報を表示する表示装置とを備えるICカード表示システムが提供される。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】コストが低い半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置の製造方法は、絶縁膜及び電極膜が交互に積層された積層体を形成する工程と、前記積層体上に、サイズが相互に異なる複数のホールが形成されたハードマスクを形成する工程と、マスク材料を堆積させることにより、最も小さい前記ホールを閉塞させると共に、その他の前記ホールを小さくする工程と、前記マスク材料及び前記ハードマスクをマスクとしてエッチングを施すことにより、前記その他のホールの直下域において、各所定枚数の前記絶縁膜及び前記電極膜を除去して、コンタクトホールを形成する工程と、前記コンタクトホールを介してエッチングを施すことにより、前記電極膜の一部分を除去して隙間を形成する工程と、前記隙間内に絶縁材料を埋め込む工程と、前記コンタクトホール内に導電材料を埋め込む工程と、を備える。

(もっと読む)

半導体記憶装置

【課題】動作速度が高い半導体記憶装置を提供する。

【解決手段】実施形態に係る半導体記憶装置は、一方向に沿って相互に平行に配列された複数枚のゲート電極膜と、前記一方向に延び、前記複数枚のゲート電極膜を貫通する半導体部材と、前記ゲート電極膜と前記半導体部材との間に設けられた電荷蓄積膜と、を備える。前記ゲート電極膜における前記半導体部材に対向した端部には、前記一方向に沿って突出した凸部が設けられており、前記ゲート電極膜間の空間の一部は気体層となっている。

(もっと読む)

半導体装置の製造方法

【課題】側壁マスクプロセスにより同時に異なる幅を持つパターンを形成する。

【解決手段】実施形態に係わる半導体装置の製造方法は、被加工材12上に第1及び第2の芯材を形成する工程と、第1及び第2の芯材の上面及び側面を覆う第1及び第2の層16a,16bを有する被覆材を形成する工程と、第1の芯材を覆う第2の層16bを除去する工程と、被覆材をエッチングすることにより、第1の芯材の側面に第1の層16aを有する第1の側壁マスクを形成し、第2の芯材の側面に第1及び第2の層16a,16bを有する第2の側壁マスクを形成する工程と、第1及び第2の芯材を除去する工程と、第1及び第2の側壁マスクをマスクとして被加工材12をエッチングすることにより、異なる幅を持つ第1及び第2のパターンを同時に形成する工程とを備える。

(もっと読む)

不揮発性半導体記憶装置の動作方法

【課題】制御部を増加せずにブロックサイズを小さくできる不揮発性半導体記憶装置の動作方法を提供する。

【解決手段】メモリストリングを有するメモリ部と、メモリ部を制御する制御部と、を備える不揮発性半導体記憶装置110の動作方法である。メモリストリングは、直列に接続された複数のトランジスタを含み、複数のトランジスタのうちの一部である第1グループGR1と、第1グループの隣りに接続された第1調整用トランジスタTr−AJと、調整用トランジスタの第1グループとは反対側に接続されたトランジスタを含む第2グループGR2と、を有する。制御部は、第1グループのトランジスタの閾値の書き換えを行ったのち、第1調整用トランジスタに、閾値の書き換えによって生じた第2グループのトランジスタの閾値の相対的な変動分を調整する第1調整用閾値を設定する制御を行う。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】安定した動作を実行可能な不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、複数のメモリストリング、選択トランジスタ、及びキャリア選択素子を備える。メモリストリングは、直列接続されたメモリトランジスタを含む。選択トランジスタは、メモリストリングの一端に一端を接続されている。キャリア選択素子は、選択トランジスタの他端に一端を接続されている。キャリア選択素子は、メモリトランジスタのボディを流れる多数キャリアを決定する。キャリア選択素子は、第3半導体層、金属層、第2ゲート絶縁層、及び第3導電層を備える。第3半導体層は、基板に対して垂直方向に延びる。金属層は、第3半導体層の上面から延びる。第3導電層は、第2ゲート絶縁層を介して、第3半導体層及び金属層を取り囲む。

(もっと読む)

記憶装置、集積回路装置及び電子機器

【課題】チップ面積や負荷容量の増加を抑止しながら、不揮発性メモリーセルのチャージトラップを低減することができる記憶装置、集積回路装置及び電子機器等を提供すること。

【解決手段】記憶装置は、電気的にデータの書き込み及び消去が可能な不揮発性メモリーセルM11、M12・・・と、トランジスターTNとを含む。不揮発性メモリーセルM11、M12・・・のワード線WS1とトランジスターTNのゲート電極GTとは、共通の導電配線PLにより形成される。導電配線PLには、ワード線WS1及びゲート電極GTに電圧を供給するためのコンタクトCNAが形成される。平面視において、コンタクトCNAと不揮発性メモリーセルM11、M12・・・との間の導電配線PLの経路において、トランジスターTNのチャネル領域が形成される。

(もっと読む)

半導体装置

【課題】記憶保持期間において、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体以外の半導体材料が用いられた第1のチャネル形成領域を有する第1のトランジスタ160と、第1のトランジスタ160の上方の、酸化物半導体材料が用いられた第2のチャネル形成領域を有する第2のトランジスタ162と、容量素子164と、を有し、第2のトランジスタ162の第2のソース電極または第2のドレイン電極の一方と、容量素子164の電極の一方とは、電気的に接続される。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセルトランジスタの特性が均一な不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】ボロンドープドシリコン層72を堆積させ、その上面にシリコン窒化層78を形成し、ノンドープドシリコン層73を堆積させ、その上面にシリコン窒化層79を形成する工程を繰り返すことにより、シリコン基板11上に積層体20を形成する。次に、積層体20に貫通ホール30aを形成し、その内部に犠牲材を埋め込み、積層体20にX方向に延びるスリット74を形成する。次に、スリット74内にエッチング水溶液を導入することにより、ノンドープドシリコン層73をウェットエッチングして除去する。次に、エッチング水溶液を除去し、ボロンドープドシリコン層72間及びスリット74内に絶縁材料を埋め込む。次に、貫通ホール内から犠牲材を除去し、内面上に電荷蓄積膜を形成し、内部にシリコンピラーを形成する。

(もっと読む)

半導体装置の製造方法

【課題】高速動作のために低電圧で相対的に大きな電流駆動力を必要とするMISFETと高耐圧を必要とするMISFETを有する半導体装置において、各素子を、それぞれの素子特性の向上を図りつつ簡素化した工程で製造する。

【解決手段】低耐圧MISFETのゲート電極4およびMONOSメモリのメモリゲート電極8のそれぞれの側壁にサイドウォールA、Bを形成する際、専用のマスクを用いず、低温下で堆積することのできる酸化膜をフォトレジスト膜が形成されたシリコン基板1上に形成し、ゲート電極4およびメモリゲート電極8のそれぞれの側壁に幅の違うサイドウォールA、Bを形成する。

(もっと読む)

半導体装置のパターン構造物及び半導体装置のパターン構造物の形成方法

【課題】半導体装置のパターン構造物及び半導体装置のパターン構造物の形成方法を提供すること。

【解決手段】半導体装置のパターン構造物は、延長ラインと延長ラインの端部に連結されるパッドとを具備する。パッドは、延長ラインの幅より広い幅を有することができる。パッドは、パッドの側部から延長する突出部を含むことができる。パターン構造物は、単純化された工程を通じて製造されることができ、微細パターンとパッドを含む多様な半導体装置に適用することができる。

(もっと読む)

半導体記憶装置

【課題】記憶素子間の干渉が少ない半導体記憶装置を提供する。

【解決手段】半導体記憶装置1において、シリコン基板11の上層部分の一部にSTI16を設け、シリコン基板11の上層部分をY方向に延びる複数本のアクティブエリアAAに区画する。そして、上下方向(Z方向)におけるアクティブエリアAAの中間部分27の幅Wmを、上部26の幅Wu及び下部28の幅Wlよりも細くする。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】垂直壁の貫通ホールが形成でき、また、貫通ホールがテーパ状となった場合においても上部と下部とでしきい値電圧特性が均一化でき、安定して動作する不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】基板11と、基板の主面11a上に設けられ、主面に対して垂直な第1方向に交互に積層された複数の電極膜WLと複数の電極間絶縁膜14とを有する積層構造体MLと、積層構造体を前記第1方向に貫通する半導体ピラーSPと、電極膜のそれぞれと半導体ピラーとの交差部に設けられた記憶部(記憶層48)と、を備える不揮発性半導体記憶装置が提供される。電極膜は、アモルファスシリコン及びポリシリコンの少なくともいずれかを含む。基板からの距離が近い第1領域RG1の電極膜に含まれる添加物の濃度は、第1領域よりも基板からの距離が遠い第2領域RG2の電極膜に含まれる添加物の濃度とは異なる。

(もっと読む)

半導体装置及びその製造方法

【課題】深さの異なる複数のコンタクトホールの底部径のばらつきを抑制する半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、複数の導電層WL1〜WL4が階段状に加工された階段構造部を有する積層体と、階段構造部を覆って設けられた層間絶縁層43と、層間絶縁層43を貫通し、それぞれが対応する各段の導電層WL1〜WL4に達して形成された複数のコンタクトホール61〜64の内部に設けられたコンタクト電極60とを備え、複数のコンタクトホール61〜64の底部の孔径は略同じであり、下段側の導電層に達するコンタクトホールは、上段側の導電層に達するコンタクトホールよりも深く、上端部の孔径が大きい。

(もっと読む)

半導体装置

【課題】メモリセル領域に隣接して配置された周辺回路の基板コンタクトプラグが高抵抗になるという不良を防止する。

【解決手段】メモリセル領域2に隣接し、第一および第二の周辺回路を有する周辺回路領域3と、第一の周辺回路に形成された第一の基板コンタクトプラグ16aと、第二の周辺回路に形成された第二の基板コンタクトプラグ16bと、第一および第二の基板コンタクトプラグに対応して半導体基板に形成されたシリサイド領域とを備え、メモリセル領域の端部から第一の周辺回路までの距離は、メモリセル領域の端部から第二の周辺回路までの距離より大きく、第一の基板コンタクトプラグの横断面形状は第二の基板コンタクトプラグの横断面形状より大きく構成した。

(もっと読む)

半導体装置の製造方法

【課題】フラッシュメモリと、精度が低くても高耐圧性が要求されるキャパシタと、耐圧性が低くても高精度が要求されるキャパシタとを備えた半導体装置を比較的少ない工程で製造できる半導体装置の製造方法を提供する。

【解決手段】半導体基板10上に形成されたシリコン膜13により、フラッシュメモリのフローティングゲートと高耐圧キャパシタの下部電極13bとを形成する。この場合、シリコン膜13中の不純物濃度を、フラッシュメモリに適した濃度とする。その後、半導体基板10に不純物をイオン注入して高精度キャパシタの下部電極となる高濃度不純物領域15を形成する際に、高耐圧キャパシタの下部電極13bに不純物を追加注入し、下部電極13bの不純物濃度を向上させる。次いで、高精度キャパシタの誘電体膜12を、増速酸化により形成する。

(もっと読む)

半導体記憶装置

【課題】チップサイズの増大を抑制でき、且つ読み出しマージンの低下を防止することが可能な半導体記憶装置を提供する。

【解決手段】第1導電型の第1のウェル12は、基板11内に形成されている。第2導電型の第2のウェル13は、第1のウェル12内に形成されている。複数のメモリセルMC、及び複数の第1、第2のビット線選択トランジスタ14e、14o、15e、15oは、第2のウェル13内に形成され、複数の第1、第2のビット線選択トランジスタ14e、14o、15e、15oは複数のビット線BLe、BLoの複数のメモリセルMCよりセンスアンプ17側に配置されている。

(もっと読む)

半導体装置

【課題】不揮発性メモリセルの面積を増大することなく、かつ、製造プロセスを変更することなく、不揮発性メモリセルのデータ書き込み速度およびデータ消去速度の向上を図ることのできる技術を提供する。

【解決手段】データ書き込み・消去用の容量部CWE、データ読み出し用のMIS・FETQRおよび容量部Cを互いに異なる位置に分離した状態で配置する。容量部Cの容量電極FGC2を覆う絶縁層6上にキャップ電極CAPを設けることにより、容量部Cは、容量電極FGC2とp型のウエルHPW1との間の容量およびキャップ電極CAPと容量電極FGC2との間の容量を加算した容量を有する。また、データ書き込み・消去用の容量部CWEにおけるデータの書き換えはチャネル全面のFNトンネル電流により行う。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】セルアレイ部の下層部分の電極を周辺回路部のトランジスタのゲート電極と同時に形成することができ、且つ、この電極の抵抗が低い半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体記憶装置1において、セルアレイ部CAにはバックゲート電極21を設け、周辺回路部SCには電界効果トランジスタ25のゲート電極22を設ける。バックゲート電極21及びゲート電極22は、下層側から順に、n型シリコン層15、金属シリサイド層16、p型シリコン層17が積層された3層構造の導電膜18により形成する。また、バックゲート電極21において、p型シリコン層17内にU字ピラー41の接続部材39を設ける。そして、コンタクトプラグ58c及び58eを、それぞれバックゲート電極21及びゲート電極22の金属シリサイド層16に接触させる。

(もっと読む)

1 - 20 / 121

[ Back to top ]