Fターム[5F101BD24]の内容

不揮発性半導体メモリ (42,765) | 素子構造 (12,113) | 組合せ (2,046) | CMOS構造 (117)

Fターム[5F101BD24]に分類される特許

1 - 20 / 117

半導体装置

【課題】メモリセルの動作を従来よりも高速化できる半導体装置を提供する。

【解決手段】フローティングゲートFGとコントロールゲートCG、第1導電型ソース13s及び第1導電型ドレイン13dを有する第1導電型MOSトランジスタ13と、前記フローティングゲートFGと前記コントロールゲートCG、第2導電型ソース14s及び第2導電型ドレイン14dを有する第2導電型MOSトランジスタ14と、前記第1導電型ドレイン13d及び前記第2導電型ドレイン14dに接続される第1のソース/ドレイン11bと、第2のソース/ドレイン11aと、ゲートを有する選択トランジスタ11と、前記第1導電型ソースに接続される第1電源線VpLと、前記第2導電型ソースに接続される第2電源線VnLと、前記選択トランジスタ11の第2のソース/ドレイン11aに接続されるビット線BLと、前記選択トランジスタ11のゲートに接続されるワード線WLと、を有する。

(もっと読む)

論理回路

【課題】安定した高速動作を実現しつつ、製造工程も簡素化することが可能な論理回路を提供すること。

【解決手段】この論理回路1は、バイアス電源とグラウンドとの間で直列に接続され、それぞれのゲート端子に入力電圧が印加される第1及び第2のFET2A,2Bを備える論理回路であって、第1及び第2のFET2A,2BのうちのFET2Aは、ゲート端子が接続されるゲート電極膜17と、半導体材料からなるチャネル層12と、ゲート電極膜17とチャネル層12との間に配置され、電荷を蓄積及び放出する電荷蓄積構造を含む電荷蓄積層16と、を有する。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する際に、信頼性の高い構成を提供する。

【解決手段】酸化物半導体層、第1の導電層及び第2の導電層の積層によって構成されるソース電極層又はドレイン電極層、ゲート絶縁層、及びゲート電極層が順に積層されたコプレナー型のトランジスタにおいて、該ゲート電極層は、該第1の導電層と該ゲート絶縁層を介して重畳し、該第2の導電層と前記ゲート絶縁層を介して非重畳とする。

(もっと読む)

半導体装置

【課題】酸化物半導体を含み、高速動作が可能なトランジスタを提供する。または、該トランジスタを含む信頼性の高い半導体装置を提供する。

【解決手段】下地絶縁層中に埋め込まれ、上面の少なくとも一部が下地絶縁層から露出した電極層上に、一対の低抵抗領域及びチャネル形成領域を含む酸化物半導体層を設け、電極層において、または、酸化物半導体層の低抵抗領域であって電極層と重畳する領域において、酸化物半導体層の上層に設けられる配線層との電気的な接続を行うトランジスタを提供する。

(もっと読む)

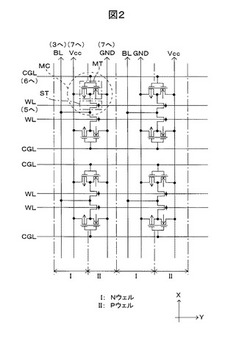

不揮発性半導体記憶装置

【課題】選択メモリセルトランジスタに電荷を蓄積する際の電圧を従来よりも自由に設定し得る不揮発性半導体記憶装置を提案する。

【解決手段】不揮発性半導体記憶装置1では、選択メモリセルトランジスタ115に電荷を蓄積させる際、電圧の高い書き込み禁止電圧をP型MOSトランジスタ9bから印加し、電圧の低い書き込み電圧をN型MOSトランジスタ15aから印加して、選択メモリセルトランジスタ115又は非選択メモリセルトランジスタ116へ電圧を印加する役割分担を、P型MOSトランジスタ9b及びN型MOSトランジスタ15aに分けたことで、P型MOSトランジスタ9b及びN型MOSトランジスタ15aそれぞれのゲート電圧やソース電圧を個別に調整でき、最終的にゲート基板間電圧を例えば4[V]等に設定し得る。

(もっと読む)

不揮発性プログラマブルロジックスイッチ

【課題】メモリの選択的な書き込みを行う際のパストランジスタのゲート絶縁膜の破壊を防ぐとともにパストランジスタのゲート絶縁膜を薄くすることを可能にし、かつメモリの微細化によって書き込み効率が損なわれない不揮発性プログラマブルロジックスイッチを提供する。

【解決手段】第1端子と、第2端子と、メモリ状態を制御する制御信号を受ける第3端子とを有する第1メモリと、ソース/ドレインの一方が第2端子に接続される第1トランジスタと、第1トランジスタのソース/ドレインの他方にゲートが接続される第2トランジスタとを備えた、第1セルおよび第2セルを有する。第1セルの第1メモリの第3端子と、第2セルの第1メモリの第3端子は共通に接続され、第1セルに書き込みを行う場合、第3端子が書き込み電源に接続され、第1セルの第1端子は接地電源に接続され、第2メモリの第1端子は書き込み防止電源に接続される。

(もっと読む)

二重フローティングゲート構造を有するトランジスタを備えた不揮発性メモリ

【課題】CMOS製造プロセスに用いることのできる材料を用いかつノイズマージンの広い不揮発性メモリを提供する。

【解決手段】本実施形態の不揮発性メモリによれば、第1および第2のPチャネルトランジスタはそれぞれ第1の半導体領域上に設けられ、第1の半導体領域上に、第1の絶縁膜と、第1のフローティングゲート、第2の絶縁膜、第2のフローティングゲート、第3の絶縁膜、および第1の制御ゲートが、この順序で積層された構造を有し、前記第1および第2のNチャネルトランジスタはそれぞれ第2の半導体領域上に設けられ、前記第2の半導体領域上に、第4の絶縁膜、第3のフローティングゲート、第5の絶縁膜、第4のフローティングゲート、第6の絶縁膜、および第2の制御ゲートがこの順序で積層された積層構造を有している。

(もっと読む)

メモリ回路

【課題】電源投入時における誤書き込みが発生しにくいメモリ回路を提供する。

【解決手段】メモリ回路10は、書き込み時のみにソース・ドレイン間に電圧を印加されて書き込まれる、書き込み用のPチャネル型不揮発性メモリ素子15と、コントロールゲート及びフローティングゲートがPチャネル型不揮発性メモリ素子15のコントロールゲート及びフローティングゲートとそれぞれ共通にされ、読み出し時のみにソース・ドレイン間に電圧を印加されて読み出される、読み出し用のNチャネル型不揮発性メモリ素子16と、を備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】特性を向上させる不揮発性メモリを有する半導体装置を提供する。

【解決手段】半導体装置を、制御ゲート電極CGと、制御ゲート電極CGと隣合うように配置されたメモリゲート電極MGと、絶縁膜3と、その内部に電荷蓄積部を有する絶縁膜5と、を有するよう構成する。このうち、メモリゲート電極MGは、絶縁膜5上に位置する第1シリコン領域6aと、第1シリコン領域6aの上方に位置する第2シリコン領域6bと、を有するシリコン膜よりなり、第2シリコン領域6bは、p型不純物を含有し、第1シリコン領域6aのp型不純物の濃度は、第2シリコン領域6bのp型不純物の濃度よりも低く構成する。

(もっと読む)

半導体装置

【課題】小型化が可能な不揮発性メモリを備えた半導体装置を提供する。

【解決手段】基板901上に画素と不揮発性メモリとを備え、不揮発性メモリは、基板901上に形成される半導体活性層と、半導体活性層上に形成される絶縁膜923と、絶縁膜923上に形成されるフローティングゲイト電極907と、フローティングゲイト電極907を酸化して得られる酸化膜908,915,922と、酸化膜908,915,922に接して形成されるコントロールゲイト電極929と、を備え、画素と不揮発性メモリとは、基板901上に一体形成される。

(もっと読む)

不揮発性プログラマブルロジックスイッチおよび半導体集積回路

【課題】回路サイズを減少させることを可能にする。

【解決手段】素子分離領域102によって分離された、隣接する第1導電型の第1半導体領域101aおよび第2導電型の第2半導体領域101cと、第1半導体領域101a上に設けられた不揮発性メモリセルトランジスタ10と、第2半導体領域101c上に設けられ、第1半導体領域101aに設けられた第1ドレイン領域10bと電気的に接続されたゲート電極20C2とを有するパストランジスタ20と、第1半導体領域101aに設けられ第1半導体領域に基板バイアスを印加する第1電極8と、第2半導体領域101cに設けられ第2半導体領域に基板バイアスを印加する第2電極9と、を備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板上に形成されたFETのソース側のエクステンション領域の抵抗値を低減し、半導体装置の動作速度を向上することができる技術を提供する。

【解決手段】ゲート電極4dの側壁に、ゲート電極4dのゲート長方向の幅が異なる第1サイドウォール6wおよび第2サイドウォール6nをそれぞれ形成する。これにより、第1サイドウォール6wおよび第2サイドウォール6nの形状によって第1サイドウォール6wおよび第2サイドウォール6nの下部に自己整合的に形成されるエクステンション領域37、38の半導体基板SBの上面の幅をそれぞれ異なる長さで形成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】高効率的に書き込みを行うことができる不揮発性半導体記憶装置を提供する。

【解決手段】直列接続された複数のメモリセルトランジスタMTと、メモリセルトランジスタの一端とソース線との間に接続された選択ゲートトランジスタST2と、メモリセルトランジスタの他端とビット線との間に接続された選択ゲートトランジスタST1と、ソース線に第1の電圧を印加し、ビット線に第1の電圧よりも高く且つ第1の電圧との差がトンネル絶縁膜のバリアハイトに対応する電圧よりも小さい第2の電圧を印加し、書き込み対象のメモリセルトランジスタMTとソース線との間に位置し、且つ書き込み対象のメモリセルトランジスタに隣接する隣接メモリセルトランジスタMTの導通状態を、他のメモリセルトランジスタMTの導通状態よりも弱くすることで書き込み対象のメモリセルトランジスタに書き込みを行う制御回路と、を具備する。

(もっと読む)

不揮発性半導体記憶装置

【課題】消去特性の変動が小さく、特性の安定した不揮発性半導体記憶装置を実現する。

【解決手段】不揮発性半導体記憶装置50は、第1導電型の半導体基板1上にゲート電極6bを有し第2導電型のMISFET5と、半導体基板1上の第2導電型第1ウェル3に設けられ、第1容量電極6cを有する第1MISキャパシタ15と、半導体基板1上の第2導電型第2ウェル4に設けられ、第2容量電極6aを有する第2MISキャパシタ21とを備える。ゲート電極6b、第1容量電極6c、第2容量電極6aが電気的に接続されてフローティングゲート6を構成する。第2MISキャパシタ21にて、第2ウェル4と、第2ウェル4上の部分の第2容量電極6aとがキャパシタ領域を構成する。第2容量電極6aは、キャパシタ領域が複数の分割キャパシタ領域に分割され、各分割キャパシタ領域の面積が変動してもその総面積は略一定となる平面形状及び配置を有する。

(もっと読む)

半導体装置

【課題】チップ面積を縮小しつつ、高信頼性を実現する半導体装置を提供する。

【解決手段】半導体装置は、第1、第2配線S1,S2を有する第1回路部210と、第3、第4配線S3、S4を有する第2回路部220と、それらの間に設けられ、第1回路部210から第2回路部220に向かう方向に直交する方向に沿って隣接する第1、第2トランジスタTR1、TR2を有する中間部230と、を備え、第1トランジスタTR1の一方の拡散層DA1の第1接続領CA1内の高濃度領域CAI1は第1配線S1に、他方の拡散層DB1は第3配線S3に接続される。第1接続領域CA1とゲートG01との距離は、第2接続領域CA2とゲートG02との距離よりも長い。第1トランジスタTR1の一方の拡散層DA1の第1接続領域CA1とゲートG01との間には、第1接続領域CA1よりも幅が狭い延在領域EA1が設けられる。

(もっと読む)

半導体集積回路装置の製造方法

【課題】共通ゲートを有する複数のトランジスタセルをアレー状に配置する構成を持つ不揮発性半導体集積回路装置において、STI領域のパターニング工程でのパターンの変形を防ぐ製造方法を提供する。

【解決手段】半導体メモリ等のメモリセルアレー等の露光において、矩形形状のSTI溝領域エッチング用単位開口を行列状に配置したSTI溝領域エッチング用単位開口群をネガ型レジスト膜28上に露光するに際して、列方向に延びる第1の線状開口群を有する第1の光学マスクを用いた第1の露光ステップと、行方向に延びる第2の線状開口群を有する第2の光学マスクを用いた第2の露光ステップとを含む多重露光を適用する。直行する2方向において、それぞれの方向に対してマスクを用いて露光を行うことで、矩形形状48の端部における近接効果を回避することができ、矩形形状48の端部が丸みを帯びるのを回避することができる。

(もっと読む)

昇圧回路および半導体メモリ

【課題】 高電圧の生成効率を向上し、消費電力を削減する。

【解決手段】 昇圧回路は、第1ノードおよび第2ノードの間に第3ノードを介して直列に接続された第1および第2キャパシタと、第4ノードおよび第5ノードの間に第6ノードを介して直列に接続された第3および第4キャパシタと、第4ノードが第1レベルに設定されているときに、第3ノードを電源線に接続する第1スイッチと、第1ノードが第1レベルに設定されているときに、第6ノードを電源線に接続する第2スイッチと、第6ノードの電荷を第2ノードに転送する第3スイッチと、第3ノードの電荷を第5ノードに転送する第4スイッチと、第2ノードを電圧線に接続する第5スイッチと、第5ノードを電圧線に接続する第6スイッチとを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】メモリセルアレイ領域と周辺回路領域との間に生じる層間絶縁膜の段差を解消し、歩留まりの向上を図ることができる半導体装置を提供すること。

【解決手段】半導体基板1上で素子分離用絶縁膜2a、2bによって素子分離された複数の第1の素子10が形成された第1の領域4と、半導体基板1上で第1の領域4に隣接して配されるとともに、素子分離用絶縁膜2b、2cによって素子分離された複数の第2の素子20が形成され、第2の素子20の高さが第1の素子10の高さよりも低い第2の領域5と、第2の領域5にある素子分離用絶縁膜2b、2cの少なくとも一部の領域上に配設されたダミー絶縁膜6c、6dと、第1の領域4及び第2の領域5にわたって形成された層間絶縁膜7と、を備える。

(もっと読む)

不揮発性半導体集積回路装置

【課題】不揮発性半導体集積回路装置のチップサイズを縮小させる。

【解決手段】シリコン基板上に隣り合って配置された第1および第2ゲート電極とそれらの側方下部のシリコン基板に形成された一対のソース・ドレイン領域とを有し、第2ゲート電極とシリコン基板との間に配置された第2ゲート絶縁膜に電荷を蓄えることで情報を記憶するメモリセルにおいて、メモリセルの消去動作時には、消去非選択セルの第1ゲート電極に正電圧を印加する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】動作信頼性を向上させる不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】基板100上に形成された蓄積層105と蓄積層上に形成された制御ゲート電極107を備えた第1電極MTと、基板100上に形成された第2電極ST2及び第3電極ST2と、ゲート長方向に沿って対向する第2電極と第3電極ST2との側壁及び基板100上に形成された第2絶縁膜112と、第2、第3ゲート電極ST2間に埋設された第1絶縁膜113と、第2電極ST2及び第1電極MT間に埋設された第2絶縁膜109、110と、第1ゲート電極MT、第2ゲート電極ST2、第3ゲート電極ST2、及び第1、第2絶縁膜上113、112にそれぞれ形成され、且つ第1絶縁膜113における水素原子の拡散を防止する第3絶縁膜114とを具備する。

(もっと読む)

1 - 20 / 117

[ Back to top ]