国際特許分類[H01L21/8246]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | 1つの共通基板内または上に形成される複数の固体構成部品または集積回路からなる装置の製造または処理 (31,691) | 複数の別個の装置に基板を分割することによるもの (31,691) | それぞれが複数の構成部品からなる装置,例.集積回路の製造 (31,684) | 基板がシリコン技術を用いる半導体であるもの (27,844) | 電界効果技術 (17,660) | MIS技術 (17,448) | メモリ構造 (10,964) | リードオンリーメモリ構造 (7,638)

国際特許分類[H01L21/8246]の下位に属する分類

電気的にプログラムできるもの (4,399)

国際特許分類[H01L21/8246]に分類される特許

1 - 10 / 3,239

プラズマ処理方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

半導体装置の製造方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

液体噴射ヘッド及び液体噴射装置並びに圧電素子

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

磁気抵抗効果素子、および磁気ランダムアクセスメモリ

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

磁気抵抗素子の製造方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

液体噴射ヘッド、液体噴射装置及び圧電素子

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

半導体装置の製造方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

ニッケル酸ランタン膜形成用組成物及びその製造方法、ニッケル酸ランタン膜の製造方法、圧電素子の製造方法、液体噴射ヘッドの製造方法、並びに液体噴射装置の製造方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

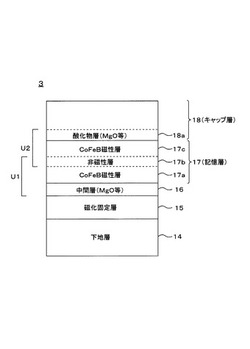

記憶素子、記憶装置

【課題】熱安定性を確保して特性バランスに優れた記憶素子を実現する。

【解決手段】記憶素子は、膜面に垂直な磁化を有し、情報に対応して磁化の向きが変化される記憶層と、上記記憶層に記憶された情報の基準となる膜面に垂直な磁化を有する磁化固定層と、上記記憶層と上記磁化固定層の間に設けられる非磁性体による中間層とを有する層構造を備える。その上で、上記層構造の積層方向に電流を流すことで記憶層の磁化の向きが変化して、記憶層に対して情報の記録が行われる。そして記憶層は、Co−Fe−B磁性層と、少なくとも1つの非磁性層を有し、酸化物層、Co−Fe−B磁性層、非磁性層が順に積層された積層構造が形成されているようにする。

(もっと読む)

半導体装置とその製造方法

【課題】ゲート高さが低いため製造容易で、ゲート−コンタクト間の容量を抑制し、ゲート−コンタクト間の短絡を抑制した半導体装置を提供する。

【解決手段】半導体装置の製造方法は基板上にFin型半導体層を形成する。Fin型半導体層に交差するダミーゲートが形成される。Fin型半導体層にソースおよびドレインが形成される。ダミーゲート上に層間絶縁膜を堆積した後、ダミーゲートの上面を露出させる。ダミーゲートを除去してゲートトレンチを形成する。ゲートトレンチ内のFin型半導体層の上部をリセスする。ゲートトレンチ内のFin型半導体層の表面にゲート絶縁膜を形成する。ゲート電極をゲートトレンチ内に充填する。ゲート電極をエッチングバックすることによってゲート電極を形成する。ゲート電極の上面の高さはソースおよびドレインにおけるFin型半導体層の上面の高さ以下かつゲートトレンチ内のFin型半導体層の上面の高さ以上である。

(もっと読む)

1 - 10 / 3,239

[ Back to top ]