国際特許分類[H01L21/8246]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | 1つの共通基板内または上に形成される複数の固体構成部品または集積回路からなる装置の製造または処理 (31,691) | 複数の別個の装置に基板を分割することによるもの (31,691) | それぞれが複数の構成部品からなる装置,例.集積回路の製造 (31,684) | 基板がシリコン技術を用いる半導体であるもの (27,844) | 電界効果技術 (17,660) | MIS技術 (17,448) | メモリ構造 (10,964) | リードオンリーメモリ構造 (7,638)

国際特許分類[H01L21/8246]の下位に属する分類

電気的にプログラムできるもの (4,399)

国際特許分類[H01L21/8246]に分類される特許

3,231 - 3,239 / 3,239

FETベースの磁気ランダム・アクセス・メモリ・デバイス用の自己整列型導電線およびこれを形成する方法

【課題】下部メタライズ線(302)に導電的に結合された横方向の金属ストラップ(326)を含む、電界効果トランジスタ(FET)ベースの磁気ランダム・アクセス・メモリ(MRAM)デバイス用の導電線構造を提供すること。

【解決手段】金属ストラップ(326)上に磁気トンネル接合(MTJ)スタック(316)が形成され、MTJスタック(316)を覆って金属シールド(324)が形成され、金属シールド(324)は金属ストラップ(326)に対して自己整列される。上部メタライズ線(332)は金属シールド(324)に導電的に結合され、金属シールド(324)は上部メタライズ線(332)の形成時にエッチ・ストップとして働く。

(もっと読む)

三次元集積回路構造及びこれを作る方法

垂直方向の半導体装置は、電気装置そして/または相互接続を含む分離して作られた基板に付加される。多くの垂直方向の半導体装置は物理的に互いに分離され、そして同一半導体本体又は半導体基板内には配置されない。多くの垂直方向の半導体装置は取り付けられた後に個別のドープされたスタック構造を生成するため、エッチングされた数個のドーピングされた半導体領域を含む薄い層として分離して作られた基板へ付加される。あるいは多くの垂直方向の半導体装置が分離して作られた基板に取り付けるのに先立ち製作される。ドープされたスタック構造は、ダイオードキャパシタ、n‐MOSFET、p‐MOSFET、バイポーラトランジスタ、及び浮遊ゲートトランジスタのベースを形成する。強誘電体メモリー装置、強磁性体メモリー装置、カルコゲニド位相変更装置が分離して作られた基板と連結して使用するために、堆積可能なアッド‐オン層に形成される。堆積可能なアッド‐オン層は相互接続ラインを含む。

(もっと読む)

(もっと読む)

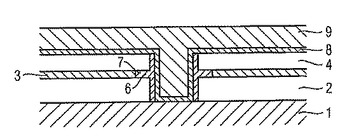

デバイス内にバリア層を有するコンタクトホールを形成する方法及び得られるデバイス

デバイスの下層(2)にコンタクトを形成する方法は、コンタクトホール(5)を形成するステップと、デバイスのコンタクトホール内にバリア材からなるコンタクトホールバリア層(7)を形成するステップと、コンタクトホールの底面のコンタクトホールバリア層をエッチングするステップと、コンタクトホール内にライナ材(8)を堆積するステップと、コンタクトホールに導電性材料(9)を充填するステップとを有する。半導体、受動素子、キャパシタ又はFeRAMなどのデバイスが上記方法に従って形成される。コンタクトホールの側壁にあるコンタクトホールバリア層(7)が、水素及び/又は酸素の側方拡散を抑制する。コンタクトホールバリア層は、ウェットエッチングプロセスによって生じる既存のバリア層(3)内のボイド(6)を充填するために上記プロセス後に、又は既存のバリア層への損傷を抑制するために上記プロセス前に行うことができる。

(もっと読む)

(もっと読む)

複合磁気フリー層を有する磁気エレクトロニクス情報デバイス

磁気エレクトロニクス情報デバイス(12)は、2つの多層構造(24,26)及び該2つの多層構造の間に配置されたスペーサ層(28)を備えている。各多層構造は、2つの磁気副層(38,40及び44,46)と、該2つの磁気副層の間に配置されたスペーサ層(42,48)とを有している。2つの磁気副層の間に配置されたスペーサ層は、飽和領域によって定量化される反強磁性交換結合を提供する。2つの多層構造の間に配置されたスペーサ層は、前記第1飽和領域よりも小さい他の飽和領域によって定量化される第2反強磁性交換結合を提供する。  (もっと読む)

(もっと読む)

MRAMセルのための磁気異方性を誘導するための斜め堆積

表面を有する基板を提供するステップと、前記基板上に合成磁気モーメントベクトルを有する第1磁気領域(17)を堆積するステップと、前記第1磁気領域上に電気絶縁材料(16)を堆積するステップと、前記電気絶縁材料上に第2磁気領域(115)を堆積するステップを備えた磁気抵抗トンネル接合セルを製造する方法であって、前記第1磁気領域および第2磁気領域の一方の少なくとも一部分が、前記基板の表面に直交する方向に対して非ゼロの堆積角で該領域を堆積することによって形成されて誘導異方性を作る方法。  (もっと読む)

(もっと読む)

レーザ移動を用いて感熱基板上に移植した磁気ランダム・アクセス・メモリ(MRAM)デバイスおよびこれを製造する方法

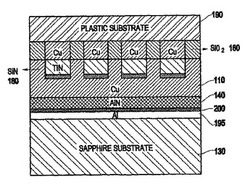

【課題】 ポリマおよびプラスチック等の低温基板上に磁気メモリ・デバイスを製造する方法を提供する。

【解決手段】 低温基板上に磁気メモリ・デバイス(およびその結果として生じる構造)を形成する方法は、メモリ・デバイスを、分解可能な材料層で被覆された透明基板上に形成し、所定の高圧を生成させる急速加熱を施すステップと、メモリ・デバイスを低温基板に移動するステップと、を含む。

(もっと読む)

1T‐nメモリセル積層構造体

本発明は、クロスポイントと1T‐1セルとの双方の設計に基づくある種の利点を導入するためのメモリ技術及びメモリアレイに関する新規な変更に関する。これらの設計のある特徴を組み合わせることにより、1T‐1セル設計における読出し時間の高速化及び信号対雑音比の増大と、クロスポイント設計における高記録密度化との双方が達成される。そのために、単一のアクセストランジスタ16を用いて、“Z”軸方向に配置された複数のメモリアレイ層で垂直方向に互いに上下に積み重ねうる多重メモリセルを読出すようにする。  (もっと読む)

(もっと読む)

半導体記憶装置

【課題】本発明は、データの読み出しを行うメモリセル周辺のセルデータやチップ上の位置によってセンスアンプの電圧マージンが低下することを防止することを特徴とする。

【解決手段】メモリ回路の1つのブロック内には複数の本体セルアレイ21、ダミーセルアレイ22、バイアス回路16、行デコーダ18、データ検出回路を構成するセンスアンプ23、基準電圧回路24が設けられる。上記本体セルアレイ21及びダミーセルアレイ22にはバイアス回路16で発生される直流バイアス電圧PRが供給される。データ検出回路を構成するセンスアンプ23は、データの読み出し時に本体セルアレイ21内の列線に対して所定のバイアス電圧SAINを供給してデータを検出する。基準電圧回路24は、ダミーセルアレイ22に所定のバイアス電圧REFINを供給することによって、上記センスアンプ23でデータを検出する際に使用される比較用基準電圧VREFを発生する。

(もっと読む)

半導体装置の製造方法

3,231 - 3,239 / 3,239

[ Back to top ]