Fターム[5F083LA06]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | アドレスバッファ回路 (155)

Fターム[5F083LA06]に分類される特許

1 - 20 / 155

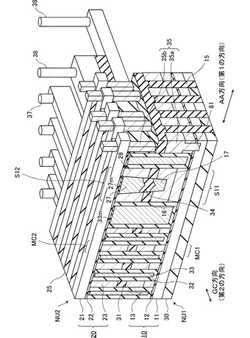

不揮発性半導体記憶装置及びその製造方法

【課題】制御性の高い不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、第1のメモリセルアレイ層と、第1のメモリセルアレイ層の上に形成された第1の絶縁層と、第1の絶縁層の上に形成された第2のメモリセルアレイ層と、第1の絶縁層を介して上下に位置する第1及び第2の浮遊ゲートの第1の方向の両側面にゲート間絶縁層を介して形成され、第1の方向と直交する第2の方向に延びる制御ゲートと、第1の絶縁層を介して上下に位置する第1及び第2の選択ゲートの第1の方向の両側面にゲート間絶縁層を介して形成され、第2の方向に延び、第1及び第2の半導体層並びに第1及び第2のゲート絶縁層と共に補助トランジスタを形成する補助ゲートとを備える。

(もっと読む)

半導体装置

【課題】

実施形態は、解析が簡便な半導体装置を提供する。

【解決手段】

本実施形態の半導体装置は、内部信号を伝送可能な第1配線101と、第1配線101

と電気的に接続された測定電極100と、測定電極100と隣接するように配置され、内

部信号を計測するときに接地電位VSSが印加され、内部信号を計測する以外のときに所

望の電圧が印加されたダミー電極102,103とを備える。

例えば、測定電極100は、環状に形成されており、ダミー電極は、第1電極102と

第2電極103とを有し、第1電極102は、測定電極100の内側に形成された空間に

隣接するように配置され、第2電極103は、測定電極100の外側に隣接するように配

置される。

(もっと読む)

抵抗変化型不揮発性記憶素子の書き込み方法および抵抗変化型不揮発性記憶装置

【課題】書き込み動作の安定性および信頼性を向上した抵抗変化型不揮発性記憶素子の書き込み方法を提供する。

【解決手段】抵抗変化素子を含むメモリセルに対して電圧パルスを印加することにより、抵抗変化素子を、印加される電圧パルスの極性によって第1の抵抗状態と第2の抵抗状態とを可逆的に変化させる書き込み方法であって、抵抗変化素子を第2の抵抗状態から第1の抵抗状態に変化せしめる時に、抵抗変化素子に対して、第2の電圧パルス(VL)よりも電圧の絶対値が小さく、かつ、第1の電圧パルス(VH)と極性が異なる第1の抵抗化プレ電圧パルス(VLpr)を印加する第1ステップと、その後、第1の電圧パルス(VH)を印加する第2ステップとを含む第1の抵抗状態化ステップを含む。

(もっと読む)

不揮発性半導体記憶装置

【課題】正確に書き込み動作を行うことができる不揮発性半導体記憶装置を提供する。

【解決手段】

複数の素子分離絶縁膜は、半導体層中に形成され、第1方向を長手方向とする。複数の素子形成領域は、素子分離絶縁膜により分離して形成される。素子形成領域にはメモリストリングが形成される。複数の素子形成領域群が素子形成領域により構成される。メモリセルアレイは、第1方向と直交する第2方向において、前記素子形成領域群の間隔が前記素子形成領域群の中の前記素子形成領域の間隔より大きくされている。制御回路は、前記メモリセルアレイに対する書き込み動作を、前記素子形成領域群ごとに実行する。

(もっと読む)

半導体記憶装置

【課題】メモリセルアレイと入出力バッファ間の遅延の最大値を抑制し高速に入出力動作が行える半導体記憶装置を提供する。

【解決手段】複数のメモリセルアレイが配置されたメモリセルアレイ部と、外部入出力回路が配置された周辺回路部と、複数のメモリセルアレイと周辺回路部とを接続する内部バス4と、を備え、周辺回路部は、複数の外部入出力バッファ23と、メモリセルアレイとの間で内部バスを並列に入出力するデータと複数の外部入出力バッファを直列に入出力するデータとを相互に変換する複数のバスインターフェース回路24と、を備え、複数のバスインターフェース回路間の距離d1が、複数の外部入出力バッファ間の距離d2及び内部バスの配線幅の最大値d3より狭くなるように、複数のバスインターフェース回路24は、内部バス4と複数の外部入出力バッファとの間にまとめて配置されている。

(もっと読む)

半導体記憶装置

【課題】 ビット線選択回路の小型化を図るとともにビット線の駆動時間を高速に行うことができる半導体記憶装置を提供する。

【解決手段】 フラッシュメモリ10は、セルユニットNUが行列状に複数配置されたメモリアレイ100と、セルユニットNUに接続されたビット線を選択するビット線選択回路200とを有する。ビット線選択回路200は、偶数ビット線GBL_e、奇数ビット線GBL_oをセンス回路に選択的に接続するための選択トランジスタSEL_e、SEL_o、BLSを含む第1の選択部210と、偶数ビット線GBL_eおよび奇数ビット線GBL_oに選択的にバイアス電圧を印加するためのバイアストランジスタYSEL_e、YSEL_oとを含む第2の選択部220とを有する。第2の選択部220のバイアストランジスタYSEL_e、YSEL_oは、記憶素子と共通のウエル内に形成される。

(もっと読む)

縦構造キャパシタを備える半導体装置

【課題】縦構造キャパシタの剥離を防止し、チップサイズの増加を抑制した半導体装置を提供する。

【解決手段】半導体装置には、第1の回路の機能素子として使用される第1の縦構造キャパシタと、第2の回路の機能素子として使用され、第1の縦構造キャパシタよりも容量値の大きい第2の縦構造キャパシタと、が含まれている。半導体装置では、第1の縦構造キャパシタを、第2の縦構造キャパシタに隣接、又は、包含させるようにレイアウトする。

(もっと読む)

半導体装置

【課題】緻密で高耐圧な絶縁膜を提供することを目的とする。

【解決手段】基板上に半導体膜を有し、半導体膜上に第1の絶縁膜を有し、第1の絶縁膜上に導電膜を有し、導電膜上に第2の絶縁膜を有し、第1の絶縁膜は、第2の絶縁膜よりも緻密であり、第1の絶縁膜は、珪素と、酸素と、窒素とを有する。第1の絶縁膜は、希ガスを有し、その膜厚は、1nm以上100nm以下である。このような第1の絶縁膜はゲート絶縁膜として機能させる。

(もっと読む)

半導体記憶装置

【課題】3次元型の半導体記憶装置のパフォーマンスを向上させる。

【解決手段】実施形態によれば、半導体記憶装置は、半導体基板と、半導体基板上に設けられ、積層された複数のメモリセルを含む複数のメモリユニットと、カラム方向に配列された複数のメモリユニット上に複数本形成されたビット線とを備え、複数のビット線のロウ方向の配列ピッチは、メモリユニットのロウ方向の配列ピッチよりも小さく、カラム方向に配列された各メモリユニットの端部は、複数本形成されたビット線のいずれか1つに接続される。

(もっと読む)

半導体装置の駆動方法

【課題】半導体装置の駆動方法を提供する。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ、該トランジスタと異なる半導体材料を用いた読み出し用のトランジスタ及び容量素子を含む不揮発性のメモリセルを有する半導体装置を提供する。メモリセルへの書き込みは、書き込み用トランジスタをオン状態として、書き込み用トランジスタのソース電極と、容量素子の電極の一方と、読み出し用トランジスタのゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタをオフ状態として、ノードに所定量の電位を保持させることで行う。メモリセルの読み出しは、ビット線にプリチャージ電位を供給した後ビット線への電位の供給を止め、ビット線の電位がプリチャージ電位に保たれるか、または電位が下がるか、により行う。

(もっと読む)

半導体記憶装置

【課題】データの読み出し速度を向上する。

【解決手段】半導体記憶装置1は、メモリセルアレー1aと、コラム線1bと、第1および第2のデータ線1d,1eと、データの読み出し時には、コラム線1bに第1および第2のデータ線1d,1eの一方を選択して接続し、データの書き込み時には、コラム線1bに第1および第2のデータ線1d,1eを接続するスイッチ1cと、第1および第2のデータ線1d,1eに接続された読み出し回路1fと、第1および第2のデータ線1d,1eに接続された書き込み回路1gと、を有する。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置の集積化を図る。

【解決手段】実施形態によれば、半導体記憶装置は、半導体基板と半導体基板上に設けられ、積層された複数のメモリセルを含むメモリセルアレイと、複数のメモリセルと電気的に接続されて平行に配列された複数のビット線と、ビット線接続配線を介してビット線と接続された複数のセンスアンプとを備える。ビット線接続配線は、隣接するN(Nは2以上の整数)本ごとに1つのグループとする。センスアンプは、ビット線接続配線が延びる第1方向にはNよりも小さい数で、且つ前記第1方向と交差する第2方向には前記グループ間のピッチよりも小さいピッチで配列されている。

(もっと読む)

可変抵抗素子のフォーミング処理方法および不揮発性半導体記憶装置

【課題】 パルスフォーミングと同程度の短時間で、スイッチング動作時の書き換え電流がDCフォーミングで達成される書き換え電流程度に抑えることのできる可変抵抗素子のフォーミング処理方法を提供する。

【解決手段】

可変抵抗素子に電圧パルスを印加して、製造直後の初期高抵抗状態にある可変抵抗素子をスイッチング動作が可能な可変抵抗状態に変化させるフォーミング処理が、可変抵抗素子が低抵抗化する閾値電圧より低い電圧振幅の第1パルスを可変抵抗素子の両電極間に印加する第1ステップと、第1ステップの後に、当該第1パルスと同極性であって閾値電圧以上の電圧振幅の第2パルスを可変抵抗素子の両電極間に印加する第2ステップとを含んでなる。

(もっと読む)

不揮発性半導体記憶装置

【課題】 BiCSメモリのような積層型メモリの書き込み動作を高速化することが可能な不揮発性半導体記憶装置を提供する。

【解決手段】 積層型のメモリセル構造を有する不揮発性半導体記憶装置であって、半導体基板上に、複数のメモリセルを積層してなるストリングを複数個配置したメモリセルアレイ11と、メモリセルアレイ11の任意のストリングをサンプルストリングとして選択し、該選択したサンプルストリングに対してデータの書き込みを行う回路12,14,16,30と、サンプルストリングの各メモリセルに対する書き込み回数をレイヤー毎に保持する書き込み回数記憶部31と、記憶部31に記憶されたレイヤー毎の書き込みパルス数を同一レイヤーの他のストリングのメモリセルの書き込み電圧の初期値に反映させる回路33とを備えている。

(もっと読む)

多値ROMセル及び半導体装置

【課題】集積度が高く、製造ばらつきの影響が小さく、製造歩留まりの高い多値ROMセルを提供する。

【解決手段】多値ROMセルは、ROMセルトランジスタTrと、複数のビット線BT1〜BT3と、第1金属配線31〜44とを具備している。ROMセルトランジスタTrは、基板表面の領域に設けられている。複数のビット線BT1〜BT3は、基板表面の上方に設けられ、Y方向に伸び、Z方向に並んで配置されている。第1金属配線31〜44は、ROMセルトランジスタTrのソース・ドレイン22の一方に接続され、複数のビット線BT1〜BT3の各々の近傍にまで連なる。第1金属配線31〜44は、複数のビット線BT1〜BT3のうちのいずれかに接続されているか、又は、いずれにも接続されていない。

(もっと読む)

半導体装置、及び半導体装置の制御方法。

【課題】簡便な半導体装置の評価試験を実現する。

【解決手段】半導体装置10は、それぞれ内部信号MAを生成する第1及び第2のコアチップCC0,CC1を備え、第1及び第2のコアチップCC0,CC1のそれぞれに、貫通電極を介して他方のコアチップとスパイラル接続された第2及び第3のノードN2,N3を設け、この第2及び第3のノードN2,N3を介して、観測対象の内部信号MAを外部に出力することを技術思想とするものである。こうして出力される複数の内部信号MAを外部のテスター等によって観測することで、各コアチップの評価試験を並列に行える。

(もっと読む)

抵抗変化型不揮発性メモリセルおよび抵抗変化型不揮発性記憶装置

【課題】電流制御素子が破壊されにくい、抵抗変化型不揮発性メモリセルおよび抵抗変化型不揮発性記憶装置を提供する。

【解決手段】極性の異なる電気的信号を印加することにより抵抗値の異なる複数の抵抗状態の間を可逆的に遷移する抵抗変化素子103と、抵抗変化素子103に直列に接続し、所定の印加電圧の範囲において印加電圧の絶対値が大きくなるにしたがい電圧電流曲線の傾きが大きくなる非線形の電圧電流特性を有する電流制御素子104と、層間絶縁層108、109、110を貫通するホールの内部に形成され、抵抗変化素子103もしくは電流制御素子104の少なくとも一方に接触し、かつ、負荷抵抗部131A、131B、131Cを有する、プラグ105,106,107と、を備える。

(もっと読む)

半導体装置

【課題】積層型の半導体装置においてリードデータの有効幅(ウィンドウ幅)を十分に確保する。

【解決手段】積層された複数のコアチップCC0〜CC7と、コアチップを制御するインターフェースチップIFとを備える。コアチップのそれぞれは、メモリセルアレイ70と、データ用の貫通電極TSV1と、メモリセルアレイ70から読み出されたリードデータをデータ用の貫通電極TSV1に出力する出力回路RBUFOとを備える。コアチップにそれぞれ設けられたデータ用の貫通電極TSV1は互いに共通接続され、コアチップにそれぞれ設けられた出力回路RBUFOはインターフェースチップIFより供給されるリードクロック信号RCLKDDに応答して活性化される。これにより、各コアチップの動作速度にばらつきが存在する場合であってもデータバス上でリードデータの競合が生じることがない。

(もっと読む)

NAND型不揮発性メモリのデータ消去方法

【課題】NAND型不揮発性メモリを提供する。

【解決手段】ビット線と、ソース線と、複数の不揮発性メモリが直列に接続されたNAND型セルと、選択トランジスタと、を有し、不揮発性メモリは、第1の絶縁膜を介した半導体上の電荷蓄積層と、第2の絶縁膜を介した電荷蓄積層上の制御ゲートと、を有し、NAND型セルの一方の端子は、選択トランジスタを介して、ビット線に接続され、NAND型セルの他方の端子は、ソース線に接続されたNAND型不揮発性メモリであって、第1の絶縁膜は、半導体に酸素雰囲気で高密度プラズマ処理を行った後、窒素雰囲気で高密度プラズマ処理を行うことで形成されるNAND型不揮発性メモリ。

(もっと読む)

抵抗変化メモリ

【課題】抵抗変化素子の低抵抗状態の抵抗値のばらつきを防止する。

【解決手段】実施形態に係わる抵抗変化メモリのメモリセルは、直列接続される抵抗変化素子RW及び積層構造Cを備える。抵抗変化素子RWを第1の抵抗値からそれよりも低い第2の抵抗値に変化させる第1の動作において、メモリセルMCに第1の電圧パルスを印加する。第1の電圧パルスの振幅は、積層構造Cがキャパシタとして機能する第1の電圧領域内にあり、第1の電圧パルスは、Ron×C < T-lead < Roff×C、 Ron×C < T-trailを満たす。但し、T-leadは、第1の電圧パルスの立ち上がり時間[sec]であり、T-trailは、第1の電圧パルスの立ち下り時間[sec]であり、Roffは、第1の抵抗値[Ω]であり、Ronは、第2の抵抗値[Ω]であり、Cは、キャパシタの容量[F]である。

(もっと読む)

1 - 20 / 155

[ Back to top ]