Fターム[5F101BA02]の内容

不揮発性半導体メモリ (42,765) | 電荷蓄積機構 (9,664) | FG型 (6,485) | FG配置 (488)

Fターム[5F101BA02]の下位に属するFターム

Fターム[5F101BA02]に分類される特許

1 - 20 / 151

不揮発性半導体記憶装置及びその製造方法

【課題】製造の容易な不揮発性半導体記憶装置およびその製造方法を提供する。

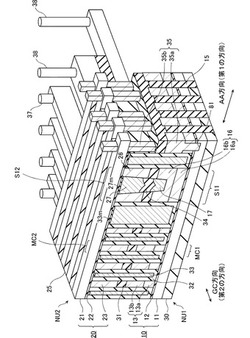

【解決手段】不揮発性半導体記憶装置は、第1のメモリセルアレイ層と、第1のメモリセルアレイ層の上に形成された第1の絶縁層と、第2のメモリセルを具備する第2のNANDセルユニットを有する第2のメモリセルアレイ層と、第1の絶縁層を介して上下に位置する第1及び第2の浮遊ゲートの第1の方向の両側面にゲート間絶縁層を介して形成され、第1の方向と直交する第2の方向に延びる制御ゲートと、第1のNANDセルユニットの両端に位置し、第1の浮遊ゲートと同層に形成され、第1の半導体層と接続される下部コンタクトと、第2のNANDセルユニットの両端に位置し、第2の半導体層と下部コンタクトとを接続する上部コンタクトとを備える。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】制御性の高い不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、第1のメモリセルアレイ層と、第1のメモリセルアレイ層の上に形成された第1の絶縁層と、第1の絶縁層の上に形成された第2のメモリセルアレイ層と、第1の絶縁層を介して上下に位置する第1及び第2の浮遊ゲートの第1の方向の両側面にゲート間絶縁層を介して形成され、第1の方向と直交する第2の方向に延びる制御ゲートと、第1の絶縁層を介して上下に位置する第1及び第2の選択ゲートの第1の方向の両側面にゲート間絶縁層を介して形成され、第2の方向に延び、第1及び第2の半導体層並びに第1及び第2のゲート絶縁層と共に補助トランジスタを形成する補助ゲートとを備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】 不揮発性半導体記憶装置の書き込み特性を向上させることができる。また、不揮発性半導体記憶装置の隣接素子間の干渉を抑制することができる。

【解決手段】本発明の不揮発性半導体記憶装置は、半導体基板と、前記半導体基板の表面内に、チャネル領域を挟んで互いに離間して設けられたソース領域及びドレイン領域と、前記チャネル領域上に設けられたトンネル絶縁膜と、前記トンネル絶縁膜上に設けられた絶縁性電荷蓄積層と、前記絶縁性電荷蓄積層上に設けられた両側部に絶縁層が設けられた導電性電荷蓄積層と、前記導電性電荷蓄積層上に設けられた層間絶縁膜と、前記層間絶縁膜上に設けられた制御ゲートとを備えている。

(もっと読む)

メモリ用シフトレジスタ及びその製造方法

【課題】大容量で、信頼性が高く、少ない工程数で製造可能なメモリ用シフトレジスタを提供する。

【解決手段】一の実施形態によれば、メモリ用シフトレジスタは、基板の主面に平行な第1方向に延び、前記第1方向に垂直な第2方向に向かい合う第1及び第2の制御電極を備える。さらに、前記レジスタは、前記第1及び第2の制御電極間において、前記第1の制御電極側に一列に設けられた複数の第1の浮遊電極を備える。さらに、前記レジスタは、前記第1及び第2の制御電極間において、前記第2の制御電極側に一列に設けられた複数の第2の浮遊電極を備える。さらに、前記第1及び第2の浮遊電極の各々は、前記第1方向に垂直な平面に対し、鏡面非対称な平面形状を有する。

(もっと読む)

メモリ回路

【課題】電源投入時における誤書き込みが発生しにくいメモリ回路を提供する。

【解決手段】メモリ回路10は、書き込み時のみにソース・ドレイン間に電圧を印加されて書き込まれる、書き込み用のPチャネル型不揮発性メモリ素子15と、コントロールゲート及びフローティングゲートがPチャネル型不揮発性メモリ素子15のコントロールゲート及びフローティングゲートとそれぞれ共通にされ、読み出し時のみにソース・ドレイン間に電圧を印加されて読み出される、読み出し用のNチャネル型不揮発性メモリ素子16と、を備える。

(もっと読む)

アプリケーション回路及び半導体デバイスの動作方法

【課題】バッテリレス電子タイマに適用される半導体デバイス、及びその動作方法とアプリケーション回路を提供する。

【解決手段】半導体デバイス600は、第1導電型半導体基板と、ゲート誘電層と、フローティングゲート606と、第2導電型ウェル608と、第1導電型ウェル610と、第2導電型ソース拡散層612と、第2導電型ドレイン拡散層614と、第2導電型制御ゲート拡散層616と、を含む。制御ゲート拡散層616、ソース拡散層612及びドレイン614の間の漏れ電流が二重のウェル領域上に印加されるバイアスを調節することにより減少される。

(もっと読む)

半導体記憶装置

【課題】電荷蓄積層及び制御ゲートを有する半導体記憶装置のバックバイアス効果による影響を低減させることにより集積度を向上させ、占有面積を増加させずに浮遊ゲートと制御ゲートとの容量の比をより一層増大させるとともに、製造プロセスに起因するセル特性のばらつきが抑制された半導体記憶装置を提供する。

【解決手段】半導体基板と、少なくとも1つの島状半導体層110、該島状半導体層110の側壁の周囲の全部又は一部に形成された電荷蓄積層513及び制御ゲート523から構成される少なくとも1つのメモリセルとを有する半導体記憶装置であって、前記メモリセルの島状半導体層110が不純物拡散層により前記半導体基板から電気的に絶縁されてなる。

(もっと読む)

半導体集積回路

【課題】電荷転送効率が高い転送トランジスタを備える半導体集積回路を提供することを目的とする。

【解決手段】実施形態に係る半導体集積回路は、ゲート電極を有し、当該ゲート電極及び一の拡散層が第1配線でダイオード接続された転送トランジスタと、クロック信号が供給されるクロック信号線とを備え、前記クロック信号線の一部である第1部分クロック信号線の少なくとも一部が前記ゲート電極上に形成されていることを特徴とする。

(もっと読む)

不揮発性半導体記憶装置とその製造方法

【課題】メモリセルが3次元的に積層された不揮発性半導体記憶装置で、メモリセルの投影面積を小さくすることができ、従来の平面型のフローティングゲート構造と類似の構造の不揮発性半導体記憶装置を提供する。

【解決手段】実施形態によれば、不揮発性半導体記憶装置は、シート状のチャネル半導体膜111の高さ方向に複数のメモリセルMCを有するメモリストリングが基板上にほぼ垂直に配置される。フローティングゲート電極膜109は、第2の方向に延在し、トンネル誘電体膜110を介してチャネル半導体膜111の第1の主面上に形成される。制御ゲート電極膜103は、第1の方向に延在する共通接続部1031と、共通接続部1031から第2の方向に突出し、フローティングゲート電極膜109の上部または下部に電極間絶縁膜108を介してメモリセルMCごとに設けられる電極構成部1032と、を有する。

(もっと読む)

電子部品の製造方法

【課題】導電膜を含む層の加工によって密の配線と疎の配線とが混在して形成された配線層で、所望の配線間の領域にのみ空隙を形成することができる電子部品の製造方法を提供する。

【解決手段】実施形態によれば、電子部品の製造方法は、まず、密の配線と疎の配線とを含む配線パターンとなるように、基板1上の導電性材料膜を含む加工対象を加工する。ついで、密の配線の形成領域にのみ配線間を埋め込む犠牲膜111を形成した後、基板1上に絶縁膜112を形成する。絶縁膜112上にレジスト113を塗布し、密の配線の形成領域上の一部と疎の配線の形成領域とが露出するようにレジスト113のパターニングを行った後、レジスト113をマスクとして絶縁膜112をエッチングする。さらに、密の配線の形成領域上の一部を通して、犠牲膜111を除去する。そして、疎の配線の形成領域で隣接する配線間を埋め込むように基板1上に埋込絶縁膜114を形成する。

(もっと読む)

プリント不揮発性メモリ

【課題】低コストで高スループットなプリント技術を使用した不揮発性メモリセルを提供する。

【解決手段】同一水平レベルにおいて所定の距離で離間している第1及び第2の半導体アイランドであって、第1の半導体アイランド2が制御ゲートを構成し、第2の半導体アイランド3がソース端子及びドレイン端子を構成する、当該第1及び第2の半導体アイランドと、第1の半導体アイランド2の少なくとも一部の上のゲート誘電体層4と、第2半導体アイランドの少なくとも一部の上のトンネリング誘電体層5と、ゲート誘電体層4とトンネリング誘電体層5の少なくとも一部の上のフローティングゲート7と、制御ゲート2並びにソース端子及びドレイン端子に電気的に接触する金属層と、を備える。一つの効果的な実施形態では、不揮発性メモリセルを、「全プリント」加工技術を使用して製造することができる。

(もっと読む)

半導体記憶装置の製造方法

【課題】隣接するメモリセル間およびメモリセルと選択トランジスタとの間に間隙を設けつつ、選択トランジスタおよび周辺回路における短絡を抑制する。

【解決手段】本実施形態による半導体記憶装置は、ゲートを有する複数のメモリセルが直列に接続されたメモリセルストリングを備える。選択トランジスタが、メモリセルストリングの一端にある端部メモリセルに接続されている。側壁膜が、端部メモリセルと選択トランジスタとの間において、端部メモリセルのゲートの側面および選択トランジスタのゲートの側面を被覆する。端部メモリセルの側壁膜と選択トランジスタの側壁膜との間に空隙がある。

(もっと読む)

半導体装置の製造方法

【課題】フラッシュメモリセルと低電圧動作トランジスタや高電圧動作トランジスタを集積化し、異種トランジスタを混載する半導体装置の製造法を提供する。

【解決手段】半導体装置の製造方法は、(a)トンネル絶縁膜、Fゲート電極膜、電極間絶縁膜を堆積したFゲート電極構造を形成し(b)ゲート絶縁膜を形成し(c)導電膜、エッチストッパ膜を堆積し(d)エッチストッパ膜、導電膜をエッチングした積層ゲート電極構造を形成し(e)積層ゲート電極構造の側壁上に第1絶縁膜を形成し(f)積層ゲート電極側壁上に第1サイドウォールスペーサ層を形成し(g)エッチストッパ層を除去し(h)他の領域の導電層から、ゲート電極構造を形成し(i)積層ゲート電極構造、ゲート電極構造側壁上に第2サイドウォールスペーサを形成し(j)希弗酸水溶液で半導体基板表面を露出し(k)半導体基板表面にシリサイド層を形成する。

(もっと読む)

半導体不揮発性メモリ装置

【課題】トンネル絶縁膜にエッジ部があることによるトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得る。

【解決手段】トンネル絶縁膜の上部であって、トンネル領域のエッジ部から離間した位置に、電荷受け渡し用電極を配置し、電荷受け渡し用電極とフローティングゲート電極とが、電気的に接続されるようにした。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】専有面積が小さく、高集積化、大記憶容量化が可能な半導体装置を提供する。

【解決手段】第1の制御ゲート、第2の制御ゲート及び記憶ゲートを有するトランジスタを用いる。記憶ゲートを導電体化させ、該記憶ゲートに特定の電位を供給した後、該記憶ゲートを絶縁体化させて電位を保持させる。情報の書き込みは、第1及び第2の制御ゲートの電位を記憶ゲートを導電体化させる電位とし、記憶ゲートに記憶させる情報の電位を供給し、第1及び第2の制御ゲートの電位を記憶ゲートを絶縁体化させる電位とすることで行う。情報の読み出しは、第2の制御ゲートの電位を記憶ゲートを絶縁体化させる電位とし、トランジスタのソースまたはドレインの一方と接続された読み出し信号線に電位を供給し、その後、第1の制御ゲートに読み出し用の電位を供給し、ソースまたはドレインの他方と接続されたビット線の電位を検出することで行う。

(もっと読む)

不揮発性記憶装置

【課題】基板の活性領域と制御ゲート電極との間の高い耐電圧特性を有する不揮発性記憶装置を提供する。

【解決手段】素子分離絶縁溝を有する基板と、前記基板上の前記素子分離溝の両側に形成された第1および第2のトンネル絶縁膜、第1および第2の浮遊ゲート電極と、前記第1および第2の浮遊ゲート電極の上面を覆い、かつ前記第1の浮遊ゲート電極と第2の浮遊ゲート電極との間、前記第1のトンネル絶縁膜と第2のトンネル絶縁膜との間、および前記素子分離絶縁溝の少なくとも上部を埋めるように形成されたゲート間絶縁膜と、前記ゲート間絶縁膜上に形成された制御ゲート電極と、を有する不揮発性記憶装置を提供する。前記ゲート間絶縁膜は、電子トラップ性を有する第1の絶縁材料からなる電子トラップ層と、前記第1の材料よりも電子トラップ性が低い第2の絶縁材料からなり、前記電子トラップ層を挟む第1および第2の絶縁層とを含む。

(もっと読む)

半導体装置

【課題】高度な集積化を実現した、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】チャネル形成領域を含む半導体層と、チャネル形成領域と電気的に接続するソース電極およびドレイン電極と、チャネル形成領域と重畳するゲート電極と、チャネル形成領域とゲート電極との間のゲート絶縁層と、を含み、チャネル形成領域を含む半導体層の側面の一部と、ソース電極またはドレイン電極の側面の一部と、は、平面方向から見て概略一致している半導体装置である。

(もっと読む)

半導体装置及びそれを用いた論理回路

【課題】面積を縮小させることが出来、また歩留まりを向上させる半導体装置及びそれを用いた論理回路を提供すること。

【解決手段】第1トランジスタTr1と第2トランジスタTr2とが形成され、前記第1トランジスタTr1はソース及びドレインとして機能する第1拡散層群103と、第1ゲート電極102と、第2ゲート電極104とを備え、前記第2トランジスタTr2はソース及びドレインとして機能する第2拡散層群201と、電荷を蓄積可能な浮遊ゲート202と、第3ゲート電極200とを備え第2ゲート電極200は、前記第1トランジスタTr1の閾値Vthを制御可能とし、この第2ゲート電極104の電位は、前記浮遊ゲート202が蓄積する電荷量に応じた値である。

(もっと読む)

半導体記憶装置

【課題】不良要素の効率良い置き換えを可能にする構成を有する半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数の単位構造を有する。単位構造は、複数のメモリセルと接続された複数のビット線と、複数のビット線のうちの隣接する複数のビット線とそれぞれ接続された複数のセンスアンプと、複数のセンスアンプと共通に接続された第1データ線SBUSと、第1データ線と接続された演算回路Yと、演算回路と接続された第2データ線DBUSと、第2データ線と接続された複数のデータラッチXDLを含む。複数の単位構造は、相互に独立しており、またその一部はスペア用単位構造である。複数の単位構造の1つは、スペア用単位構造と置き換えられる。

(もっと読む)

不揮発性半導体記憶装置

【課題】不揮発性半導体記憶装置について、製造工程中のゲート絶縁膜及び容量絶縁膜の特性劣化を抑制する。

【解決手段】不揮発性半導体記憶装置は、第1導電型の半導体基板2上のMISFET16と、第2導電型の第1ウェル3のMISキャパシタ17とを含む。MISFET16は、半導体基板2上のゲート絶縁膜4、その上のゲート電極6a、ゲート電極6aの両側のソース・ドレイン不純物層7及び8を含む。MISキャパシタ17は、第1電極としての第1ウェル3上の容量絶縁膜5、その上の第2電極6b、第1導電型の第1不純物層11a及び11bを含む。ゲート電極6aと第2電極6bとが電気的に接続されてフローティングゲート6を構成する。ゲート絶縁膜4と容量絶縁膜5とは材料及び膜厚が同一である。ゲート電極6aと第2電極6bとは同一の導電膜からなる。半導体基板2と第1ウェル3との境界を跨ぐ第2不純物層14が形成されている。

(もっと読む)

1 - 20 / 151

[ Back to top ]