Fターム[5F101BA05]の内容

不揮発性半導体メモリ (42,765) | 電荷蓄積機構 (9,664) | FG型 (6,485) | FG配置 (488) | フィールド上 (37)

Fターム[5F101BA05]に分類される特許

1 - 20 / 37

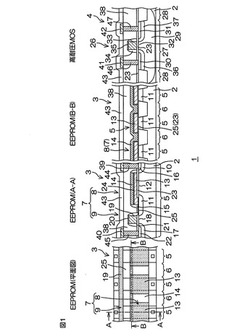

半導体装置および半導体装置の製造方法

【課題】トンネルウィンドウやセレクトゲートの加工寸法のばらつき、およびセレクトゲートのアライメント精度を考慮する必要がなく、セルサイズを小さくすることができる半導体装置およびその製造方法を提供すること。

【解決手段】不揮発性メモリセル7を半導体基板2上に選択的に備える半導体装置1が製造される。この製造方法は、ゲート絶縁膜23上において不揮発性メモリセル7用のアクティブ領域5に、セレクトゲート19を選択的に形成する工程と、セレクトゲート19に対して自己整合的に導入することによってn型トンネル拡散層11を形成する工程と、ゲート絶縁膜23の一部セレクトゲート19に対して自己整合的に除去し、その後の熱酸化によりトンネルウィンドウ25を形成する工程とを含む。

(もっと読む)

不揮発性半導体メモリ素子、および不揮発性半導体メモリ装置

【課題】フローティングゲートへの電荷の蓄積と消去を容易に行え、またフローティングゲートの電荷を消去する場合にメモリセルの閾値を容易に制御できる、不揮発性半導体メモリ素子を提供する。

【解決手段】フローティングゲートへの電荷の蓄積時に、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットエレクトロンを半導体基板中に発生させ、フローティングゲートに電荷を注入する。また、フローティングゲートの電荷の消去時には、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットホールを発生させ、該ホットホールにより蓄積された電荷を消去する。また、フローティングゲートの電荷の消去時には、メモリセルのコントロールゲートとソース間の閾値が所望の値になるように制御しながら、電荷を消去する。

(もっと読む)

半導体記憶装置及び半導体記憶素子

【課題】素子の面積を増大させることなく、かつ、コントロールゲート電圧を制御しなくとも、低電圧で書き込み量を大幅に増やすことが可能であり、また、安定して十分な書き込みを行うことが可能である不揮発性半導体装置を提供すること。

【解決手段】ドレインアバランシェホットエレクトロンにより書き込みを行う半導体記憶素子であって、第1導電型の半導体基板に形成された第2導電型の第1の半導体層と、前記第1の半導体層上に絶縁膜を介して設けられたフローティングゲートと、前記フローティングゲート下部の前記第1の半導体層の表面に形成されたチャネル領域と、前記チャネル領域に接触するように前記第1の半導体層上に設けられた第1導電型のソース領域及びドレイン領域とを有するMOSトランジスタであって、前記チャネル領域が2種類以上のキャリア濃度の分布をもつ半導体記憶素子とした。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】浮遊ゲート電極の細りを補償して信頼性を向上させた不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置10では、第1の幅W1を有する活性領域12が、半導体基板11の主面に形成された素子分離層13で分離されている。第1ゲート絶縁膜14が、活性領域12に形成されている。第1の幅W1より狭い第2の幅W2を有する第1導電層15aが、第1ゲート絶縁膜14を介して活性領域12に形成されている。第1の幅W1と第2の幅W2の差を補償するように第3の幅W3を有する第2導電層15aが第1導電層15aの側壁に形成されている。第1ゲート電極15は、第1導電層15aと第2導電層15bを含んでいる。第2ゲート絶縁膜16が、第1ゲート電極15および素子分離層13上にコンフォーマルに形成されている。第2ゲート電極17が、第2ゲート絶縁膜16上に形成されている。

(もっと読む)

ボトムポリ制御ゲートを使用するPMOSフラッシュセル

【課題】制御ゲートが占有する面積を大幅に減らし、PMOSメモリ回路の密度を大幅に向上させることができるボトムポリ制御ゲートを使用するPMOSフラッシュセルを提供する。

【解決手段】2つのトランジスタのPMOSメモリセルは、SG−PMOS150a、FG−PMOS150b及び制御ゲート125を備える。SG−PMOS150aは、n型ウェル110中に設けられたドレイン及びソースを有する。FG−PMOS150bは、n型ウェル110中に設けられたソース及びドレインを有する。SG−PMOS150aのドレインとFG−PMOS150bのソースとは同じである。制御ゲート125は、第1のポリシリコン層からなり、アイソレーション構造115上に形成され、FG−PMOS150bの浮遊ゲート135bの延伸部分と重畳する。

(もっと読む)

半導体装置およびその製造方法

【課題】データ保持特性の良好な不揮発性メモリおよびその製造技術を提供する。

【解決手段】ゲート絶縁膜6上に多結晶シリコン膜7および絶縁膜8を順次堆積し、これら多結晶シリコン膜7および絶縁膜8をパターニングしてゲート電極7A、7Bを形成した後、ゲート電極7A、7Bの側壁に酸化シリコン膜からなるサイドウォールスペーサ12を形成する。その後、基板1上にプラズマCVD法で窒化シリコン膜19を堆積することにより、ゲート電極7A、7Bと窒化シリコン膜19とが直接接しないようにする。

(もっと読む)

半導体記憶装置の製造方法

【課題】データ書き込み時に、電流値が低下して、電荷保持特性が著しく低下することを防止する。

【解決手段】第1の方向に延在した複数の活性領域列と、第1の方向と実質的に直交する第2の方向に延在する複数の活性領域行からなる活性領域101を形成する工程と、活性領域列上に浮遊電極及び制御電極を形成するとともに、活性領域行に低面及び底面を囲む側面を備えた凹部105を形成する工程と、活性領域101および制御電極の上に、上部配線110の下層となる層間絶縁膜109を形成する工程と、上部配線110と活性領域101との電気的接続をとり、底面及び側面に接続する導電部106を活性領域行の凹部105上に形成する工程とを備える。

(もっと読む)

半導体装置

【課題】素子分離領域の端部における応力ひずみの発生及び結晶欠陥発生を抑制する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1と、半導体基板1内に形成された第1素子領域9、半導体基板1に埋め込まれて第1素子領域9を分離する第1素子分離領域4を有し、印加される電圧が第1レベルで動作を行うメモリ回路領域と、半導体基板内1に形成された第2素子領域15、半導体基板1に埋め込まれて第2素子領域15を分離する第2素子分離領域12を有し、印加される電圧が第1レベルよりも大きい第2レベルで動作を行う周辺回路領域とを備え、第1素子分離領域4の溝下方の側面と半導体基板1に垂直な平面のなす第1のテーパー角度は、第2素子分離領域12の溝下方の側面と半導体基板1に垂直な平面のなす第2のテーパー角度よりも大きい。

(もっと読む)

不揮発性半導体メモリ及びその製造方法

【課題】メモリセルトランジスタのチャネル端に寄生素子が発生するのを抑制できる。

【解決手段】本発明の例の不揮発性半導体メモリは、半導体基板1と、半導体基板1内に形成されるSTI構造の素子分離絶縁層と、素子分離絶縁層間のチャネル領域と、チャネル領域上のゲート絶縁膜2と、ゲート絶縁膜2上の浮遊ゲート電極3と、浮遊ゲート電極3上の中間絶縁膜5と、中間絶縁膜5上の制御ゲート電極6とを具備し、素子分離絶縁層は、半導体基板の凹部の底面及び側面に形成される熱酸化膜7と、熱酸化膜7上に形成され、凹部を満たすSTI絶縁膜8とから構成され、浮遊ゲート電極3のチャネル幅方向の寸法W1は、チャネル幅の寸法W2よりも広いことを備える。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】浮遊ゲート間の電荷移動によるデータ破壊を防止して信頼性向上を図った不揮発性半導体記憶装置を提供する。

【解決手段】シリコン基板1にストライブ状の素子形成領域2を区画する素子分離絶縁膜4が埋め込まれる。この基板1に第1のゲート絶縁膜5を介して浮遊ゲート6が形成され、更に第2のゲート絶縁膜7を介して制御ゲート8が形成される。制御ゲート8に自己整合的にソース、ドレイン拡散層12が形成される。浮遊ゲート6上の第2のゲート絶縁膜7は、浮遊ゲート6と共に、素子分離絶縁膜4上でスリット13により隣接するメモリセル間で分離される。

(もっと読む)

半導体装置及びその製造方法

【課題】アクティブ領域の形状に起因する特性の変動を抑制した半導体装置を提供する。

【解決手段】半導体基板のアクティブ領域を区画し、少なくとも一部が前記半導体基板中に設けられた素子分離20と、前記アクティブ領域上に設けられたメモリセルトランジスタ及び選択トランジスタを含む半導体装置であって、前記メモリセルトランジスタは、前記アクティブ領域の少なくとも一部を含むように設けられたスリット26により区画され、チャネル領域上にゲート絶縁膜22を介して設けられた第1のゲート電極24と、前記第1のゲート電極24を覆い電極間絶縁膜28を介して設けられた第2のゲート電極32とを具備し、前記選択トランジスタは、前記アクティブ領域上にゲート絶縁膜22を介して設けられ、配線に接続された第3のゲート電極24Sと、前記第3のゲート電極24S上に電極間絶縁膜28を介して形成された第4のゲート電極32とを具備する。

(もっと読む)

Fin型メモリセル

【課題】Fin−FETとの混載に適したFin型メモリセルを提案する。

【解決手段】本発明の例に関わるFin型メモリセルは、フィン形状のアクティブエリアAAと、アクティブエリアAAの側面に沿うフローティングゲート電極FGと、フローティングゲート電極FGに対してアクティブエリアAAの長手方向に配置され、フローティングゲート電極FGを挟み込む2つのコントロールゲート電極CGとを備える。

(もっと読む)

半導体装置

【課題】工程数の増加を伴うことなく、FAMOSにおける電気的な消去を実現することが可能な半導体装置を提供する。

【解決手段】P型半導体基板1に形成されたN−ウェル層31と、N−ウェル層31に形成されたP−不純物拡散層4と、P−不純物拡散層4から離れた一の領域のN−ウェル層31上にゲート絶縁膜7を介して形成され、P−不純物拡散層4上と、当該P−不純物拡散層4から離れた他の領域のN−ウェル層31上とにそれぞれ延伸されたフローティングゲート8と、ゲート絶縁膜7上のフローティングゲート8を挟み込むようにN−ウェル層31に形成され、素子分離絶縁膜8によってP−不純物拡散層4と分離されたP+型不純物拡散層6a、6bと、フローティングゲート8が延伸された他の領域に隣接してN−ウェル層31に形成されたP+型不純物拡散層5aと、を備えたものである。

(もっと読む)

半導体記憶装置

【課題】より低電圧での消去動作を可能にすること。

【解決手段】基板上の第1の領域に配設されたセレクトゲート3と、前記第1の領域に隣接する第2の領域に配設されたフローティングゲート6と、前記第2の領域と隣接する第3の領域に設けられた第1の拡散領域7と、フローティングゲート6の上に配設されたコントロールゲート11と、基板1(ウェル1a)、セレクトゲート3、第1の拡散領域7、およびコントロールゲート11に印加される電圧を制御する駆動回路22と、を備え、駆動回路22は、消去動作の際、セレクトゲート3およびコントロールゲート11の電圧を負電圧とし、残り1つ基板1(ウェル1a)の電圧を正電圧とするように制御する。

(もっと読む)

半導体記憶装置

【課題】メモリセルが微細化されても十分な動作マージンを確保できるようにすること。

【解決手段】基板1、セレクトゲートSG0、SG1、ローカルビット線LB2、及びコントロールゲートCGnに印加される電圧を制御する駆動回路22を備える。駆動回路22は、書き換え動作の際、コントロールゲートCGnに対して負電圧、セレクトゲートSG0に正電圧、セレクトゲートSG1にセレクトゲートSG0の電圧よりも低い電圧、ローカルビット線LB2に正電圧をそれぞれ印加することによって、FNトンネリングによりフローティングゲートFG3からローカルビット線LB2に電子を選択的に引き抜く制御を行なう。

(もっと読む)

不揮発性メモリ装置及びその製造方法

【課題】不揮発性メモリ装置及びその製造方法を提供する。

【解決手段】半導体基板100の第1及び第2領域に形成されて、第1及び第2活性領域を各々画定する第1及び第2素子分離膜パターン125,122と、第1及び第2活性領域の上部に各々配置される第1及び第2下部導電パターン200,205と、第1及び第2下部導電パターン200,205の上部で第1及び第2活性領域を各々横切る第1及び第2上部導電パターン210,215と、第1下部導電パターン200と第1上部導電パターン210との間に介在されるゲート層間絶縁膜パターン185と、を含み、第1下部導電パターン200は、底部152及び当該底部152から延長されて当該底部152よりも狭い幅を有する少なくとも一つの延長部153を具備し、第2下部導電パターン205は、第1下部導電パターン200の底部152よりも厚い。

(もっと読む)

フラッシュメモリ素子及びその製造方法

【課題】サイクリングの際にコントロールゲートとチャネル領域間の酸化膜にトラップされる電荷量を減らすことが可能なフラッシュメモリ素子の提供。

【解決手段】フィールド領域およびアクティブ領域が画定された半導体基板と、前記アクティブ領域およびこれに隣接したフィールド領域上に形成されるトンネル酸化膜と、前記トンネル酸化膜の両側で一定の深さのモウトを有する素子分離膜と、前記トンネル酸化膜およびその両側の素子分離膜上に形成され、前記モウトの内部を充填するフローティングゲートと、前記フローティングゲートおよび素子分離膜の表面段差に沿って形成される誘電体膜と、前記誘電体膜上に形成されるコントロールゲートとから構成されることを特徴とするフラッシュメモリ素子を提供する。

(もっと読む)

半導体記憶装置

【課題】メモリセルアレイ端の領域のエッチング精度の低下に起因した不良を防ぐことができる半導体記憶装置を提供することを目的としている。

【解決手段】メモリセルM1〜M8を複数個接続した第1のメモリセルユニットにより構成された第1のブロック2−0,2−Nと、メモリセルM1〜M8を複数個接続した第2のメモリセルユニットにより構成された第2のブロック2−1〜2−(N−1)とを有し、両端に前記第1のブロックを、他の部分には前記第2のブロックを配設してメモリセルアレイ2を構成している。そして、前記第1のメモリセルユニットの前記メモリセルアレイ端側の構成が前記第2のメモリセルユニットと異なることを特徴とする。メモリセルアレイ端の領域のエッチング精度の低下に起因した不良を防ぐことができ、チップサイズの増加をほとんど招くことなく、歩留まりが高く且つ動作の信頼性の高い動作を実現できる。

(もっと読む)

U字状浮遊ゲートを有するフラッシュメモリの製造方法

【課題】U字状浮遊ゲートを有するフラッシュメモリの製造方法を提供する。

【解決手段】上面と両側面の一部とが基板表面から突出した素子分離膜を形成した後、素子分離膜の間の基板上にトンネル酸化膜を形成する。トンネル酸化膜上に素子分離膜の間を満たさない厚さに導電膜を形成した後、導電膜上に研磨犠牲膜を形成する。素子分離膜上の研磨犠牲膜及び導電膜を除去して素子分離膜の間に自己整列されたU字状浮遊ゲートを形成すると同時に、浮遊ゲート上に研磨犠牲膜パターンを残す。研磨犠牲膜パターンをマスクとして用いて素子分離膜をリセスさせて、浮遊ゲートの両側壁を露出させる。浮遊ゲートに対して研磨犠牲膜パターンを選択的に除去して浮遊ゲートの上面を露出させるフラッシュメモリの製造方法である。

(もっと読む)

半導体装置およびその製造方法

【課題】 ドレインコンタクトの形成時にSTIと活性領域との段差に起因したエッチング残りでコンタクト面積の縮小で抵抗が高くなるのを防止する。

【解決手段】 NOR型フラッシュメモリにおいて、ゲート電極4の形成後にスペーサとして第1のシリコン窒化膜15を形成する。この後、ドレインコンタクトの形成領域のSTI2の高さをエッチングにより低くして活性領域3との段差を小さくする(ΔH<Δh)ことで、第2のシリコン窒化膜16形成後のコンタクト形成で、段差部分に残渣が少なくなりコンタクト面積の減少を防止できる。これにより、コンタクト抵抗の低減を図れ、しかもゲート絶縁膜であるシリコン酸化膜7の端面が保護されているので悪影響を与えることがない。

(もっと読む)

1 - 20 / 37

[ Back to top ]