Fターム[5F101BA03]の内容

不揮発性半導体メモリ (42,765) | 電荷蓄積機構 (9,664) | FG型 (6,485) | FG配置 (488) | SDとの重なり (68)

Fターム[5F101BA03]に分類される特許

1 - 20 / 68

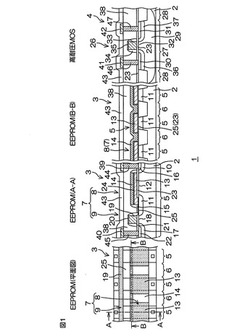

半導体装置および半導体装置の製造方法

【課題】トンネルウィンドウやセレクトゲートの加工寸法のばらつき、およびセレクトゲートのアライメント精度を考慮する必要がなく、セルサイズを小さくすることができる半導体装置およびその製造方法を提供すること。

【解決手段】不揮発性メモリセル7を半導体基板2上に選択的に備える半導体装置1が製造される。この製造方法は、ゲート絶縁膜23上において不揮発性メモリセル7用のアクティブ領域5に、セレクトゲート19を選択的に形成する工程と、セレクトゲート19に対して自己整合的に導入することによってn型トンネル拡散層11を形成する工程と、ゲート絶縁膜23の一部セレクトゲート19に対して自己整合的に除去し、その後の熱酸化によりトンネルウィンドウ25を形成する工程とを含む。

(もっと読む)

二重層フローティングゲートを備えているEPROMセル

【課題】インクジェットペンコントロールチップの既存の層を利用して製造できるEPROMを提供する。

【解決手段】EPROMセル70は、ソース領域及びドレイン領域を有する半導体基板52と、第1の金属層60と電気的に相互接続されている半導体ポリシリコン層56を含むフローティングゲート72と、第2の金属層64を含むコントロールゲートとを備えている。フローティングゲート72は、ソース領域及びドレイン領域に隣接して配置され、第1の誘電体層54によって半導体基板52から分離され、コントロールゲートの第2の金属層64は、第1の金属層60との間にある第2の誘電体層62を介して、第1の金属層60と容量結合されている。

(もっと読む)

導電性側壁スペーサを有する不揮発性メモリ装置及びその製造方法

【課題】従来の窒化膜側壁を電荷トラップ媒体に利用する場合の信頼性劣化を改善した不揮発性メモリ装置を提供する。

【解決手段】半導体基板21上のゲート絶縁膜22Aと、該ゲート絶縁膜上に順に積層して形成された第1電極膜23、第2電極膜24、及びハードマスク膜25を有するゲート100と、該ゲートの第1電極膜23及び第2電極膜24の両側壁に形成された一対の再酸化側壁スペーサ27と、該再酸化側壁スペーサ及びゲート100のハードマスク膜25の両側壁上に形成された一対の側壁スペーサ28Aと、一対の側壁スペーサ28A上に形成された、電荷を捕獲及び放出する一対の導電性側壁スペーサ29Bと、半導体基板21内に形成された一対のLDD領域26と、半導体基板21内に形成されたソース/ドレイン領域30とを備え、導電性側壁スペーサ29Bが、ゲート100及び側壁スペーサ28Aよりも低い高さを有する。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を提供する。

【解決手段】フローティングゲート電極を、掘り下げ領域に埋め込んで形成し、ドレイン領域内のトンネル領域と掘り下げ領域に埋め込まれて形成されたフローティングゲート電極の側面との間にトンネル絶縁膜を設ける。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得ることを目的とする。

【解決手段】ドレイン領域内のトンネル領域には、ドレイン領域と同一の電位に固定されたドレイン領域に比べて不純物濃度の低い第2導電型の領域と、不純物濃度の低い第1導電型の領域とを形成し、不純物濃度の低い第2導電型の領域と、不純物濃度の低い第1導電型の領域のそれぞれの上面に、フローティングゲート電極への電子注入用と電子引き抜き用のトンネル絶縁膜を独立して設けた。また、データ書き換え時に印加されるストレスが偏らないように、電子引き抜き用のトンネル絶縁膜に比べて電子注入用のトンネル絶縁膜の面積を大きくあるいは厚くした。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を提供する。

【解決手段】トンネル領域とフローティングゲート電極との間には、膜厚の異なる複数のトンネル絶縁膜を形成した。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を提供する。

【解決手段】フローティングゲート電極は、高い不純物濃度領域と低い不純物濃度領域とからなり、高い不純物濃度領域は、コントロールゲート絶縁膜と接する部分に配置し、低い不純物濃度領域はトンネル絶縁膜と接する領域に配置し、フローティングゲート電極のコントロールゲート絶縁膜と接する表面部分には微細凹凸を形成した。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を提供する。

【解決手段】トンネル領域のエッジ近傍のトンネル絶縁膜上には、トンネル絶縁膜とは異なる材質の絶縁膜からなる電界緩和層を配置した。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書 き換え可能な半導体不揮発性メモリ装置を提供する。

【解決手段】トンネル絶縁膜の上部であって、トンネル領域のエッジ部近傍の領域には、フローティングゲート電極とガード絶縁膜を介してドレイン電極と同電位に固定されたトンネル領域エッジ部ガード電極を配置した。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得る。

【解決手段】第2導電型のトンネル領域のフローティングゲート電極のエッジ部の下部に、第1導電型の領域からなるフローティングゲート電極エッジの電界集中防止用領域を形成する。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書 き換え可能な半導体不揮発性メモリ装置を得る。

【解決手段】ドレイン領域内のトンネル領域とフローティングゲート電極領域との間には、トンネル絶縁膜が設けられており、トンネル領域のエッジ近傍のフローティングゲート電極の不純物濃度は、その他の箇所のフローティングゲート電極の不純物濃度に比べて低く設定した。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書 き換え可能な半導体不揮発性メモリ装置を得ることを目的とする。

【解決手段】電気的書き換え可能な半導体不揮発性メモリにおいて、第2導電型のドレイン領域内のトンネル領域と前記フローティングゲート電極領域との間には、トンネル絶縁膜が設けられており、前記フローティングゲート電極は第1導電型の導電体で形成されている電気的書き換え可能な半導体不揮発性メモリ装置。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書 き換え可能な半導体不揮発性メモリ装置を得ることを目的とする。

【解決手段】電気的書き換え可能な半導体不揮発性メモリにおいて、第2導電型のドレイン領域内のトンネル領域の表面には、薄い不純物濃度の第1導電型の領域を形成した。

(もっと読む)

半導体不揮発性メモリ装置

【課題】膜質の劣化を抑え、トンネル領域のエッジ部への電界集中を防止し、占有面積を増加することなくトンネル絶縁膜の劣化を抑制して、高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得る。

【解決手段】電気的書き換え可能な半導体不揮発性メモリにおいて、ドレイン領域内のトンネル領域と前記フローティングゲート電極領域との間には、第1のトンネル絶縁膜と第2のトンネル絶縁膜が設けられており、第1のトンネル絶縁膜は、トンネル領域のエッジ部近傍に形成されており、第2のトンネル絶縁膜はトンネル領域の前記第1のトンネル絶縁膜か形成されていない領域に形成されており、第1のトンネル絶縁膜の膜厚は、第2のトンネル絶縁膜の膜厚よりも大きく、ゲート絶縁膜よりも小さく形成した。

(もっと読む)

メモリセル電荷記憶素子あたりに二重のコントロールゲートを有するフラッシュメモリセルアレイ

【課題】フローティングゲートが少なくとも2つのコントロールゲートラインと容量的に結合するようになっているフラッシュNANDタイプのEEPROMシステムの提供。

【解決手段】コントロールゲートラインはフローティングゲートの側壁と結合するようにフローティングゲート間に位置し、メモリセルの結合比が望ましく高められる。フローティングゲートの選択された行の両側の両方のコントロールゲートラインは普通同じ電圧まで高められ、隣接するフローティングゲートの選択されていない行に結合された第2のコントロールゲートラインは低く保たれる。選択されたフローティングゲートの領域でその電圧を選択的に高めるために、コントロールゲートラインを基板と容量的に結合させる。フローティングゲートの長さとコントロールゲートラインの厚さとは、スペーサのエッチマスクを形成することによってプロセスの最小分解エレメントより小さくされ得る。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】従来の半導体記憶装置では、十分に半導体チップの面積を削減することができない問題があった。

【解決手段】本発明の半導体記憶装置は、半導体基板の平坦部に形成されたドレイン領域13と、半導体基板に形成された凸部の上端部に形成されたソース領域10と、ドレイン領域13の一部と重なる領域であって、かつ、平坦部の上層に形成されるコントロールゲート12と、コントロールゲート12と隣り合った領域であって、平坦部、凸部の壁面及びソース領域10の一部を覆う領域に形成されるフローティングゲート11と、を有する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】N+型ソース層とフローティングゲートとのカップリング比を高くしてプログラム特性を改善すると共にメモリーセルの面積の縮小化を図る。

【解決手段】N+型ソース層4の両側にトレンチ3を形成する。トレンチ3の側壁は2つの素子分離層STI2の端面と平行なトレンチ側壁2a、トレンチ側壁2bと、STI2に垂直な面からなるトレンチ側壁3a、及びトレンチ側壁3aと平行でないトレンチ側壁3bから構成される。かかる構成のトレンチ3の上部からトレンチ側壁3aに平行で、且つP型ウエル層1に垂直又は角度をもった砒素イオン等のイオン注入を行い、トレンチ3底面からトレンチ側壁3bに延在するフローティングゲートFG6と広い面積で対峙するN+型ソース層4を形成する。

(もっと読む)

スプリットゲート型不揮発性半導体記憶装置の製造方法、及びスプリットゲート型不揮発性半導体記憶装置

【課題】スプリットゲート型不揮発性記憶装置に製造における工程数を削減する。

【解決手段】基板(2)と、ゲート絶縁膜(7)を介して基板(2)の上に形成されたフローティングゲート(5)と、トンネル絶縁膜(8)を介してフローティングゲート(5)の隣に形成されたコントロールゲート(6)と、コントロールゲート(6)側の基板(2)に形成された第1ソース/ドレイン拡散層(4)と、フローティングゲート(5)側の基板(2)に形成された第2ソース/ドレイン拡散層(3)と、第1ソース/ドレイン拡散層(4)と第2ソース/ドレイン拡散層(3)との間の基板に設けられるチャネル領域と、第2ソース/ドレイン拡散層(3)に接触しているシリサイド(21)とを具備するスプリットゲート型不揮発性半導体記憶装置を構成する。

(もっと読む)

半導体装置

【課題】第1導電型の半導体層とトンネルウィンドウが対向する第2導電型の不純物拡散領域との高い接合耐圧を得ることができる、半導体装置を提供する。

【解決手段】各メモリセルにおいて、半導体基板2の表層部には、N型の第1不純物拡散領域3が形成されている。また、半導体基板2の表層部には、第1不純物拡散領域3に対して所定方向の一方側に、第1不純物拡散領域3と間隔を空けて、N型の第2不純物拡散領域4が形成されている。半導体基板2上には、第1絶縁膜6が形成されている。第1絶縁膜6には、第1厚膜部8が形成されており、第2不純物拡散領域4の全周縁は、第1厚膜部8の直下に位置している。

(もっと読む)

不揮発性半導体記憶装置および動作方法

【課題】NOR型B4−Flash不揮発性半導体記憶装置の構造および動作方法の改良に関する。B4−Flashではソース側でも弱いB4−HE注入が起り、書込み非選択のセルに対して不必要な書込みが起ってしまう。またスケーリングが進みゲート長が短くなるとショートチャネル効果によりメモリセルのパンチスルーが起こり書き込みが出来なくなると言う課題があった。

【解決手段】ソース・ドレイン拡散層の構造を非対称にし、ソース側の濃度を下げ電荷蓄積層に対してオフセット構造とすることでソース側からの不必要な書き込みが起こらないようにする。さらに前記ソース構造を採用する事による読み出し電流の低下を避ける為に書込み時とソース・ドレインの電位配置を逆にしたリバースリード読み出しを行う。これにより、NOR型アレイ配置のB4−Flashにおけるソース側からの誤書込みの低減とショートチャネル耐性の改善が可能になる。

(もっと読む)

1 - 20 / 68

[ Back to top ]