Fターム[5F083ZA11]の内容

Fターム[5F083ZA11]の下位に属するFターム

メモリ+(ロジック、アナログ)LSI (844)

メモリ+CPU(マイコン) (621)

メモリ部+メモリ部(異種) (302)

メモリ+(ゲートアレイ、マスタスライス) (127)

Fターム[5F083ZA11]に分類される特許

1 - 20 / 47

集積回路装置及びその製造方法

【課題】FinFETの特性が均一な集積回路装置及びその製造方法を提供する。

【解決手段】実施形態に係る集積回路装置は、半導体基板の上面に形成され、第1方向に延びる複数本のフィンと、前記フィン間に配置された素子分離絶縁膜と、前記第1方向に対して交差した第2方向に延び、前記素子分離絶縁膜上に設けられたゲート電極と、前記フィンを前記ゲート電極から絶縁する絶縁膜と、を備える。そして、連続して配列された複数本の前記フィンが配置された第1領域においては、前記素子分離絶縁膜の上面は前記フィンの上端よりも下方の第1の位置に位置し、前記第1領域から見て前記第2方向に位置する第2領域においては、前記素子分離絶縁膜の上面は前記フィンの上端よりも上方の第2の位置に位置する。また、前記第2領域においては、前記素子分離絶縁膜が前記フィンの側面の全体を覆っている。

(もっと読む)

半導体装置の製造方法

【課題】充分なキャパシタ容量を有する半導体装置を提供する。

【解決手段】半導体装置100の製造方法は、次の工程を含む。まず、基板(半導体基板102)上に下部電極152を形成する。次いで、下部電極152を第1結晶化処理する。次いで、第1結晶化処理後の下部電極152の上に容量絶縁層154を形成する。次いで、容量絶縁層154を第2結晶化処理する。この後、容量絶縁層154上に上部電極156を形成する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いたトランジスタ(より広義には、十分にオフ電流が小さいトランジスタ)を用いた記憶回路と、酸化物半導体以外の材料を用いたトランジスタ(換言すると、十分な高速動作が可能なトランジスタ)を用いた駆動回路などの周辺回路と、を一体に備える半導体装置とする。また、周辺回路を下部に設け、記憶回路を上部に設けることで、半導体装置の面積の縮小化及び小型化を実現することができる。

(もっと読む)

記憶素子及び記憶装置

【課題】電力の供給が停止した後もデータを保持することができる、新たな構成の記憶素子を提供することを目的の一とする。

【解決手段】記憶素子は、ラッチ回路と、第1の選択回路と、第2の選択回路と、第1の不揮発性記憶回路と、第2の不揮発性記憶回路と、を有する。また、第1の不揮発性記憶回路及び第2の不揮発性記憶回路は、それぞれトランジスタ及び容量素子を有する。第1及び第2の不揮発性記憶回路のそれぞれが有するトランジスタは、チャネルが酸化物半導体膜に形成されるトランジスタである。当該トランジスタは、オフ電流が極めて低いため、トランジスタと容量素子の接続点であるノードにデータが入力された後、トランジスタがオフ状態となり、電源電圧の供給が停止しても、長期間にわたりデータを保持することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の製造後におけるチャージ蓄積用素子からのチャージの放電を防止してデバイス機能素子のチャージダメージを低減する半導体装置及びその製造方法を提供する。

【解決手段】 半導体基板上に形成されたデバイス機能素子と、半導体基板上に形成されたチャージ蓄積用素子と、半導体基板上に形成され、デバイス機能素子とチャージ蓄積用素子との間に接続され、電気的に書き換え可能な不揮発性メモリトランジスタにより形成された分離用素子とを有する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、最初に、第1のレジスト膜を用いて、隣接ゲート電極間切断領域のエッチングを実行し不要になった第1のレジスト膜を除去した後、第2のレジスト膜を用いて、ライン&スペースパターンのエッチングを実行するものである。

(もっと読む)

半導体装置

【課題】小型化が可能な不揮発性メモリを備えた半導体装置を提供する。

【解決手段】基板901上に画素と不揮発性メモリとを備え、不揮発性メモリは、基板901上に形成される半導体活性層と、半導体活性層上に形成される絶縁膜923と、絶縁膜923上に形成されるフローティングゲイト電極907と、フローティングゲイト電極907を酸化して得られる酸化膜908,915,922と、酸化膜908,915,922に接して形成されるコントロールゲイト電極929と、を備え、画素と不揮発性メモリとは、基板901上に一体形成される。

(もっと読む)

半導体素子及びその製造方法

【課題】半導体素子のビア構造物及び導電構造物を提供する。

【解決手段】前記ビア構造物は、平坦部及び突出部を含む表面を有する。前記導電構造物は前記平坦部のうち、少なくとも一部上に形成され、前記突出部のうち、少なくとも一部上には形成されない。例えば、前記導電構造物は前記平坦部上のみに形成されて前記突出部上には全く形成されない。これによって、前記導電構造物と前記ビア構造物との間に高品質の接続を形成することができる。

(もっと読む)

半導体素子、及びその形成方法

【課題】 信頼性が向上する半導体素子、及びその形成方法を提供する。

【解決手段】 半導体素子の形成方法は、半導体基板100の上にゲート電極120及びゲート電極120の両側にスペーサー110を形成する段階、ゲート電極120の上にキャッピングパターン170を形成する段階、ゲート電極120の間にメタルコンタクト195を形成する段階を含み、キャッピングパターン170の幅はゲート電極120の幅より大きく形成される。これにより、形成された半導体素子は、メタルコンタクト195とゲート電極120との間での電気的な短絡を效果的に防止することができる。

(もっと読む)

不揮発性半導体記憶装置

【課題】積層されるチップ数が増加した際にワイヤボンディング数の増加を抑制でき、さらにインダクタ素子の形成によるチップ面積の増大を抑制できる高速なインタフェースを有する不揮発性半導体記憶装置を提供する。

【解決手段】信号を送受信するインダクタ素子ID1を有するNANDチップNC1と、信号を送受信するインダクタ素子ID0を有するNANDチップNC0と、NANDチップNC1,NC0の動作を制御する制御回路が形成され、インダクタ素子ID1,ID0との間で信号を送受信するインダクタ素子IDCを有する制御用チップCC0とを備える。インダクタ素子ID1,ID0の外周は、インダクタ素子IDCの外周をインダクタ素子IDCを含む平面に垂直な方向に延長した閉空間に含まれ、インダクタ素子IDCのインダクタンスは、インダクタ素子ID1あるいはID0のインダクタンスの少なくともいずれか一方より大きい。

(もっと読む)

半導体表示装置

【課題】作製工程を複雑化させることなく、高集積化を実現することが可能な、DRAM混載の集積回路の提供。

【解決手段】DRAMを有する集積回路であって、DRAMには、薄膜トランジスタを備えたメモリセルが複数設けられており、薄膜トランジスタは、活性層と、活性層が有するチャネル形成領域を間に挟んで重なり合っている第1の電極及び第2の電極とを有しており、データに従って薄膜トランジスタのドレイン電圧を制御することで、チャネル形成領域における正孔の蓄積の有無を選択し、正孔の蓄積の有無を把握することでデータを読み出すことを特徴とする集積回路。

(もっと読む)

半導体装置

【課題】高周波動作向けの半導体装置を高性能化させる。

【解決手段】シリコン基板S1上に形成された抵抗素子TDR1および不揮発性メモリNVM1を有する半導体装置であって、不揮発性メモリNVM1は、シリコン基板S1上に埋め込み酸化層BOX1を介して配置されたシリコン層SOI1に形成されている。特に、抵抗素子TDR1と不揮発性メモリNVM1とは互いに電気的に接続され、不揮発性メモリNVM1のオン状態またはオフ状態により、抵抗素子TDR1の導通状態または非導通状態が切り替わる。

(もっと読む)

情報処理方法、積層型集積回路メモリ

【課題】メモリの単位メガバイト当たり製造コストを、単にモノリシック回路集積法で慣用的に製造される回路の数分の一に低減させる。

【解決手段】各層が別々に最適化されるように、別々の層(103)上へのメモリ回路(103)および制御論理回路(101)の物理的分離が可能な三次元(3DS)メモリ(100)。幾つかのメモリ回路(103)について1つの制御論理回路(101)で十分であり、コストを低減できる。3DSメモリ(100)の製造は、メモリ回路(103)を50μm以下の厚さに薄肉化する工程と、該メモリ回路を、ウェーハ基板形態のまま回路積層体に接合する工程とを有する。微粒子の高密度層間垂直バス相互接続部(105)が使用されている。3DSメモリ(100)製造方法は、幾つかの性能および物理的サイズ効率を可能にしかつ確立された半導体加工技術により実施される。

(もっと読む)

半導体装置

【課題】オフ電流が小さい薄膜トランジスタによって問題なく動作することが可能な記憶素子を含む記憶装置を提供することを課題とする。

【解決手段】酸化物半導体層を有する薄膜トランジスタが少なくとも一つ設けられた記憶素子を、マトリクス状に配置した記憶装置を提供する。酸化物半導体層を有する薄膜トランジスタは、電界効果移動度が高く、且つオフ電流を小さくできるため、問題なく良好に動作させることができる。また、消費電力を低くすることもできる。このような記憶装置は、例えば酸化物半導体層を有する薄膜トランジスタが表示装置の画素に設けられている場合に、記憶装置を同一基板上に形成することができるため、特に有効である。

(もっと読む)

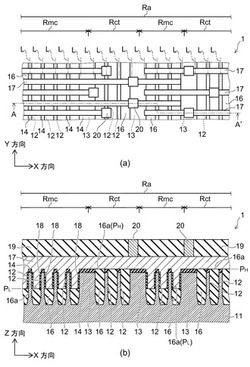

半導体装置

【課題】複数の回路ブロックを効率よくレイアウトする。

【解決手段】X方向に沿って配列された複数の不揮発性記憶素子110と、不揮発性記憶素子110のそれぞれに割り当てられた複数の比較回路120と、複数の比較回路120に対して共通に割り当てられた判定回路130とを有する回路ブロック100を複数備える。複数の回路ブロック100のうち、所定の回路ブロックに含まれる不揮発性記憶素子110は領域A1に配置されている。所定の回路ブロックに含まれる比較回路120及び判定回路130は、領域A1に対してY方向に位置する領域A2に設けられ、且つ、X方向に並べて配置されている。これにより、回路ブロックが整形された形状となることから、複数の回路ブロックを繰り返し配置する場合であっても、より一層の面積縮小を実現することが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】 抵抗素子の抵抗値の選択範囲を拡大し、且つ抵抗層形成後にシリサイドブロックを形成せずに該抵抗層のシリサイド化を防止することを可能にする。

【解決手段】 半導体領域11上に絶縁膜15を形成し、絶縁膜15を介して半導体領域11に不純物のイオン注入12を行う。これにより、絶縁膜15の下に抵抗層13が形成されるとともに、抵抗層13に隣接して電極領域14が形成される。その後、電極領域14の表面にシリサイド膜17を形成する。このとき、絶縁膜15は、抵抗層13がシリサイド化されることを防止するシリサイドブロックとして機能する。イオン注入12として、同一半導体基板上に形成されるMOSトランジスタのソース/ドレイン領域への不純物注入工程を利用し得る。

(もっと読む)

電気フューズメモリを有する半導体デバイス

【課題】電圧供給のための構成が占める占有面積が小さく、かつ、高精度な電圧供給が可能な電気フューズメモリを提供する。

【解決手段】フューズ素子Fと第1トランジスタTRBを含むメモリセルMCと、外部端子PADと、第2トランジスタTRAと、を有する。N型の第1トランジスタとフューズ素子Fが互いに直列接続されている。外部端子PADは、フューズ素子Fの一方の端子側に外部電圧VFUSEを供給する端子である。第2トランジスタTRAは、フューズ素子Fの他方の端子側に内部電圧GNDを供給するN型のトランジスタである。

(もっと読む)

相変化メモリデバイスを有する分圧器を含む不揮発性メモリ回路

第一相変化メモリ(PCM)デバイス、および第一PCMデバイスに結合された第二PCMデバイスを有する分圧器を含むメモリ回路を記述する。1つの実施形態では、第一PCMデバイスはセット抵抗の状態にあり、第二PCMデバイスはリセット抵抗の状態にある。また、1つの実施形態では、分圧器は、更に、第一PCMデバイスに接合された第一スイッチ、ならびに第一スイッチおよび第二PCMデバイスに結合された第二スイッチを含む。1つの実施形態では、メモリ回路は、更に、分圧器に結合されたハーフラッチ、ならびにハーフラッチおよび分圧器に結合されたカスケードトランジスタを含む。  (もっと読む)

(もっと読む)

相変化メモリのFEOLプロセスフローにおける回路及びメモリアレイの相対的高さの制御

【課題】相変化メモリのFEOLプロセスフローにおいて回路及びメモリアレイの相対的高さを制御する。

【解決手段】PCM部分が埋設されたCMOS論理部分は、ゲート酸化物及びポリシリコンゲートの厚みで測定されたゲート構造体の高さだけリセス加工されて、CMOS論理部分とPCM部分との平坦性を与える。

(もっと読む)

半導体装置およびその製造方法

【課題】スプリットゲート構造のMONOS型不揮発性メモリセルを有する半導体装置において、信頼度を低減することなく高集積化を実現する。

【解決手段】メモリ用nMISのメモリゲート電極MGの高さを選択用nMISの選択ゲート電極CGの高さよりも20〜100nm高く形成することにより、メモリゲート電極MGの片側面(ソース領域Srm側の側面)に形成されるサイドウォールSW1の幅を、所望するメモリセルMC1のディスターブ特性を得るために必要とする大きさとする。また、周辺用第2nMIS(Q2)のゲート電極G2の高さを選択用nMISの選択ゲート電極CGの高さ以下とすることにより、ゲート電極G2の側面に形成されるサイドウォールSW3の幅を小さくして、シェアードコンタクトホールC2の内部がサイドウォールSW3により埋め込まれるのを防ぐ。

(もっと読む)

1 - 20 / 47

[ Back to top ]