Fターム[5F064BB01]の内容

ICの設計・製造(配線設計等) (42,086) | ICの機能 (7,082) | デジタル信号処理 (4,646)

Fターム[5F064BB01]の下位に属するFターム

論理ゲート (2,166)

CPU (274)

ワンチップマイコン (28)

メモリ (1,165)

アドレスデコーダ (88)

シフトレジスタ (70)

フリップフロップ (730)

カウンタ、分周器 (66)

Fターム[5F064BB01]に分類される特許

1 - 20 / 59

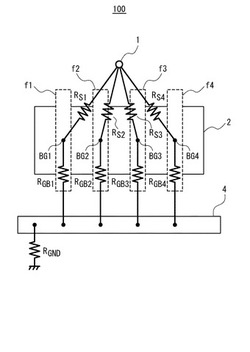

ノイズ解析モデル及びノイズ解析方法

【課題】解析対象回路内に設けられた素子のそれぞれに対する基板ノイズの影響を解析することができるノイズ解析モデル及びノイズ解析方法を提供すること。

【解決手段】本発明の一態様にかかるノイズ解析モデル100は、抵抗RS1〜RS4、抵抗RGB1〜RGB4及び接地抵抗RGNDを有する。抵抗RS1〜RS4は、ノイズ発生源から半導体基板を介して基板ノイズが伝搬する接続点1と、バックゲート直下の半導体基板中の点BG1〜BG4の間にそれぞれ接続される。抵抗RGB1〜RGB4は、バックゲート直下の半導体基板中の点BG1〜BG4とガードバンド4との間に接続される。接地抵抗RGNDは、ガードバンド4と接地電位との間に接続される。

(もっと読む)

消費電流算出装置、消費電流算出プログラムおよび消費電流算出方法

【課題】ミックスドシグナル回路の消費電流を短時間で見積もること。

【解決手段】消費電流算出装置100は、対象回路へ入力されるデジタル信号の値113と、デジタル信号とともに対象回路へ入力されるアナログ信号の値112と、を取得する。消費電流算出装置100は、デジタル信号の値113およびアナログ信号の代表値の組み合わせごとに組み合わせが入力された場合の対象回路の消費電流を示す消費電流テーブル114から、デジタル信号の値113が対象回路へ入力された場合のアナログ信号の各代表値と消費電流との対応情報115を抽出する。消費電流算出装置100は、抽出した対応情報115に基づいて、アナログ信号の各代表値の間の値に対応する対象回路の消費電流を補間する補間関数116を生成し、生成した補間関数116に基づいて、アナログ信号の値112に対応する対象回路の消費電流117を算出する。

(もっと読む)

基板ノイズ解析装置

【課題】 本発明の課題は、被ノイズ回路において影響を受けるノイズの大きさに基づいて効率的に基板ノイズ解析を行うことを目的とする。

【解決手段】 上記課題は、導体集積回路の回路ブロック毎に該回路ブロックの回路データを用いてノイズ源解析を行い、各周波数と該周波数に対するノイズ量とを対応させたノイズ源情報を出力するノイズ源解析手段と、回路ブロック毎に該回路ブロックの回路データを用いて各周波数に対して出力ノードから出力される該周波数の振幅をノイズの影響の大きさを示す感度として解析するノイズ感度解析を行い、各周波数と該周波数に対する感度とを対応させたノイズ感度情報を出力するノイズ感度解析手段と、前記ノイズ源情報と前記ノイズ感度情報とに基づいてノイズを受ける被ノイズ回路の動作に影響を与える周波数成分を特定し、該ノイズ源情報から該周波数成分を抽出するノイズ源情報抽出手段とを有する基板ノイズ解析装置により達成される。

(もっと読む)

半導体装置

【課題】RDRに従い設計され、活性領域と電源配線との境界部や周辺部における不具合の発生が抑制された、小型化かつ高集積化された半導体装置を提供する。

【解決手段】少なくとも1つのスタンダードセル内における半導体基板SBの主表面に形成される第1導電型の機能素子用不純物領域Apと、電源電位が印加される第2導電型の電源電位用不純物領域Anとを備える。半導体基板SBの主表面上に形成され、かつ半導体基板SBの主表面に達する貫通孔SCTHを有する絶縁層II1、II2と、絶縁層II1、II2の貫通孔内に形成されたコンタクト用導電層PCLとを備える。上記機能素子用不純物領域Apと電源電位用不純物領域Anとをまたぐように形成されるコンタクト用導電層PCLを通じて電気的に接続される。

(もっと読む)

半導体集積回路およびそのパターンレイアウト方法

【課題】CMP処理においてダミーパターンに機械的ストレスが作用しても、ダミーパターンが折れ曲がったり、ダミーパターンの一部が欠落したりすることを抑制できる半導体集積回路およびそのパターンレイアウト方法を提供する。

【解決手段】半導体集積回路は、所定の機能領域と、空き領域SP1に形成されたダミーパターンDMP1とを備える。空き領域SP1は、所定の機能領域同士の間に位置する。ダミーパターンDMP1は、枠状に形成されるとともに、ダミーパターンDMP1の外縁EDを規定する第1メタル部MT1と、第1メタル部MT1の内周側に位置し、第1メタル部MT1に連続するように形成された第2メタル部MT2と、第1メタル部MT1の内周側において第2メタル部MT2が形成されていない領域に位置する複数の非形成領域NTと、を有する。

(もっと読む)

半導体装置の電源配線レイアウト方法及び電源配線レイアウト装置

【課題】基板ノイズ違反を解消しつつ、半導体集積回路の大型化を抑制することができる半導体装置の電源配線レイアウト方法。

【解決手段】アナログ回路とデジタル回路とが混載された半導体集積回路の電源配線レイアウト方法。電源配線を、複数のノードと、それぞれが互いに隣接するノード間に配置された複数の要素抵抗と、を含む解析モデルとしてモデル化し、回路シミュレーションにより各複数のノードにおける電圧値を求め、アナログ回路のノードの電圧値に基板ノイズ違反がある場合、デジタル回路のノードのうち当該アナログ回路のノードへ流れ込む電流量が最大となる最大電流ノードを探索し、デジタル回路において最大電流ノードへ流れ込む電流経路を探索し、複数の要素抵抗のうち、電流経路に含まれる要素抵抗からボトルネック要素抵抗を選択し、ボトルネック要素抵抗の抵抗値を変更する。

(もっと読む)

半導体装置

【課題】ノイズが高周波である場合においても、多層配線層を介してデジタル回路とアナログ回路の間でノイズが伝播することを抑制する。

【解決手段】回路分離領域40は第1回路領域20と第2回路領域30の間に位置している。回路分離領域40には複数の第1導体及び複数の第1ビアが設けられている。複数の第1導体は、電源ライン110より下層に設けられ、電源ライン110に対向しており、かつ繰り返し配置されている。複数の第1ビアは多層配線層の中に、複数の第1導体それぞれごとに設けられており、各第1導体を電源ライン110に接続している。

(もっと読む)

半導体装置

【課題】機能回路の電源配線及び接地配線に要する接地面積を少なくし、同時に消費電流による電源電圧降下及び接地電圧上昇を抑えることで、薄型・軽量・高機能・低価格の半導体装置を提供する。

【解決手段】機能回路に電源電圧を供給する電源配線1009及び接地電圧を供給する接地配線1010が格子状に配置されている半導体装置である。格子状にすることで、電源電圧降下及び接地電圧上昇は大幅に低減できる。また、配線幅を細くしても、格子状にしない場合と同程度の電源電圧降下及び接地電圧上昇に抑えられるので、電源配線及び接地配線の配置面積を大幅に低減できる。

(もっと読む)

コントローラ

【課題】プログラマブルロジックデバイスにおけるコンフィギュレーションデータのエラーを確実に検出すること。

【解決手段】 論理モジュールを構築する複数のコンフィギュレーションデータのCRCエラーを検出するCRCチェッカを備えたプログラマブルロジックデバイスを有し、プロセス制御における制御対象を制御するコントローラにおいて、定期的に前記複数のコンフィギュレーションデータの擬似エラーを生成してエラー検出状態を作り出し、前記CRCチェッカが前記擬似エラー以外のエラーを検出すると前記論理モジュールのリセット要求信号を出力するとともに前記プログラマブルロジックデバイスへのアクセスを停止する演算制御手段と、前記演算制御手段と前記プログラマブルロジックデバイスとのアクセスが停止すると前記論理モジュールのリセット要求信号を出力する第1のウォッチドッグタイマを、備えることを特徴とする。

(もっと読む)

半導体集積回路

【課題】PKGの設計期間を遅延させることなくクロストーク耐性を向上させることが可能な半導体集積回路を提供する。

【解決手段】複数の信号配線を有するChip20において、一の信号配線と前記一の信号配線に隣接する一方の隣接信号配線と前記一の信号配線に隣接する他方の隣接信号配線との間で生じるクロストークの発生量を抑制するための補正係数31と、前記一の信号配線に送出される一の信号、前記一方の隣接信号配線に送出される一方の隣接信号、および前記他方の隣接信号配線に送出される他方の隣接信号の組み合わせパターンと、に基づいて、前記一の信号のスルーレートの低減度合を示す補正量を演算する補正量演算部42a〜42cと、前記補正量に基づいて、前記一の信号のスルーレートを調整するドライバ41a〜41cと、を備える。

(もっと読む)

設計支援プログラム、設計支援装置、および設計支援方法

【課題】局所的に高温となる領域の温度を低下させること。

【解決手段】

設計支援装置は、設計対象回路のレイアウトデータ100内で所定温度以上となる領域1を有する熱解析結果と、当該レイアウトデータ100内のパスに関する解析結果とを取得する。そして、領域1内に配置されているセルの中から非クリティカルパス上の任意のセルを領域1の温度を低下させる対象セルに決定し、決定結果を出力する。つぎに、決定された対象セルに対して温度を低下させる処理を実施する。対象セルの出力に抵抗素子を接続させる。または、対象セルの配置位置を領域1の外に再配置させるか、対象セルのセルタイプを消費電力値の低いセルタイプに変換する。

(もっと読む)

電子回路の階層的次数ランキングされたシミュレーション

【課題】集積回路設計をシミュレートする方法を提供する。

【解決手段】本発明の方法では、ネットリストにおけるノードのノード次数ランキングを決定することができる。ネットリストの回路は、ノード次数ランキングに基づいて静的及び動的電流駆動方式でパーティショニングされることができる。ノード次数パーティショニングに基づいて階層データ構造が構築されることができる。一実施形態では、シミュレーション最適化のために中間ノード次数を動的に結合することができる。その後、回路を1若しくは複数の結合された中間ノード次数に基づいて再パーティショニングすることができる。階層データ構造を用いて求解及び積分を行い、次数ランキングされた階層エンジンを生成することができる。次数ランキングされた階層エンジンについての解析を行うことができる。この時点で、解析に基づいてIC設計のシミュレーションデータがエクスポートされることができる。

(もっと読む)

等価性検証プログラム、等価性検証プログラムを記録したコンピュータ読み取り可能な記録媒体、等価性検証装置、および等価性検証方法

【課題】アナログ回路とその特性モデルとの等価性を効果的かつ容易に検証することができる等価性検証プログラム、等価性検証プログラムを記録したコンピュータ読み取り可能な記録媒体、等価性検証装置、および等価性検証方法を提供する。

【解決手段】アナログ回路およびその特性モデルについてそれぞれ自動的に検証環境を構築し(ステップS120)、構築した検証環境に基づきGUIを用いてテストシナリオを作成する(ステップS130)。次いで、作成したテストシナリオからシミュレーションを行い(ステップS140)、得られたシミュレーションログから等価性を判断するための情報を表として記載したテキストデータに変換し(ステップS150)、比較する(ステップS160)。

(もっと読む)

クロック分配回路及びクロックスキュー調整方法

【課題】消費電力とクロックスキューを最小限に抑える。

【解決手段】クロック分配回路は、クロック分配領域に格子状に配置され、クロックメッシュを駆動する複数のクロックドライバと、各クロックドライバに対して格子状に割り当てた分割領域毎に、クロックドライバが駆動するクロックメッシュの配線容量及びクロックメッシュに接続した回路素子のクロック端子容量を抽出し、分割領域毎に抽出した総容量から必要なクロックドライバの駆動力を割り出して、ディジタルデータとして保持するクロックドライバ駆動力保持回路と、各分割領域内で必要なクロックドライバの駆動力保持データと、上下方向及び左右方向の分割領域内で必要なクロックドライバの駆動力保持データとをそれぞれ分割領域毎の抵抗比率により平均化して、クロックドライバの駆動力を調整するクロックドライバ駆動力制御回路とを有する。

(もっと読む)

ルックアップテーブル、半導体集積回路、ルックアップテーブルの製造方法、および半導体集積回路の製造方法

【課題】製造が容易で集積度が高く動作の速い低廉なルックアップテーブルを短期間で開発すること。

【解決手段】

ルックアップテーブル200は、入力端子101と、出力端子102と、入力端子101の個数により決定される入力パターン数に対応したビア挿入箇所と、トランジスタにより構成される選択回路と、プリチャージ回路とを備える。ビア挿入箇所は、単一のビア層が有している。ビア挿入箇所の中から組合せ回路に応じてビアが挿入され、挿入されたビアを介して入力端子101と出力端子102とが接続される。入力端子101に入力される入力パターンが、ビアが挿入されたビア挿入箇所に対応している場合、出力端子102にはVSSが出力される。入力端子101に入力される入力パターンが、ビアが挿入されたビア挿入箇所に対応していない場合、出力端子102にはプリチャージ回路によりVDDが出力される。

(もっと読む)

半導体装置

【課題】チップサイズパッケージのように半導体基板上に再配線と外部接続端子とを形成するパッケージにおいて、再配線を短く形成して、回路ブロック間のアイソレーションを高めるように半導体基板の中央部にPADを配置する場合にも、ウエハ検査プローブが相互に接触することがないように対策する。

【解決手段】半導体装置を構成する半導体基板2を縦方向及び横方向に2分割して、半導体基板2を合計4つの四角形状の領域である回路領域a 101、回路領域b 102、回路領域c 103、回路領域d 104に区分する。前記4つに区分された回路領域では、各々、外周に沿って複数個のPAD200が配置される。

(もっと読む)

レイアウト設計方法および半導体集積回路

【課題】パッド律則とコア律則を意識しないレイアウト設計を容易に実現し、半導体集積回路の面積の縮小化とコストの低減化を図ること。

【解決手段】レイアウト設計装置300は、設計対象回路の回路情報の入力を入力部301により受け付け、入力された回路情報に含まれているコアの領域が確保された設計対象回路のレイアウト情報を生成部302が生成する。生成されたレイアウト情報上のコアの領域以外の領域に、回路情報に含まれているI/O回路をレイアウト部303により配置および配線する。回路情報に含まれているパッドの配置可能領域を決定部308により作成したレイアウト情報上に決定する。必要配置数分のパッドの総面積が配置可能領域の面積を超えない最大の大きさに、パッドの面積を最適化部309により最適化する。最適化されたパッドを配置部310により配置可能領域に配置する。

(もっと読む)

半導体集積回路

【課題】機能を柔軟に制御可能なアナログの機能ICを提供する。

【解決手段】アナログブロック10は、所定のアナログ信号処理を実行する。デジタルブロック20は、再構成可能に構成され、所定のデジタル信号処理を実行してアナログブロック10を制御する。FeRAM30は、デジタルブロック20の回路構成のコンフィギュレーションデータを格納する。機能IC100は、FeRAM混載プロセスを用いてひとつの半導体基板上に一体集積化され、アナログブロック10の動作状態が、デジタルブロック20の構成状態に応じて変更可能である。

(もっと読む)

配線のレイアウト方法及びプログラム

【課題】公知文献の方法には、集積回路の消費電力を過大に見積もっているという課題があった。

【解決手段】集積回路の電源配線をレイアウトする工程と、信号配線をレイアウトする工程と、比較する工程と、分類する工程と、求める工程と、修正する工程とを具備する配線のレイアウト方法によって解決できる。比較する工程においては、信号配線の信号周波数を、所定の基準周波数と比較する。分類する工程においては、信号配線を、基準周波数以上の信号周波数の信号配線で構成される第一のグループと、基準周波数よりも低い信号周波数の信号配線で構成される第二のグループとに分類する。求める工程においては、第一のグループに分類された信号配線で消費される電力に基づく温度上昇を除外して、集積回路における温度上昇の評価値を求める。修正する工程においては、評価値が所定の許容値を超えていた場合に、集積回路のレイアウトを修正する。

(もっと読む)

半導体装置

【課題】基板上に形成された第1導電型のウェルと第2導電型のウェルとの間でデカップリング容量を形成する際に、高い周波数まで追随できるようにする。

【解決手段】半導体装置100は、P型基板102上に形成された埋込Pウェル104と、その上に形成され、互いに隣接して交互に設けられた複数のPウェル106および複数のNウェル108と、を含む。各Nウェル108が埋込Pウェル104と接する領域の幅は、2μm以下である。Pウェル106およびNウェル108には、それぞれ接地電圧および電源電圧が印加される。Nウェル108と埋込Pウェル104との間でデカップリング容量が形成される。

(もっと読む)

1 - 20 / 59

[ Back to top ]