Fターム[5F064BB20]の内容

ICの設計・製造(配線設計等) (42,086) | ICの機能 (7,082) | デジタル信号処理 (4,646) | カウンタ、分周器 (66)

Fターム[5F064BB20]に分類される特許

1 - 20 / 66

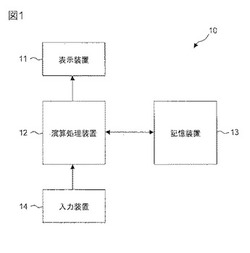

レイアウト装置及びレイアウト方法

【課題】クロックツリーにおけるクロックスキューの調整において、精度の確保とデューティ保持とを両立させる。

【解決手段】レイアウト装置(10)において、MOSトランジスタ1段で形成された第1セルと、MOSトランジスタ複数段で形成された第2セルとがライブラリ化されたテーブルを設ける。また、上記レイアウト装置には、上記第1セルと上記第2セルとの組み合わせによるコンビネーションチェーンを上記クロックツリーに挿入することで、上記クロックツリーにおける異なるクロック系統間のクロックスキューを調整可能な演算処理部(12)を設ける。上記コンビネーションチェーンによってクロックスキューの調整を行うことで、個々の第1セルでの遅延誤差が伝播されるのを抑制し、遅延計算における遅延誤差の低減を図る。また、第1セルはMOSトランジスタ1段で形成され、そこで論理反転されるため、デューティ保持の観点で有利とされる。

(もっと読む)

半導体装置および電源供給方法

【課題】消費電力を低減することが可能な半導体装置および電源供給方法を提供することである。

【解決手段】本発明にかかる半導体装置は、内部回路3に電源を供給する電源供給部4と、内部回路3の複数の場所における特性をモニタする複数のモニタ部1_1〜1_Nと、複数のモニタ部1_1〜1_Nから出力された信号C_1〜C_Nに基づき算出されたモニタ値C_AVEと、設定された比較値COMPとの比較結果に応じて電源供給部4を制御する制御部2と、を備える。制御部2は、複数のモニタ部1_1〜1_Nにおける特性のばらつきに応じて比較値COMPを設定する。

(もっと読む)

半導体装置

【課題】少しの設計方法の変更で設計できる、一層低消費電力化した半導体装置の実現。

【解決手段】複数の電源供給領域23と、複数の電源供給領域に供給する電源の電圧を切り替える複数の電源切替ユニットSWA,SWBと、を有し、複数の電源供給領域に含まれる回路要素を組み合わせて少なくとも1つの機能ブロックが形成され、少なくとも1つの機能ブロックは、内部に異なる電圧で動作する回路要素を含む半導体装置。

(もっと読む)

半導体集積回路設計方法

【課題】LSIに搭載された複数のマクロ間のクロックスキューを低減する設計方法を提案する。

【解決手段】本発明の半導体集積回路設計方法は、複数の下層回路を含む集積回路の回路情報に基づいて、下層回路に含まれるフリップフロップにクロックを供給する論理回路の出力をクロックポイントとして抽出し、抽出したクロックポイントを出力とする論理回路の回路構成を認識し、抽出したクロックポイントのうち、第1下層回路からクロックポイントを選択し、第2下層回路からクロックポイントを選択し、それぞれのクロックポイントを出力とする論理回路の回路構成を比較し、比較結果が一致した場合、選択された2つクロックポイントを出力する論理回路の一方を削除すると共に、削除した一方のクロックポイントを他方の論理回路の出力とすることにより、2つのクロックポイントを共通化する。

(もっと読む)

半導体装置

【課題】ウエハーテストにおいて、キャリブレーション動作の評価を、容易、かつ高精度に行うことができる半導体装置を提供する。

【解決手段】キャリブレーション端子ZQを駆動するレプリカバッファ(131)と、レプリカバッファの出力インピーダンスを変化させる際に目標となるインピーダンスが設定され、キャリブレーション端子ZQに接続される可変インピーダンス回路(170)と、を備える。

(もっと読む)

クロックツリー生成方法、クロックツリー生成プログラム、記録媒体、およびクロックツリー生成装置

【課題】外部電源電圧が変動した場合でも、安定に動作する半導体装置を実現することが可能なクロックツリー生成方法を提供する。

【解決手段】プログラム5のCTS部8は、電源領域Aから電源領域Bにクロック信号CLK1,CLK2を伝達する経路L1,L2を設け、電源領域A内の経路L1,L2にそれぞれアンカーバッファB1,B2を配置し、遅延回路D1,D2を電源領域B内の経路L1,L2にそれぞれ配置し、遅延回路D3,D4をアンカーバッファB1,B2の入力ノード側の経路L1,L2にそれぞれ配置する。したがって、外部電源電圧VDD1,VDD2が変動した場合でも、クロック信号CLK1,CLK2の遅延時間は同じになる。

(もっと読む)

I/O積層体を含むシステム及びこのシステムを製造する方法

【課題】入出力(I/O)積層体を含むシステムを提供する。

【解決手段】入出力(I/O)積層体を含むシステム及びこのシステムを製造する方法が記述されている。一実装において、本方法は、I/O素子を含むと共に論理素子を含まないI/Oダイを積層するステップを有する。又、一実装において、本方法は、I/Oダイに対して集積回路ダイを積層するステップを更に含む。集積回路は、論理素子を含み、且つ、I/O素子を含まない。集積回路ダイからI/Oダイを分離することにより、それぞれのダイの独立的な開発や従来のダイのものとの比較におけるI/OダイのI/O基板上のI/O素子用の相対的に大きな空間などの様々な利益が得られる。空間の増大により、多数の論理素子を集積回路ダイの基板の同一の表面積内に収容する集積回路ダイの新しいプロセス世代が可能となる。

(もっと読む)

半導体装置

【課題】タイミングエラーに起因する動作不良を低減した半導体装置の実現。

【解決手段】組合せ回路11A-11Cと、クロックCLKに応じて、組合せ回路が出力するデータを取り込んで保持する1個以上の記憶素子2A-2Dと、クロックを供給するクロック信号線3と、を備え、少なくとも1個の記憶素子は、記憶素子に供給するクロックを遅延させ、遅延時間が可変の少なくとも1個の可変遅延素子11A,11Bを、備え、可変遅延素子が出力する遅延クロックに応じて、当該記憶素子が正常に動作するか否かを検出し、正常に動作するか否かの検出結果に応じて可変遅延素子の遅延時間を変化させるタイミングエラー検出機能付き記憶素子である半導体装置。

(もっと読む)

半導体装置

【課題】本発明は単一半導体装置を構成する複数個のチップでヒューズ信号を伝送できる半導体装置を提供する。

【解決手段】半導体装置は伝送制御信号生成部と、ヒューズ信号伝送部と、受信制御信号の生成部と、ヒューズ信号の受信部を備える。前記伝送制御信号生成部は、クロック信号を受信して複数個の分周クロック信号を生成し、前記複数個の分周クロックから伝送制御信号を生成する。前記ヒューズ信号の伝送部は前記伝送制御信号に同期してヒューズ信号を伝送する。前記受信制御信号生成部は前記クロック信号を受信して前記複数個の分周クロック信号を生成し、前記複数個の分周クロックから受信制御信号を生成する。前記ヒューズ信号受信部は前記受信制御信号に同期して前記ヒューズ信号を受信する。

(もっと読む)

貫通電極を有する積層構造の半導体装置、半導体メモリ装置、半導体メモリ・システム及びその動作方法

【課題】貫通電極を有する積層構造の半導体装置、半導体メモリ装置、半導体メモリ・システム及びその動作方法を提供する。

【解決手段】複数の半導体レイヤ間で伝送される情報の衝突を防止する構造を有する半導体装置であり、該半導体装置は、第1温度情報を出力する第1温度センサ回路を含む少なくとも1つの第1半導体チップと、貫通電極に電気的に連結されずに、第1温度センサ回路に電気的に連結される第1バンプと、第1半導体チップの貫通電極に電気的に連結される第2バンプと、を具備する半導体装置であることを特徴とする。

(もっと読む)

プログラマブル・ゲートアレイ部を備えたマスクプログラマブル論理装置

【課題】プログラマブルゲートアレイ部を備えるマスクプログラマブル論理装置を提供すること。

【解決手段】集積回路の基板上に配置される複数のマスク−プログラマブル領域と、上記マスク−プログラマブル領域に結合されると共に上記マスク−プログラマブル領域を相互接続するために基板上に配置される複数の相互接続導体と、基板上に配置される複数のゲートアレイ部とからなり、ゲートアレイ部はマスクプログラマブル論理装置上の回路設計の実行を促進する少なくとも一つの機能を達成するようにプログラム可能である集積回路上に配置されるマスク−プログラマブル論理装置。

(もっと読む)

半導体集積回路装置

【課題】保護対象の回路ブロックの上に配置された導電パターンに加えられた改変の検出する精度を向上するための技術を提供することを目的とする。

【解決手段】半導体基板に形成された回路ブロックと、回路ブロックのうち保護対象の部分の上層に配置された導電パターンと、導電パターンに接続され、導電パターンの回路定数により決定される発振周波数で発振する発振回路と、発振回路の発振周波数が事前に設定された範囲に含まれるか否かを判定し、発振周波数が事前に設定された範囲に含まれない場合に、導電パターンに改変が加えられたことを検出する検出回路とを有することを特徴とする半導体集積回路装置が提供される。

(もっと読む)

抵抗値補償方法、抵抗値補償機能を有する回路、回路の抵抗値試験方法、抵抗値補償プログラム、回路の抵抗値試験プログラム及びシステム

【課題】簡易で精度の高いODT回路の抵抗補償方式を提供することを目的とする。

【解決手段】複数のトランジスタの組み合わせによって所望の抵抗値と同等の抵抗値を実現するODT回路200であって、組み合わせるべきトランジスタを順次選択することにより、選択されたトランジスタによって実現される抵抗値を順次変化させる構成である。

(もっと読む)

半導体装置

【課題】印加電圧の過剰による、アンチヒューズ素子の誤コネクトや書き込みが正確に行われないアンチヒューズ素子の発生を抑制する。

【解決手段】本発明の半導体装置は、アンチヒューズ素子の一端の電位AF_Gと電位VPPRとを比較し、電位AF_Gが電位VPPR以上の場合には、アンチヒューズ素子の一端に接続される電源線の電位VPPSVTを昇圧し、昇圧された電位によりアンチヒューズ素子の一端と他端とが導通状態となることで、電位AF_Gが電位VPPRよりも低くなった場合には、昇圧を停止する。

(もっと読む)

ヒューズ制御回路、ヒューズ制御システム、照度センサ、近接センサ、携帯電話、デジタルスチルカメラ、および電源回路

【課題】従来のヒューズ制御回路よりも回路規模が低減されたヒューズ制御回路、照度センサ、近接センサ、携帯電話、デジタルスチルカメラ、および電源回路を提供する。

【解決手段】ヒューズ制御回路1は、ヒューズ溶断回路2がヒューズ素子F1に電流を流すとき、ノードBとヒューズ溶断検知回路3とを切断するとともに、ヒューズ溶断回路2がヒューズ素子F1に電流を流さないとき、ノードBとヒューズ溶断検知回路3とを接続する分離用素子4を備える。

(もっと読む)

コントローラ

【課題】プログラマブルロジックデバイスにおけるコンフィギュレーションデータのエラーを確実に検出すること。

【解決手段】 論理モジュールを構築する複数のコンフィギュレーションデータのCRCエラーを検出するCRCチェッカを備えたプログラマブルロジックデバイスを有し、プロセス制御における制御対象を制御するコントローラにおいて、定期的に前記複数のコンフィギュレーションデータの擬似エラーを生成してエラー検出状態を作り出し、前記CRCチェッカが前記擬似エラー以外のエラーを検出すると前記論理モジュールのリセット要求信号を出力するとともに前記プログラマブルロジックデバイスへのアクセスを停止する演算制御手段と、前記演算制御手段と前記プログラマブルロジックデバイスとのアクセスが停止すると前記論理モジュールのリセット要求信号を出力する第1のウォッチドッグタイマを、備えることを特徴とする。

(もっと読む)

積層型半導体装置

【課題】積層された複数の半導体チップ間で貫通電極切替情報を共有する。

【解決手段】複数の半導体チップ間でデータ転送を行うための複数の貫通電極を互いに共有した積層型半導体装置であって、複数の半導体チップに含まれる第1の半導体チップIFは、複数の貫通電極のうちデータ転送を行う貫通電極を指定する貫通電極切替情報SWを保持し、複数の半導体チップに含まれる第2の半導体チップCC0〜CC7に貫通電極切替情報SWを転送する。本発明によれば、貫通電極切替情報SWが第1の半導体チップIFから第2の半導体チップCC0〜CC7に転送されることから、第2の半導体チップには貫通電極切替情報SWを不揮発的に記憶する回路を設ける必要がない。これにより、第2の半導体チップのチップ面積を縮小することが可能となる。

(もっと読む)

半導体集積回路およびパワーゲーティング制御方法

【課題】搭載される機能ブロックの個数によらず、一定数の少数の配線のみでパワーゲーティング制御を行うことのできる半導体集積回路およびパワーゲーティング制御方法を提供する。

【解決手段】パワーゲーティング制御情報生成部1が、機能ブロックBLK1〜BLK3に対するパワーゲーティング制御情報PGCを生成し、クロック信号制御部2が、クロック信号CK0にパワーゲーティング制御情報PGCを重畳し、機能ブロックBLK1〜BLK3へ供給するクロックとなるクロック信号CKを生成し、機能ブロックBLK1〜BLK3のそれぞれと一体に1個ずつ配置されたパワーゲーティング制御部31〜33が、クロック信号CKに重畳されたパワーゲーティング制御情報PGCを解読して、機能ブロックBLK1〜BLK3に対するパワーゲーティング制御信号PG1〜PG3をそれぞれ生成する。

(もっと読む)

半導体装置及びその製造方法

【課題】従来よりも少数のLEを用いてより小面積のDFFを構成できる、ビアパターンによって論理を変更可能な半導体装置及びその製造方法を提供すること。

【解決手段】半導体装置の製造方法は、

複数のトランジスタと、これらに接続された第1メタル層とが形成された基板において、第1メタル層の上に、第1ビアパターンを含む第1ビア層を形成する工程と、

第1ビア層の上に第2メタル層、第2ビア層および第3メタル層を形成する工程と、

第3メタル層の上に、第3ビアパターンを含む第3ビア層を形成する工程とを含み、

複数の前記トランジスタによって基本論理素子が構成され、

基本論理素子が、2つのN型トランジスタ及び2つのP型トランジスタ(CS2)と、1つのAOIゲート(AOI)と、2つのインバータ(INV)とを備え、

第1ビアパターンによって基本論理素子の論理を決定し、

第3ビアパターンによって基本論理素子間の配線を決定する。

(もっと読む)

半導体装置

【課題】回路構成を再構成可能であるとともに、同時に複数のアプリケーションを実行することを可能にする半導体装置を提供する。

【解決手段】コンフィグレーションデータの保持用及び演算処理の結果の保持用に同じバンク数のレジスタバンクを設け、バンク切り替え信号によりレジスタバンクのバンクを同期して切り替えるようにして、アプリケーションの切り替えに応じて、コンフィグレーションデータ及び処理に用いるデータを同期して切り替えて処理を実行可能にし、同時に複数のアプリケーションを実行できるようにする。

(もっと読む)

1 - 20 / 66

[ Back to top ]