Fターム[5F064BB16]の内容

ICの設計・製造(配線設計等) (42,086) | ICの機能 (7,082) | デジタル信号処理 (4,646) | アドレスデコーダ (88)

Fターム[5F064BB16]に分類される特許

1 - 20 / 88

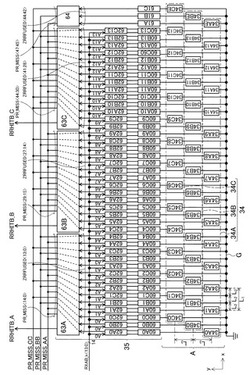

半導体装置及びトリミング方法

【課題】ヒューズ素子の列数増に伴うトリミング時間の伸長を抑制する。

【解決手段】x方向に延伸する接地配線Gと、接地配線のy方向の一方側に設けられたヒューズ素子領域Aにx方向に沿って3列に並べて配置され、かつそれぞれの一端が接地配線Gに共通に接続される複数のヒューズ素子と、ヒューズ素子領域Aを挟んで接地配線Gの反対側に設けられ、ヒューズ素子領域Aに配置された複数のヒューズ素子それぞれの他端と接続される救済回路とを備え、上記複数のヒューズ素子は、それぞれ1つの欠陥選択線を示すアドレス情報を記憶する複数のヒューズ素子グループに所定個ずつグループ化され、同一のヒューズ素子グループに属する所定個のヒューズ素子は、同一列に配置されることを特徴とする

(もっと読む)

半導体装置

【課題】配線間の寄生容量を削減可能にした半導体装置を提供する。

【解決手段】X方向に配列する複数のトランジスタについて、夫々が、対応するダミーゲートDG1,DG2を挟む複数のソース拡散層S1,S2に接続する第2及び第3の金属配線M12,M13は、2つのS1,2つのS2に夫々接続する複数の第1のビアV1の両方を含む第1の幅L1と、V1を含まず、L1よりも短い第2の幅L2と、を有する。ドレイン拡散層D1に接続する第1の金属配線M11と、M12との間、並びにM11及びM13の間の夫々は、L1に対応する第1のギャップSP1と、L2に対応する、L1よりも大きな第2のギャップSP2と、を有する。好ましくは、M11〜M13の夫々と第2のビアV2を介して接続される第4〜第6の金属配線M24〜M26の夫々は、L1よりも短い第3の幅L3を有する。

(もっと読む)

半導体ウエハ、半導体装置、および、半導体装置の製造方法

【課題】半導体チップのチップ面積の削減を図るとともに、半導体チップへの入力を記憶させる時間を短縮する。

【解決手段】本発明の半導体ウエハ1は、チップ領域10に形成され、絶縁膜を有し、電圧の印加による絶縁膜の絶縁破壊により導通状態となる複数のアンチヒューズ14を有するアンチヒューズ回路12と、チップ領域10を区画するダイシング領域20に複数のアンチヒューズ14の各々に対応して形成され、配線を有し、レーザー照射による配線の切断により非導通状態となる複数のレーザーヒューズ24を有するレーザーヒューズ回路22と、複数のアンチヒューズ14のうち、半導体チップへの入力に応じて非導通状態とされたレーザーヒューズ22に対応するアンチヒューズ14の有する絶縁膜に、電源からの電圧を印加させて、そのアンチヒューズ14を導通状態とする制御回路13と、を有する。

(もっと読む)

半導体装置

【課題】残渣による配線間のショートの発生を防ぐ。

【解決手段】本発明の半導体装置は、高誘電率材料を含む第1のゲート絶縁膜4と第1のゲート絶縁膜4上に形成された第1のメタルゲート電極5とを備える第1のトランジスタが形成される半導体基板上の第1の領域と、高誘電率材料を含む第2のゲート絶縁膜4と第2のゲート絶縁膜上に形成された第2のメタルゲート電極12とを備え、第1のトランジスタとは閾値電圧の異なる第2のトランジスタが形成される半導体基板上の第1の領域に並ぶ第2の領域と、電位の異なる第1および第2の配線と、を有し、第1の領域と第2の領域との境界が、第1および第2の配線の少なくとも一方としか重ならない。

(もっと読む)

半導体装置

【課題】複数の回路ブロックの特性を正確に一致させる。

【解決手段】例えば、端子31A,31Bと、これら端子間に設けられた回路110A,110Bを備える。回路110Aは端子31Aに接続され、端子31Aから端子31Bへ向かって配置されたセル120A,130A,140Aを含む。回路110Bは端子31Bに接続され、端子31Bから端子31Aへ向かって配置されたセル120B,130B,140Bを含む。セル120A,120Bのレイアウトは、形状、サイズ及び向きがトランジスタレベルで同一である。セル130A,130B及びセル140A,140Bのレイアウトは、形状及びサイズが同一であり、トランジスタの向きが180°相違している。これにより各セルを対称配置しつつ、センシティブなセル120A,120Bにおいては電流方向の違いによる特性差が生じない。

(もっと読む)

半導体装置

【課題】ウエハーテストにおいて、キャリブレーション動作の評価を、容易、かつ高精度に行うことができる半導体装置を提供する。

【解決手段】キャリブレーション端子ZQを駆動するレプリカバッファ(131)と、レプリカバッファの出力インピーダンスを変化させる際に目標となるインピーダンスが設定され、キャリブレーション端子ZQに接続される可変インピーダンス回路(170)と、を備える。

(もっと読む)

半導体集積回路装置

【課題】容易にカスタマイズ対応可能な半導体集積回路装置を提供する。

【解決手段】アレイ型プロセッサ部(300)は、プロセッサエレメント(330)とプログラマブルスイッチ(320)とを備えるプロセッサユニット(310)をマトリクス状に配置する。プロセッサエレメント(330)は、複数ビット幅の第1演算器(332)と複数ビット幅より狭い所定のビット幅の第2演算器(333)とを有する。第1演算器(332)および第2演算器(333)の接続構成は構成情報メモリ(340)に設定される構成情報に基づいて変更可能である。プログラマブルスイッチ(320)は、配線からプロセッサエレメントに複数ビット幅のデータおよび所定のビット幅のデータを構成情報に基づいて入出力する。制御回路(200)は、内部バス(180)に接続され、アレイ型プロセッサ部(300)の動作を制御し、内部バス(180)を介してデータを授受する。

(もっと読む)

半導体装置

【課題】半導体装置の電源線および接地線の高抵抗化を抑制する。

【解決手段】第1の方向に延伸された第1の回路セル列及び第2の回路セル列と、第1の方向に延伸され、第1の回路セル列上に配置され、第1の電源線には第1の電源電位が供給される、第1及び第2の電源線と、第1の方向に延伸され、第2の回路セル列上に配置され、第2の電源電位が供給される第3の電源線と、第2の電源線と第3の電源線との間に接続され、導通状態において第2の電源線と第3の電源線とを接続して第3の電源線から第2の電源線に第2の電源電位を供給し、非導通状態において第2の電源線と第3の電源線とを電気的に切り離す第1のトランジスタと、第1の回路セル列に配置され、第1の電源線から供給される第1の電源電位と第2の電源線から供給される第2の電源電位との間の電源電圧で動作する第1の回路素子とを備える。

(もっと読む)

半導体装置

【課題】周辺回路領域を整形された形状とすることによりチップ面積を縮小する。

【解決手段】Y方向に延在する複数のデータバスDBがピッチP1でX方向に配列されたメモリセル領域40と、対応する複数のデータバスDBにそれぞれ接続された複数のバッファ回路BCが設けられたバッファ領域61とを備える。バッファ領域61上においては、Y方向に延在する複数のデータバスDBがピッチP2でX方向に配列され、ピッチP2はピッチP1よりも小さい。本発明によれば、データバスDBの配列ピッチをバッファ領域上において縮小していることから、他の回路ブロックに割当可能な面積を十分に確保することが可能となる。これにより、当該回路ブロックの幅拡大や形状の変形が不要となることから、無駄な空きスペースが生じにくく、チップ面積を縮小することが可能となる。

(もっと読む)

可変遅延回路およびその制御方法

【課題】信号の遅延量を微調整可能な可変遅延回路を提供する。

【解決手段】可変遅延回路において、N個の可変論理回路を用いてN段のセレクタが直列接続される。1段目のセレクタSL1の2つの入力端子に信号が入力される際、入力信号が通過する2つの信号経路D1には経路差d1が存在している。また、2段目のセレクタSL2の2つの入力端子に信号が入力される際、入力信号が通過する2つの信号経路D2には、経路差d2が存在している。信号が通過する当該経路の組み合わせは、セレクタSLの段数に基づき、N段であるため2nとおりの信号経路の組み合わせが生じる。すなわち、2nとおりの切替信号R1〜Rnの組み合わせに基づいて2nとおりの信号経路が選択される。2nとおりの信号経路の組み合わせに基づく配線経路差に基づいて信号遅延量を調節する。

(もっと読む)

ランダム・アクセス電気的プログラム可能なEヒューズROM

【課題】ランダム・アクセス電気的プログラム可能なeヒューズROMを提供する。

【解決手段】1回プログラム可能な読み出し専用メモリ(OTPROM)が、アグレッシブにスケール縮小された、シリサイド移動可能なeヒューズの2次元配列において実施される。ワード・ライン選択は、VDDにおいて動作するデコード論理によって実施され、一方ビット・ライン・ドライブは、VDDとプログラミングのためのより高い電圧VPとの間でスイッチ切替えされる。OTPROMは、それゆえコストを加算することなしに他の技術と適合可能で、統合することができ、そして、ヒューズ・プログラミングの間、電圧降下を最小にする高電流経路の最適化をサポートする。プログラム可能参照を有する差動センス増幅器は、センス・マージンを改善するために使用され、個々のヒューズに設けられるセンス増幅器の代りに、ビット・ライン全体をサポートすることができる。

(もっと読む)

半導体装置

【課題】回路特性を調整するためのトリミング時間を短縮する。

【解決手段】切断ポイントが座標Y1に配列されたラダーヒューズLFAと、切断ポイントが座標Y2に配列されたラダーヒューズLFBとを備える。回路特性を調整するための補正データが第1の範囲内にある場合はラダーヒューズLFA,LFBの両方に対してトリミング動作を行い、回路特性を調整するための補正データが第2の範囲内にある場合はラダーヒューズLFAに対してトリミング動作を行うことなく、ラダーヒューズLFBに対してトリミング動作を行う。これにより、補正データが第2の範囲内である場合には、ラダーヒューズLFAに対してレーザ照射する必要がない。このため、例えば量産段階で必要となる調整範囲をラダーヒューズLFBに割当てれば、1回のスキャンでトリミングを完了することが可能となる。

(もっと読む)

半導体装置及びその制御方法

【課題】様々な導通状態にある複数の電気ヒューズを有する半導体装置において、複数の電気ヒューズによりプログラミングされた結果を誤判定なく読み出すことのできる半導体装置及び半導体装置の制御方法を提供する。

【解決手段】其々がプログラム状態又は非プログラム状態である複数のヒューズ素子と、複数のヒューズ素子のプログラム状態又は非プログラム状態に対応する判定結果信号FLDa,FLDbを其々出力する複数のヒューズ判定回路92a,92bと、第1のタイミング信号LOAD_ENDを共通に受け、第1のタイミング信号LOAD_ENDに同期して複数の判定結果信号FLDa,FLDbを其々ラッチ及び出力する複数のラッチ回路93a,93bとを備える。

(もっと読む)

半導体装置及びその制御方法

【課題】様々な導通状態にある電気ヒューズを其々誤判定なく読み出すことのできる半導体装置及び半導体装置の制御方法を提供する。

【解決手段】選択トランジスタ903を介して検出ノードAに接続された電気ヒューズ902と、選択トランジスタ903をオフさせた状態で検出ノードAをプリチャージするプリチャージトランジスタ904と、選択トランジスタ903をオンさせ、プリチャージトランジスタ904をオフさせた状態で、検出ノードAにバイアス電流を流すバイアストランジスタ905と、検出ノードAにバイアス電流が流れている状態で検出ノードAの電位を検出する検出回路906とを備え、バイアストランジスタ905は、バイアス電流の量を段階的又は連続的に減少させる。

(もっと読む)

半導体装置

【課題】コンタクトパッドを含む所定領域内に形成できる配線数を増加させることができ、設計レイアウトの自由度を向上させることができるパターンレイアウトを有する半導体装置を提供する。

【解決手段】第1方向に所定ピッチでラインとスペースが交互に配列された第1配線パターンと、第1配線パターンのライン間に配置され、所定ピッチの3倍の幅を有するコンタクトパッド30Bとを有する。第1配線パターンのラインとコンタクトパッドとの間隔は所定ピッチであり、所定ピッチは100nm以下である。

(もっと読む)

半導体装置

【課題】 半導体装置のレイアウト面積を大きくすることなく、内部電源回路の電流供給能力の向上を可能にする。

【解決手段】 半導体装置は、主領域12と、第1の方向に沿って主領域に形成された複数の第1の電源配線15と、第1の電源配線と交差しかつ電気的に接続されるように第2の方向に沿って主領域に形成された複数の第2の電源配線16と、第1の方向に関して主領域の一方の側に隣接する第1の隣接領域13に設けられ、第1の電源配線の一端にそれぞれ接続された第1の内部電源回路17と、第2の方向に関して主領域の一方の側に隣接する第2の隣接領域14に設けられ、複数の第2の電源配線のうち最も第1の電源配線の他端に近い電源配線の一端に接続された第2の内部電源回路18と、を備える。

(もっと読む)

不揮発性プログラマブルロジックスイッチおよび半導体集積回路

【課題】回路サイズを減少させることを可能にする。

【解決手段】素子分離領域102によって分離された、隣接する第1導電型の第1半導体領域101aおよび第2導電型の第2半導体領域101cと、第1半導体領域101a上に設けられた不揮発性メモリセルトランジスタ10と、第2半導体領域101c上に設けられ、第1半導体領域101aに設けられた第1ドレイン領域10bと電気的に接続されたゲート電極20C2とを有するパストランジスタ20と、第1半導体領域101aに設けられ第1半導体領域に基板バイアスを印加する第1電極8と、第2半導体領域101cに設けられ第2半導体領域に基板バイアスを印加する第2電極9と、を備えている。

(もっと読む)

半導体装置

【課題】低消費電力かつ低占有面積で、パッケージ実装後においてもプログラムを行なうことができるヒューズ素子を備えるヒューズプログラム回路を実現する。

【解決手段】ヒューズプログラム回路(FPK1−FPKn)において、ヒューズ素子FSを、多層メタル配線の第3層以上のメタル配線(M(i))を用いて実現する。各ヒューズプログラム回路において、スキャンフリップフロップ(FSSRおよびPSR)を用いてプログラム情報およびヒューズ選択情報を順次転送して、選択的に、1本ずつヒューズを電気的に切断する。

(もっと読む)

半導体装置の配線抵抗算出装置

【課題】配線に多数のスルーホールが存在する場合にも、多数のスルーホール分割要素に分割されることを回避し、分割要素の数の増大を抑制し、配線抵抗の算出時間を短縮する装置の提供。

【解決手段】第1配線層と第2配線層の配線を接続する複数のスルーホールを有する領域に、複数のスルーホールを含む枠図形FF1を設定し、枠図形を複数の枠領域FR1〜3に分割する。各枠領域内の複数のスルーホールを合成して1つのスルーホールにまとめ、各枠領域内にはそれぞれ1つの合成スルーホールCT1〜3が設定される。各枠領域に1つに設定されたスルーホールの位置を基準として、第1配線層、第2配線層における枠図形に対応する配線抵抗を分割した抵抗値RL11〜14、RL21〜22と、各枠領域内で1つに設定されたスルーホールの抵抗値RCT1〜3とを用いて、抵抗回路網を作成し、抵抗回路網を1つの抵抗RSに合成する。

(もっと読む)

半導体装置

【課題】印加電圧の過剰による、アンチヒューズ素子の誤コネクトや書き込みが正確に行われないアンチヒューズ素子の発生を抑制する。

【解決手段】本発明の半導体装置は、アンチヒューズ素子の一端の電位AF_Gと電位VPPRとを比較し、電位AF_Gが電位VPPR以上の場合には、アンチヒューズ素子の一端に接続される電源線の電位VPPSVTを昇圧し、昇圧された電位によりアンチヒューズ素子の一端と他端とが導通状態となることで、電位AF_Gが電位VPPRよりも低くなった場合には、昇圧を停止する。

(もっと読む)

1 - 20 / 88

[ Back to top ]