Fターム[5F064BB40]の内容

ICの設計・製造(配線設計等) (42,086) | ICの機能 (7,082) | その他 (40)

Fターム[5F064BB40]に分類される特許

1 - 20 / 40

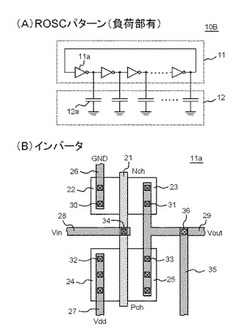

半導体装置、パラメータ最適化方法、及びプログラム

【課題】トランジスタの容量の各成分や配線容量を分離してパラメータを最適化することが可能な半導体装置、パラメータ最適化方法、及びプログラムを提供すること。

【解決手段】MOSトランジスタから構成されたプリミティブゲート回路11aを奇数段でリング状に結合した第1リングオシレータ部11の各前記プリミティブゲート回路の出力部と電気的に接続された負荷部12となる第1配線を有する配線負荷パターンと、第2リングオシレータ部の各プリミティブゲート回路の出力部が第2配線を介して負荷部となるMOSトランジスタのゲートに電気的に接続された複数のゲート負荷パターンと、第3リングオシレータ部の各プリミティブゲート回路の出力部が第3配線を介して負荷部となる拡散層に電気的に接続された複数の拡散層負荷パターンと、を備え、複数のゲート負荷パターンは、パターンごとに容量負荷が異なり、複数の拡散層負荷パターンは、パターンごとに容量負荷が異なる。

(もっと読む)

半導体集積回路装置

【課題】過電流に対して内部回路を保護する半導体集積回路装置を提供することを目的としている。

【解決手段】多層配線構造を有する半導体集積回路装置であって、半導体集積回路装置の内部にある内部回路と半導体集積回路装置の外部にある外部回路とを接続するために半導体集積回路装置の内部に設けられたパッドパターンにおいて、第1の配線層と、第1の配線層が形成されている層とは別の層に形成されている第2の配線層と、第1の配線層と第2の配線層を接続するビアと、を備え、第2の配線層にヒューズパターンが形成されており、ヒューズパターンを経由して内部回路と外部回路とを電気的に接続する。

(もっと読む)

鍵格納回路、半導体集積回路、及びシステム

【課題】格納された鍵の値の推測を困難にすることができる、鍵格納回路、半導体集積回路、及びシステムを提供する。

【解決手段】LSI10に搭載された鍵格納ブロック20は、k個のヒューズメモリセル30を有するヒューズブロック22と、鍵生成回路24と、を備えており、ヒューズブロック22からは予め実装されているビット長kの固定出力値fout[k−1:0]が出力される。鍵生成回路24は、レジスタ及び復号器を含んで構成されており、復号器は、演算処理により、固定出力値fout[k−1:0]と、レジスタの出力値と、からビット長n(n>k)の鍵key[n−1:0]を生成して出力する。

(もっと読む)

消費電力解析装置及び方法

【課題】 本発明の課題は、組み合せ回路を含めた電力解析を効率的かつ高速に行うことを目的とする。

【解決手段】 上記課題は、回路の動作記述の抽象度が異なる概要回路モデルと、該概要回路モデルより抽象度が低い詳細回路モデルとを含む回路データと、該回路の電力検証方法に係る動作シーケンス・データとを記憶する記憶部と、論理回路の動作シミュレーションを行う論理シミュレーション部に、前記前記概要回路モデルと前記詳細回路モデルとを含む前記回路データをロードし、該記憶部に記憶されている前記動作シーケンス・データに従って、該概要回路モデルによって前記動作シミュレーションを行わせる概要モードと、該詳細回路モデルによって該動作シミュレーションを行わせる詳細モードとを切り替えて、該論理シミュレーション部に該動作シミュレーションを行わせるシミュレーション制御部とを有することを特徴とする消費電力解析装置により達成される。

(もっと読む)

配線抵抗網作成装置および配線抵抗網作成方法

【課題】配線形状の複雑化に起因するエレクトロマイグレーション解析の処理時間の増加を抑制する。

【解決手段】配線パターン分割部(22)と、ビア部分抵抗網設定部(25)と、配線部分抵抗網設定部(24)と、配線抵抗・ビア抵抗接続部(28)を有する配線抵抗網作成装置(10)を構成する。配線パターン分割部(22)は、レイアウトデータからビアとの接続位置情報を含む配線パターンを取得し、配線パターンをアレイビア部分と配線部分に分割する。ビア部分抵抗網設定部(25)は、アレイビア部分に対応するビアノードおよびビア部分抵抗を含むビア部分抵抗網を設定する。配線部分抵抗網設定部(24)は、配線部分に対応する配線ノードおよび配線部分抵抗を含む配線部分抵抗網を設定する。配線抵抗・ビア抵抗接続部(28)は、ビア部分抵抗網と配線部分抵抗網を接続して配線抵抗網データを生成する。

(もっと読む)

回路設計検証装置および回路設計検証方法

【課題】回路シミュレーション用のネットリストに基づいて、当該回路のファンアウトを計算できるようにすること。

【解決手段】回路設計検証装置は、半導体素子レベルの回路シミュレーション用のネットリストを、論理を構成する複数の駆動回路に分割するネットリスト分割部と、前記複数の駆動回路のそれぞれに含まれるMOSトランジスタのゲート長およびゲート幅からゲートサイズを算出するゲートサイズ算出部と、前記複数の駆動回路のそれぞれによって駆動される後段の素子の負荷容量を算出する負荷容量算出部と、算出されたゲートサイズおよび算出された負荷容量に基づいて、前記複数の駆動回路のそれぞれに対するファンアウトを算出するファンアウト算出部と、を備えている。

(もっと読む)

プログラマブル・ゲートアレイ部を備えたマスクプログラマブル論理装置

【課題】プログラマブルゲートアレイ部を備えるマスクプログラマブル論理装置を提供すること。

【解決手段】集積回路の基板上に配置される複数のマスク−プログラマブル領域と、上記マスク−プログラマブル領域に結合されると共に上記マスク−プログラマブル領域を相互接続するために基板上に配置される複数の相互接続導体と、基板上に配置される複数のゲートアレイ部とからなり、ゲートアレイ部はマスクプログラマブル論理装置上の回路設計の実行を促進する少なくとも一つの機能を達成するようにプログラム可能である集積回路上に配置されるマスク−プログラマブル論理装置。

(もっと読む)

設計支援装置、設計支援プログラムおよび回路設計方法

【課題】クロックゲーティング回路を使用した、より効率的な低消費電力化を実現するための設計方法を提供する。

【解決手段】デジタル回路内のフリップフロップの出力がフリップフロップの入力側の組合せ回路に回帰している論理において、フリップフロップの出力がマルチプレクサに回帰ルートとして、またマルチプレクサに前段組合せ論理の出力が更新ルートとして接続されている論理に変換をするクロックゲーティング回路設計方法により解決できる。

(もっと読む)

半導体集積回路装置

【課題】回路ブロックの面積を増大しないで容量セルを構成すること。

【解決手段】一対の拡散領域15、14を有する基板構造層10と、一対の電源配線41、42を有する配線層40と、第1電極21、誘電体22、第2電極23が積層するとともに、基板構造層10と配線層40との間にて、スタンダードセルが配置されるスタンダードセル領域1の外枠に沿って枠状に形成される容量20と、スタンダードセル領域1外において一方の電源配線41と一方の拡散領域15とを電気的に接続する第1基板コンタクト31と、スタンダードセル領域1外において他方の電源配線42と他方の拡散領域14とを電気的に接続する第2基板コンタクト32と、スタンダードセル領域1内において第1電極21と他方の拡散領域14とを電気的に接続する第1容量コンタクト34と、スタンダードセル領域1内において第2電極23と一方の電源配線41とを電気的に接続する第2容量コンタクト33と、を備える。

(もっと読む)

半導体集積回路のレイアウト設計装置および半導体集積回路のレイアウト設計方法、制御プログラム、可読記録媒体、半導体集積回路

【課題】大規模特殊マクロセルのコーナー部近辺の配線を更に高密度に行い、チップサイズを更に縮小しかつチップコストをも低減する。

【解決手段】大規模特殊マクロセル2〜4とスタンダードセルを含む半導体集積回路において、大規模特殊マクロセル2〜4のコーナー部近辺(コーナー領域)の配線を、水平配線および垂直配線をコンタクトを設けることなく同一層で効率よく平行に配置した水平・垂直配線乗換え専用セル5を用いることにより、大規模マクロセル2〜4のコーナー部近辺の配線を更に高密度に行う。

(もっと読む)

半導体装置の作製方法

【課題】分周回路において消費電流を削減することを課題とする。特に、多段の分周回路において消費電流を削減すること課題とする。

【解決手段】多段の分周回路100では、初段ほど入力される信号の周波数が高く、後段ほど入力される信号の周波数は低くなる。よって、高い周波数の信号が入力される分周回路に対応する基本セル(D1)から優先的に配置し、配線接続を行う。つまり、高い周波数の信号が入力される配線を、より低い周波数の信号が入力される配線と比較して、配線長が短く、他の配線との交差が少なくなるように、即ち配線の寄生容量、寄生抵抗が小さくなるように、多段の分周回路に対応する複数の基本セルをレイアウトする。

(もっと読む)

スケーラブルアレイ構成方法及び装置

【課題】直列、並列、又はこれらの任意の組合せであるように再構成可能な、ロジックブロックのアレイを有するデバイスを提供する。

【解決手段】両端に配置された第1及び第2接続手段をそれぞれが有する一連の並列なロジックブロックチェーンを含むプログラマブルロジック回路のためのプログラミングインタフェースデバイスであって、各ロジックブロックチェーンの第1及び第2の接続手段とのインタフェースをそれぞれ行う第1及び第2のインタフェース手段と、複数の直列に接続されたロジックブロックを構成するようにそれぞれが配列された、少なくとも1つのプログラミング回路と、並列なロジックブロックチェーンが、並列、直列、又はこれらの任意の組合せであるように構成され得るように、各ロジックブロックチェーンの接続手段を、他のロジックブロックチェーンの接続手段に接続又は直接前記少なくとも1つのプログラミング回路に接続するプログラマブル接続手段とを備える。

(もっと読む)

配線パターン生成装置、配線パターン生成プログラム、および、半導体装置の製造方法

【課題】限られた大きさの配線領域であっても、当該配線領域の形状とパッド位置との関係を考慮することで、当該配線領域に対する配線パターンの自動生成を良好に行えるようにする。

【解決手段】配線パターンを自動生成に必要な情報を取得する情報取得手段4aと、前記情報取得手段4aが取得した各情報を基に、接続対応関係にあるパッド同士の位置関係によって、前記各パッドを複数のパッド群にグループ分けするグループ分け手段4bと、前記グループ分け手段4bがグループ分けした複数のパッド群についての処理優先順を決定する優先順決定手段4cと、前記優先順決定手段4cが決定した処理優先順に従いつつ、前記パッド群毎に個別に、当該パッド群で接続対応関係にあるパッド同士の間を導通させる配線のレイアウトパターンを決定する配線処理手段4dと、を備えて配線パターン生成装置を構成する。

(もっと読む)

配線パターン生成装置、配線パターン生成プログラム、および、半導体装置の製造方法

【課題】配線のレイアウトパターンを決定する際の処理モードを適宜選択し得るようにして、配線パターンの自動生成を良好に行えるようにする。

【解決手段】配線パターンを自動生成に必要な情報を取得する情報取得手段4aと、前記情報取得手段4aが取得した各情報に基づき、接続対応関係にあるパッド同士の間を導通させる配線のレイアウトパターンを決定するとともに、当該レイアウトパターンの決定を予め規定された互いに異なる複数の処理モードのいずれかに対応して行う配線処理手段4bと、前記配線処理手段4bが対応する処理モードを選択し、その選択結果を前記配線処理手段4bに指示するモード選択手段4cと、を備えて配線パターン生成装置を構成する。

(もっと読む)

半導体装置及びその制御方法

【課題】半導体装置の製造ばらつきや経年劣化に起因するクロックスキューを補正することができる半導体装置を提供する。

【解決手段】スキュー検出部6は、スキューを検出するための少なくとも1個のクリティカルパス7又はレーシングパス7を含む。クロック調整部5は、スキュー検出部6により検出されたスキューに基づいて、ディレイの設定値を設定する。クロックセル4は、ディレイの設定値に応じて、第1のクロックのディレイを調整して、第2のクロックとして出力する。

(もっと読む)

半導体集積回路の設計方法、設計プログラム、半導体集積回路の設計支援装置、及び半導体集積回路

【課題】本発明による半導体集積回路の設計方法、設計プログラムによれば、信頼性の高い累積故障確率の計算を行なうことができる。

【解決手段】本発明による半導体集積回路の設計方法は、半導体集積回路のレイアウト情報に基づいて、半導体集積回路全体のゲート面積を算出するステップと、経時絶縁破壊に対する累積故障確率を算出するステップと、累積故障確率を用いて半導体集積回路全体の累積故障確率を算出するステップとを具備する。

(もっと読む)

アンチヒューズリペア電圧制御回路

【課題】 アンチヒューズリペア時、高い電源電圧または低いバックバイアス電圧がセルや周辺回路またはコア領域のような回路部に影響を与えるのを防止する。

【解決手段】 アンチヒューズリペア電圧制御回路は、アンチヒューズのリペアに対応して、アンチヒューズリペアイネーブル信号を提供するアンチヒューズリペアイネーブル部と、前記アンチヒューズリペアイネーブル信号によって、電源電圧が第1回路部に伝達されることを制御する電源電圧制御部と、前記アンチヒューズリペアイネーブル信号によって、バックバイアス電圧が第2回路部に伝達されることを制御するバックバイアス電圧制御部とを具備する。

(もっと読む)

半導体装置

【課題】電源供給チップから本体チップへの電源供給制御を行う半導体装置において、本体チップのチップサイズに影響を与えることなく、電源供給配線の電位降下およびエレクトロマイグレーション問題の発生を抑止する手段を提供する。

【解決手段】本体チップ100が有するリング状の電源/GND配線と、本体チップへ電源供給を行う電源供給チップ106が有するリング状の電源/GND配線とが、複数の電極とバンプ103によって接続されてCOC構造をとった半導体装置。

(もっと読む)

半導体集積回路およびその設計方法

【課題】半導体集積回路置において、クロック回路の電源と、論理回路の電源とを分離しても、設計工数の増加や回路面積のオーバーヘッドを生じないようにする。

【解決手段】開示される半導体集積回路は、スタンダードセルの構造を有するクロック回路35と論理回路34とを第1の層上に同方向に形成された列上に配置し、クロック回路にクロック電源33を供給するクロック電源用電源38と論理回路に論理回路電源31を供給する論理回路電源用電源39とを第2の層上にクロック回路と論理回路の列と直交方向に形成された列上に配置してなるLSIに搭載された半導体集積回路であって、論理回路が論理回路電源の列とグランドGND32の列とにわたって置かれ、クロック回路がクロック電源とグランドGNDとにわたって置かれているとともに、クロック回路の電源にクロック電源が接続されている。

(もっと読む)

半導体集積回路の生産方法、設計方法及び設計システム

【課題】製造プロセスの成熟や変更に応じて、統計セルライブラリを速やかに更新すること。

【解決手段】半導体集積回路の設計方法は、(a)セルを構成する素子のモデルパラメータを作成するステップと、(b)モデルパラメータを用いた回路シミュレーションを行うことによって、モデルパラメータに対するセルの特性の応答を表す応答関数を作成するステップと、(c)応答関数を用いることによって、セルの特性の期待値及び統計的変動を示す統計セルライブラリを作成するステップと、を含む。ここで、モデルパラメータは、目標値と、その目標値からのばらつきの分布関数とで規定される。統計的変動は、上記分布関数と感度との積で表される。感度は、上記応答関数に基づいて算出される。設計方法は更に、(d)モデルパラメータが変更された場合、変更後のモデルパラメータと応答関数を用いることによって、回路シミュレーションを行うことなく統計セルライブラリを更新するステップを含む。

(もっと読む)

1 - 20 / 40

[ Back to top ]