Fターム[5F038DF16]の内容

半導体集積回路 (75,215) | 集積回路機能及び回路ブロック構成 (8,544) | 複数機能、回路ブロックの搭載、接続 (1,821) | 機能回路切換用構成 (929)

Fターム[5F038DF16]の下位に属するFターム

切換制御 (705)

Fターム[5F038DF16]に分類される特許

1 - 20 / 224

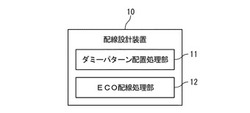

配線設計装置、配線設計方法、及びプログラム

【課題】半導体集積回路に対し、ダミーパターン配置後に、ダミーパターンを使用したECO(Engineering Change Order)配線設計を行う。

【解決手段】配線設計装置は、半導体集積回路にダミーパターンを配置し、ダミーパターンをECO配線に変更し、ダミーパターンの再配置及び電気的ショートを発生することなくECO配線を行う。これにより、ECO配線を行う時に、ダミーパターン再挿入や、既存配線とのショートを発生せずに、設計TAT(Turn Around Time)増を抑制することを可能とする。

(もっと読む)

半導体装置及びトリミング方法

【課題】ヒューズ素子の列数増に伴うトリミング時間の伸長を抑制する。

【解決手段】x方向に延伸する接地配線Gと、接地配線のy方向の一方側に設けられたヒューズ素子領域Aにx方向に沿って3列に並べて配置され、かつそれぞれの一端が接地配線Gに共通に接続される複数のヒューズ素子と、ヒューズ素子領域Aを挟んで接地配線Gの反対側に設けられ、ヒューズ素子領域Aに配置された複数のヒューズ素子それぞれの他端と接続される救済回路とを備え、上記複数のヒューズ素子は、それぞれ1つの欠陥選択線を示すアドレス情報を記憶する複数のヒューズ素子グループに所定個ずつグループ化され、同一のヒューズ素子グループに属する所定個のヒューズ素子は、同一列に配置されることを特徴とする

(もっと読む)

給電電圧の変動を吸収する電源構造を持つ集積回路

【課題】給電ユニット(エナジーハーベスティングデバイス)に改変を加えること無く、不安定な給電電圧、特に、低い給電電圧ででも正常に動作する、回路ユニットを含む集積回路を提供する。

【解決手段】本発明に係る集積回路は、外部電源に接続された第1の電源リングで囲まれた第1の回路ブロックと、第1の電源リングを介して前記外部電源に接続された第2の電源リングで囲まれた第2の回路ブロックとを含み、第1の回路ブロック内の半分以上が同期回路で構成され、第2の回路ブロック内の半分以上が非同期回路で構成されている。

(もっと読む)

半導体装置

【課題】電源線と機能回路の間に電源スイッチとして接続されるMOSトランジスタのオン時のバックゲートの電圧を簡単な構造で調整することができる半導体装置を提供する。

【解決手段】一対の電源線2、3と、機能回路4a0〜4anと、一対の電源線2、3との少なくとも一方と機能回路4a0〜4anの間に接続されるスイッチング回路6a0〜6an、7a0〜7anとを有し、スイッチング回路6a0〜6an、7a0〜7anは、ソース/ドレインの一方が機能回路4a0〜4anに接続され、他方が前記一対の電源線2、3の一方に接続される第1のMOSトランジス11と、第1のMOSトランジスタ11のゲートとバックゲートを接続する抵抗素子12、21と、第1のMOSトランジスタ11のゲートに接続されるゲート電圧制御回路13と、を有する。

(もっと読む)

半導体装置

【課題】積層チップシステムにおいて、各チップのIO回路の大きさを、そのドライブ能力やESD耐性能力を維持した上で、従来のサイズから縮小し、積層システムでは積層数に応じてIO数を変化させることができる半導体装置を提供する。

【解決手段】積層チップシステムにおいて、各チップは、各IO用の貫通ビア接続用パッド201に接続するIO回路202、スイッチ回路206にてIOチャネル207を構成し、このIOチャネル207を最大積層予定数のIOチャネル分まとめて接続してIOグループを構成し、このIOグループを1個以上持つ。各IO用の貫通ビア接続用パッド201は、貫通ビアにて別層のチップの同一位置のIO端子と接続される。インターポーザにおいては、実際の積層数が最大積層予定数に満たない場合はインターポーザ上で隣接するIOグループ内のIO用の接続用パッドが導体で接続されている。

(もっと読む)

鍵格納回路、半導体集積回路、及びシステム

【課題】格納された鍵の値の推測を困難にすることができる、鍵格納回路、半導体集積回路、及びシステムを提供する。

【解決手段】LSI10に搭載された鍵格納ブロック20は、k個のヒューズメモリセル30を有するヒューズブロック22と、鍵生成回路24と、を備えており、ヒューズブロック22からは予め実装されているビット長kの固定出力値fout[k−1:0]が出力される。鍵生成回路24は、レジスタ及び復号器を含んで構成されており、復号器は、演算処理により、固定出力値fout[k−1:0]と、レジスタの出力値と、からビット長n(n>k)の鍵key[n−1:0]を生成して出力する。

(もっと読む)

半導体集積回路装置の試験方法及び半導体集積回路装置

【課題】 半導体集積回路装置の試験方法及び半導体集積回路装置に関し、所定の回路動作を行った状態のまま半導体集積回路装置側の操作で所望の温度に制御する。

【解決手段】 スクリーニング試験前の工程にて測定された半導体集積回路装置の回路毎の電源電流値或いは電流ランクのいずれかにより、前記半導体集積回路装置全体毎または個別の回路動作毎に、適切な周波数に周波数設定し、所望の発熱量になるよう発熱量の制御を行い、スクリーニング試験時に、所定の回路動作を行った状態のまま所望の温度に制御する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の製造後におけるチャージ蓄積用素子からのチャージの放電を防止してデバイス機能素子のチャージダメージを低減する半導体装置及びその製造方法を提供する。

【解決手段】 半導体基板上に形成されたデバイス機能素子と、半導体基板上に形成されたチャージ蓄積用素子と、半導体基板上に形成され、デバイス機能素子とチャージ蓄積用素子との間に接続され、電気的に書き換え可能な不揮発性メモリトランジスタにより形成された分離用素子とを有する。

(もっと読む)

半導体装置

【課題】従来の入出力セルよりも回路面積の大きな入出力セルを面積効率良く配置する。

【解決手段】半導体装置において、複数の第1バッファセル31〜34は、基板の一辺に沿って1列に設けられる。複数の第2バッファセル21,22は、複数の第1バッファセルよりも基板の中央寄りの位置に、複数の第1バッファセルの配列方向に沿って1列に設けられる。複数の第1パッド81〜88は、複数の第1バッファセルの上部に上記配列方向に沿って1列に設けられる。複数の第2パッド61〜66は、複数の第1パッドよりも基板の中央寄りの位置に、上記配列方向に沿って1列に設けられる。複数の第2パッド61〜66は、各々が、複数の第1バッファセルのいずれか1つと個別に接続される複数の第3のパッド61,63,65,66と、各々が、複数の第2バッファセルのいずれか1つと個別に接続される複数の第4パッド62,64とを含む。

(もっと読む)

プログラマブルLSI

【課題】低消費電力で、動的コンフィギュレーションにも対応可能なプログラマブルLSIを提供する。

【解決手段】複数のロジックエレメントを有し、複数のロジックエレメントそれぞれは、コンフィギュレーションメモリを有する。複数のロジックエレメントそれぞれは、コンフィギュレーションメモリに記憶されたコンフィギュレーションデータに応じて、異なる演算処理を行い、且つ、ロジックエレメント間の電気的接続を変更する。コンフィギュレーションメモリは、揮発性の記憶回路と、不揮発性の記憶回路との組を有し、不揮発性の記憶回路は、チャネルが酸化物半導体層に形成されるトランジスタと、当該トランジスタがオフ状態となることによってフローティングとなるノードに一対の電極のうちの一方が電気的に接続された容量素子と、を有する。

(もっと読む)

半導体回路

【課題】レイアウトの複雑化や面積増大を伴わずにオフリーク電流の抑制と高速化を両立した半導体回路の実現。

【解決手段】通常動作モードと、少なくとも一部の回路に供給する信号を固定して、少なくとも一部の回路の状態を固定する低消費電力モードと、を備え、少なくとも一部の回路20において、低消費電力モード時にオン状態になるトランジスタPT1,PT3,NT2,NT4の閾値電圧が、低消費電力モード時にオフ状態になるトランジスタPT2,PT4,NT1,NT3の閾値電圧より小さい。

(もっと読む)

集積回路装置、電子機器及び集積回路装置の製造方法

【課題】 出力端子から出力される電圧値に応じて複数種の中から選択される耐圧に設定される集積回路装置等の提供すること。

【解決手段】 第1の耐圧を有する第1の出力トランジスター構造Tr_M1,Tr_M2と、第1の耐圧よりも高い第2の耐圧を有する第2の出力トランジスター構造Tr_H1,Tr_H2とが形成された半導体基板に、マスクを変えて配線して所定の耐圧に設定される集積回路装置である。配線により第1の耐圧が選択されると、第1,第2の出力トランジスター構造の双方が出力端子OUTと接続され、第2の出力トランジスター構造は、ダイオード接続されて静電気保護素子D1,D2を形成する。配線により第2の耐圧が選択されると、第1の出力トランジスター構造は出力端子OUTに非接続とされ、第2の出力トランジスター構造が出力端子OUTと接続される第2耐圧出力段トランジスターを形成する。

(もっと読む)

テストモード設定回路

【課題】端子数の少ないテストモード設定回路を提供する。

【解決手段】半導体装置のテストモードを制御するテスト端子に、低閾値電圧のディテクタと高閾値電圧のディテクタを設け、低閾値電圧のディテクタによって論理回路のリセットを解除し、高閾値電圧のディテクタでテストモードを切替え制御するような構成にした。従って、テスト端子とリセット端子とテストモード制御端子が共通になり、端子の数を大幅に削減することが可能である。

(もっと読む)

半導体チップおよびその設計方法

【課題】設計期間が短く、面積効率が高く、電源配線における電圧降下が小さな半導体チップと、その設計方法を提供する。

【解決手段】この半導体チップは、複数の電源ドメインD1〜D4に分割された内部回路2を備える。互いに異なる電流駆動能力を有する複数種類のレギュレータR1,R2を予め準備しておき、各電源領域毎に、当該電源領域の最大負荷電流を供給するために必要なレギュレータの種類と数を選択し、選択した1または2以上のレギュレータによって当該電源領域用の電源回路を構成する。したがって、設計期間が短くて済む。

(もっと読む)

半導体装置及びその駆動方法

【課題】現行プロセスを用いて追加工程なしに製造でき、高い信頼性を有する多値化された電気ヒューズを有する半導体装置を提供する。

【解決手段】第1フィラメントFS1と、第1フィラメントFS1に接続された第2フィラメントFS2とを有する電気ヒューズ素子を有し、第1フィラメントFS1の第2フィラメントFS2との接続端と反対の端部に接続された第1フィラメントFS1と第2フィラメントFS2の直列抵抗を読み出す直列読み出し部RDSとを有する構成とする。

(もっと読む)

半導体集積回路

【課題】遅延故障を適切に検出すること。

【解決手段】半導体集積回路は、当該半導体集積回路の被検査箇所への入力側の信号と出力側の信号とを入力とする排他論理和回路と、前記排他論理和回路の出力信号とクロック信号とを入力とする第一のマルチプレクサと、前記第一のマルチプレクサの出力信号に同期させて入力信号が示す値を記憶し、記憶している値を出力するフリップフロップとを含む検査用回路を有する。

(もっと読む)

半導体集積デバイスのテスト回路、テスト方法及びプログラム

【課題】複数のI/Oバッファ間における相対的な差を測定し、I/Oバッファの複数信号の相対的な差が許容範囲にあれば正常な半導体集積デバイスと判定し、いままでは不良のデバイスであると判定されていたものを救済する。

【解決手段】半導体集積デバイスにおいて、ドライバ、複数のレシーバ、インバータによって発振回路を構成し、この発振回路の出力をクロック入力とする2個以上のカウンタと、カウント値を比較するコンパレータの比較結果により半導体集積デバイスの良否を判定する。

(もっと読む)

集積回路および測定装置

【課題】集積回路自体の構成を変更することなく、回路動作を容易に変更することができる集積回路を提供する。

【解決手段】本発明の集積回路は、外部センサ200からの信号を処理する集積回路であって、互いに異なる入力端子部101,103に入力された信号を処理して互いに異なる出力端子部102,104に出力する複数の処理回路110,120を有し、前記集積回路に選択的に接続される外部センサ200の種類に応じて前記入力端子部と前記出力端子部との間の外部接続状況を変更することによって、前記複数の処理回路のうちで、前記外部センサからの信号を初めに受信する初段の処理回路と次段以降の処理回路との順番を切り替える。

(もっと読む)

半導体装置およびその制御方法

【課題】電源遮断・復帰時に動作中の回路の誤動作を抑止しつつ、デバイスの製造ばらつきに応じて最適な速度での電源制御領域の電源遮断・復帰を可能とする半導体装置の制御技術を提供する。

【解決手段】半導体装置において、通常動作領域10と、電源制御領域20と、電源制御領域20に接続され、電源制御領域20への電源を供給または遮断する複数の電源スイッチSWとを有し、さらに、複数の電源スイッチSWのオンオフを制御し、半導体装置毎の製造後の性能に応じて電源遮断・復帰の遷移時間を変更し、電源遮断・復帰を行うスイッチ制御回路30を有する。さらに、半導体装置毎の製造後の性能を記録する記憶素子40を有する。

(もっと読む)

システムインパッケージ

【課題】外付け機器用に別途端子を設けたりテスト端子を別途設けたりすることなく、マイクロコンピュータおよび周辺素子がパッケージに内蔵され互いに電気的に接続されたとしてもデバッグツールを外部接続することができ外部からデバッグできるようにする。

【解決手段】代替パルス発生制御部7eはデバッグするときにパルス発生素子3のパルス信号に代えて代替パルス信号を発生し、切替部8はパルス発生素子3のパルス信号と代替パルス発生制御部7eの代替パルス信号とを切替え、デバッグするときに代替パルス信号に切替えて出力し、各機能部4〜6が代替パルス信号に応じて動作し、外部接続されたデバッグツール9によってデバッグできる。

(もっと読む)

1 - 20 / 224

[ Back to top ]