Fターム[5F038DF17]の内容

半導体集積回路 (75,215) | 集積回路機能及び回路ブロック構成 (8,544) | 複数機能、回路ブロックの搭載、接続 (1,821) | 機能回路切換用構成 (929) | 切換制御 (705)

Fターム[5F038DF17]に分類される特許

1 - 20 / 705

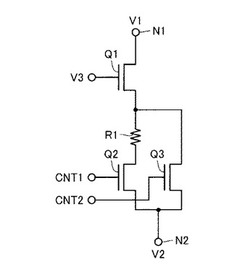

半導体装置と、それを用いたインバータ、コンバータおよび電力変換装置

【課題】性能のばらつきが小さな半導体装置を提供する。

【解決手段】この半導体装置は、ノードN1,N2間に直列接続された第1のスイッチング素子(高耐圧のトランジスタQ1)および第2のスイッチング素子(抵抗素子R1および低耐圧のトランジスタQ2)と、第2のスイッチング素子に並列接続された第3のスイッチング素子(低耐圧のトランジスタQ3)とを含む。トランジスタQ2をオンさせるとトランジスタQ1がオンし、さらにトランジスタQ3をオンさせるとノードN1,N2間が導通状態になる。したがって、オン抵抗値の高い第1のスイッチング素子をオンさせて高耐圧のトランジスタQ1をオンさせるので、ターンオン時間のばらつきが小さくなる。

(もっと読む)

半導体装置

【課題】異なる配線を介して異なる電源端子から内部回路を構成する第1の回路および第2の回路にそれぞれ給電する際に、第1の回路に給電する配線と第2の回路に給電する配線との間に発生するノイズを抑制する。

【解決手段】半導体装置は、第1の回路に給電を行う第1の電源配線と、第2の回路に給電を行う第2の電源配線と、第1の電源配線と第2の電源配線との間に容量素子を設けることにより、両端子間のインピーダンスを、大幅に低減させることにより異種電源間のノイズを低減する。

(もっと読む)

リレーデバイスを有するメモリ要素

【課題】メモリ要素有する集積回路を提供すること。

【解決手段】上記集積回路は、基板において形成された回路網と、回路網の上における複数の機械的リレーメモリ回路とを含む。集積回路は、回路網と複数の機械的リレーメモリ回路との間に配置された誘電スタックをさらに含む。誘電スタックは、複数の金属ルーティング層およびビア層を含む。回路網は、相補型金属酸化物半導体回路網を含む。回路網は、複数の機械的リレーメモリ回路に対する制御信号を生成するように動作可能である。

(もっと読む)

チャージポンプ回路およびそれを用いた半導体装置

【課題】起動時の消費電流を小さく抑制できるチャージポンプ回路を提供する。

【解決手段】このチャージポンプ回路30では、ポンプ回路10の起動期間は分周クロック信号CLKDをポンプ回路10に与えてポンプ回路10の電流供給能力を低く設定し、起動期間の終了後はクロック信号CLKをポンプ回路10に与えてポンプ回路10の電流供給能力を高く設定する。したがって、起動期間はポンプ回路10の消費電流を小さく抑制し、起動期間の終了後はポンプ回路10の電流供給能力を高めることができる。

(もっと読む)

半導体装置

【課題】回路構成の簡素化を図るとともに、遅延回路の遅延時間のばらつき等に起因して生じる問題点を解消し、コンパレータの動作を保証する2逓倍器を備えた半導体装置を提供する。

【解決手段】入力クロック信号CLKを可変遅延器16で遅延させた遅延クロック信号CLKDと、前記入力クロック信号の位相を位相比較器18で比較することで前記入力クロック信号CLKの周波数を2逓倍した2逓倍クロック信号CLKX2を生成する2逓倍器20と、前記2逓倍器20からの2逓倍クロック信号CLKX2が第1の論理レベルのとき入力信号の大小の比較動作を行い、前記2逓倍クロック信号CLKX2が第2の論理レベルのとき、比較動作を停止するコンパレータ10と、前記コンパレータ10の出力をモニタし、前記コンパレータ10が比較結果を出力したことを検出した時点でトリガ信号DLCLKを生成する第1の回路12、14を備える。

(もっと読む)

半導体装置

【課題】VIAホールを高密度に形成したとしても半導体素子が割れやすくなるのを防止し、素子の形成歩留りを向上させることができる半導体装置を提供する。

【解決手段】半導体装置は、基板110と、基板の第1表面に配置され、それぞれ複数のフィンガーを有するゲート電極124、ソース電極120およびドレイン電極122と、ソース電極120の下部に配置されたVIAホールSCと、基板の第1表面とは反対側の第2表面に配置され、VIAホールを介してソース電極に接続された接地電極とを備え、VIAホールSCは、基板110を形成する化合物半導体結晶のへき開方向とは異なる方向に沿って配置される。

(もっと読む)

半導体装置

【課題】スタンバイ状態時における第1導電型のトランジスタでの劣化を抑制可能な半導体装置を提供する。

【解決手段】半導体装置は、第1導電型のトランジスタを含み縦列接続された複数の回路と、複数の回路の其々の入力端子のうち他の回路と接続された接続入力端子と接続し接続入力端子の電圧を制御するための制御信号の活性化に応じて、接続入力端子に、該接続入力端子から電圧を受け付ける回路内の第1導電型のトランジスタを非導通状態とする第1の電圧を供給する制御回路と、を備える。

(もっと読む)

半導体装置、電子装置、車両、及び過熱検出方法

【課題】過熱検出回路の検出温度がばらつくことを抑制する。

【解決手段】コンパレータ170には、第1抵抗110と第1定電流源120の間の電圧Aと、ダイオード130と第2定電流源140の間の電圧Bが入力される。第1リーク電流源150は、ドレインが第1抵抗110と第1定電流源120の間に接続されており、ソース及びゲート電極が第1定電流源120と第2配線104の間に接続されている。第2リーク電流源160は、ドレインが第1配線102とダイオード130の間に接続されており、ソース及びゲート電極がダイオード130と第2定電流源140の間に接続されている。

(もっと読む)

半導体装置

【課題】直流電源配線に電流が流れたか否かを検出可能な回路を備えた半導体装置を提供する。

【解決手段】半導体装置において、駆動回路BLDU,BLDD,BLBDU,BLBDDは、電流磁界またはスピン注入によってトンネル磁気抵抗素子TMR,TMRBを第1の磁化状態に初期設定するために、制御信号線BL,BLBに直流電流を流す。電源配線DLは、トンネル磁気抵抗素子TMR,TMRBに近接して設けられる。ここで、トンネル磁気抵抗素子TMR,TMRBは、電源配線DLに直流電流が流れるときに生じる電流磁界によって第2の磁化状態に変化する。センスアンプ10は、トンネル磁気抵抗素子TMR,TMRBが第1の磁化状態から第2の磁化状態に変化したか否かを判定するために、制御信号線BL,BLBを介してトンネル磁気抵抗素子TMR,TMRBに流れる電流を検出する。

(もっと読む)

半導体装置および電源供給方法

【課題】消費電力を低減することが可能な半導体装置および電源供給方法を提供することである。

【解決手段】本発明にかかる半導体装置は、内部回路3に電源を供給する電源供給部4と、内部回路3の複数の場所における特性をモニタする複数のモニタ部1_1〜1_Nと、複数のモニタ部1_1〜1_Nから出力された信号C_1〜C_Nに基づき算出されたモニタ値C_AVEと、設定された比較値COMPとの比較結果に応じて電源供給部4を制御する制御部2と、を備える。制御部2は、複数のモニタ部1_1〜1_Nにおける特性のばらつきに応じて比較値COMPを設定する。

(もっと読む)

マルチICデバイスをテストするための方法および装置

【課題】マルチICデバイスをテストするための方法および装置を提供する。

【解決手段】集積回路は、入力信号を受け取るように構成される第1の入力相互接続と、テスト・イネーブル信号を受け取るように構成される第1のテスト・イネーブル相互接続と、前記入力信号に対応する値に基づいて該集積回路のテストを実行するためのコントローラと、入力ポートと、前記第1の入力相互接続、前記コントローラ、および前記入力ポートに結合され、前記テスト・イネーブル信号がアサートされていないことに応答して前記入力信号を前記入力ポートに渡し、前記テスト・イネーブル信号がアサートされていることに応答して前記入力信号を前記コントローラに渡すように制御可能である第1のマルチプレクサとを備える。

(もっと読む)

デュアルモードスイッチングレギュレータ

【課題】本発明は、デュアルモードスイッチングレギュレータに関する。

【解決手段】入力端からの入力電圧と予め設定された基準電圧とを比較して比較結果信号を出力する比較部と、上記比較結果信号に応じて予め連結されたレギュレート経路を制御するためのレギュレート選択信号及び予め連結されたバイパス経路を制御するためのバイパス選択信号を生成するスイッチング信号生成部と、上記レギュレート経路上に含まれ上記入力電圧を予め設定された電圧に変換するレギュレータと、上記レギュレート選択信号に応じて上記入力端と出力端との間のレギュレータを含むレギュレート経路をオン/オフスイッチングするレギュレート経路選択部と、上記バイパス選択信号に応じて上記レギュレータを経由せず上記入力端と出力端とを連結するバイパス経路をオン/オフスイッチングするバイパス経路選択部と、を含むことができる。

(もっと読む)

半導体テスト回路

【課題】スキャンチェーンを構成する回路でバーンイン試験を行う際に、シフトモードとキャプチャモードを切り替えるスキャンモードコントロール信号が接続された回路に対してもストレス印加を可能にする半導体テスト回路を提供する。

【解決手段】半導体テスト回路は、シフトモードとキャプチャモードを交互に切り替える内部スキャンモードコントロール信号と、スキャンチェーンのスキャンフリップフロップ回路に供給する内部クロック信号を生成するスキャンチェーン制御信号生成部を備える。スキャンチェーン制御信号生成部は、スキャンフリップフロップ回路の出力を遷移させる内部クロック信号のエッジのタイミングにおいて、内部スキャンモードコントロール信号がシフトモードになるように、内部スキャンモードコントロール信号と内部クロック信号の相互のタイミングを制御する。

(もっと読む)

半導体装置

【課題】寿命が長い半導体装置を提供する。

【解決手段】このLSIは、2つのCPU1,2と、CPU1,2のうちのいずれか1つのCPUを示す論理レベルのデータ信号が書き込まれた記憶回路4と、リセット信号REが非活性化レベルにされてLSIのリセットが解除された場合、記憶回路4の記憶データの論理レベルに対応するCPUのみに電源電圧を供給するとともに、記憶回路4の記憶データを現在の論理レベルと異なる論理レベルのデータ信号に書き換える制御回路3,5とを備える。したがって、故障の検知や、厳密なタイミング制御を必要とせずに、CPUの長寿命化を図ることができる。

(もっと読む)

再構成可能な集積回路ユニットを備えた論理回路及びその論路回路のエラー修正方法

【課題】エラー箇所の特定を実施する際に、システムを停止しないでエラー発生前の高信頼性までシステム性能を復帰させる。

【解決手段】同一動作を行う複数個の再構成可能な集積回路ユニットを備え、複数の該集積回路ユニットのそれぞれに複数のバンクを有する論理回路において、入力されたデータを、複数個の前記集積回路ユニットの各バンクに振り分けて入力する入力データ制御部と、複数個の集積回路ユニットの各バンクから出力されるデータを比較して、データ間の不一致を検出するエラー解析部と、エラー解析部から、データ間の不一致の通知を受けた場合に、複数個の集積回路ユニットの該当するバンクの再構成を行う構成情報制御部と、を備える。

(もっと読む)

半導体集積回路及びその電源制御方法

【課題】電源遮断状態からの復帰の際に、周辺回路の動作に影響を与えない半導体集積回路及び電源制御方法が、望まれる。

【解決手段】半導体集積回路は、第1及び第2の電源線と、サブ電源線と、第1の電源線とサブ電源線との間に配置される第1のスイッチ回路と、第2の電源線とサブ電源線との間に配置される論理回路と、第1の端子が第1の電源線と接続される容量素子と、容量素子の第1の端子の他方の第2の端子の接続を、第1の電源線、又は、サブ電源線、のいずれかに切り替える第2のスイッチ回路と、論理回路を非活性化状態から活性化状態に遷移させる場合に、第1のスイッチ回路により、第1の電源線及びサブ電源線の接続を遮断しつつ、第2のスイッチ回路により、第2の端子の接続を少なくても1回以上、サブ電源線に接続した後、第1の電源線に接続する制御回路と、を備えている。

(もっと読む)

プロセッサシステム及び半導体集積装置

【課題】処理速度の低下を最低限に抑えかつ従来技術に比較して消費電流の変動を抑える。

【解決手段】プロセッサシステム1は、プログラムメモリ2に格納された複数の命令コードを任意の順序で連続して実行する。テーブルメモリ53は、各命令コードと各命令コードの実行時の消費電流量との関係を示す消費電流量テーブルを格納する。電流変動抑制回路51は、消費電流量テーブルを参照して、連続する2つの命令コードの実行時の消費電流量の差の大きさが所定のしきい値以下になるように、上記連続する2つの命令コードのうちの一方の命令コードの実行時にプロセッサシステム1に流す補正消費電流を算出し、上記算出された補正消費電流量の補正消費電流をプロセッサシステム1に流すように、補正消費電流発生回路54を制御する。

(もっと読む)

半導体装置

【課題】出力信号を高速に変化させかつオーバーシュートやアンダーシュートを抑制できるようにする。

【解決手段】入力信号を反転して出力する主ドライバ11に加えて、補助ドライバ12を設け、入力信号の電圧変化に応じて出力信号が第1の電圧レベルから第2の電圧レベルへ変化するときに、変化開始から主ドライバの出力信号がある電圧レベルを超えるまでの期間では信号変化を補助するように制御部15により補助ドライバの動作を制御し、主ドライバの出力信号がある電圧レベルを超えてから第2の電圧レベルになるまでの期間に信号変化を抑制するように制御部により補助ドライバの動作を制御するようにして、出力信号における信号変化の高速性を向上させ、かつオーバーシュートやアンダーシュートを抑制できるようにする。

(もっと読む)

半導体装置

【課題】製造プロセスによる閾値電圧の変動に起因する歩留まりの悪化を抑制可能な半導体装置を提供する。

【解決手段】半導体装置は、複数のトランジスタが並列に接続された所定並列回路と、複数のトランジスタのオンオフ状態を制御しつつ所定並列回路のインピーダンスが所定値になったかを検出し、該インピーダンスが所定値になったときの複数のトランジスタのオンオフ状態に応じた制御値を生成する制御値生成部と、電源電圧を生成する電圧発生部と、電源電圧で動作する動作トランジスタと、制御値に基づいて電源電圧を制御する制御部と、を含む。

(もっと読む)

半導体集積回路装置

【課題】電源遮断領域の信号配線の自由度を低下させないで、電源遮断用スイッチから電源遮断領域に至る電圧伝達経路における電圧降下を抑える。

【解決手段】半導体集積回路装置(80)は、電源遮断用スイッチ(90)と電源遮断領域(763)とが形成された半導体チップ(22)とを含む。半導体チップは基板(21)に結合される。上記電源遮断領域の外側に上記電源遮断用スイッチを配置することで、電源遮断領域内の配線チャネル数の低減を回避する。そして上記基板には、上記半導体チップ内から上記電源遮断用スイッチを介して上記半導体チップの外に伝達された電源電圧を再び上記半導体チップ内に伝達して上記電源遮断領域へ給電するための基板側給電路(30)を形成することで、上記電源遮断用スイッチと上記電源遮断領域との間の電圧降下を抑える。

(もっと読む)

1 - 20 / 705

[ Back to top ]