Fターム[5F038AV08]の内容

半導体集積回路 (75,215) | 可変インピーダンス (2,334) | 可変素子(自身のインピーダンスを使用) (1,002) | MOSFET (453) | EPROM、EEPROM (55)

Fターム[5F038AV08]に分類される特許

1 - 20 / 55

半導体集積回路

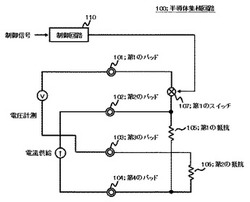

【課題】半導体集積回路に含まれる終端抵抗の抵抗値を4端子法によって測定をするためには、必要となる端子が増加し、半導体集積回路のチップサイズが増加するという問題がある。そのため、半導体集積回路のチップサイズ増加を抑制しつつ、終端抵抗の抵抗値を高精度で測定可能な半導体集積回路が、望まれる。

【解決手段】半導体集積回路は、第1乃至第4のパッドと、第2のパッドと第4のパッドの間に接続される第1の抵抗と、第3のパッドと第4のパッドの間に接続される第2の抵抗と、第1のパッドと第2のパッドの間に接続される第1のスイッチと、第1のパッド及び第3のパッドを4端子法における電圧測定端子として、第2のパッド及び第4のパッドを4端子法における電流供給端子として、それぞれ使用し第1の抵抗の抵抗値を測定するテストモードへの遷移指示を含む制御信号に基づき、第1のスイッチをオンする制御回路と、を備える。

(もっと読む)

鍵格納回路、半導体集積回路、及びシステム

【課題】格納された鍵の値の推測を困難にすることができる、鍵格納回路、半導体集積回路、及びシステムを提供する。

【解決手段】LSI10に搭載された鍵格納ブロック20は、k個のヒューズメモリセル30を有するヒューズブロック22と、鍵生成回路24と、を備えており、ヒューズブロック22からは予め実装されているビット長kの固定出力値fout[k−1:0]が出力される。鍵生成回路24は、レジスタ及び復号器を含んで構成されており、復号器は、演算処理により、固定出力値fout[k−1:0]と、レジスタの出力値と、からビット長n(n>k)の鍵key[n−1:0]を生成して出力する。

(もっと読む)

半導体装置

【課題】半導体装置に損傷を与えることなく、単体の抵抗素子自体の抵抗値を精度良く微調整する。

【解決手段】P型の半導体基板10上にN型の半導体層11が形成されている。半導体層11の表面には薄い第2の絶縁膜13が形成され、第1の絶縁膜12及び第2の絶縁膜13上にフローティングポリシリコン層14が形成されている。フローティングポリシリコン層14は第3の絶縁膜15に覆われている。第3の絶縁膜15によって覆われたフローティングポリシリコン層14上にはポリシリコン抵抗層16が形成されている。そして、半導体層11とポリシリコン抵抗層16との間に電圧を印加することにより、第2の絶縁膜13を通してフローティングポリシリコン層14の中に電子が注入され、ポリシリコン抵抗層16の中に正孔蓄積層16Aが形成される。

(もっと読む)

リーク電流モニタ、リーク電流モニタ方法、及び、半導体装置の製造方法

【課題】 リーク電流モニタ、リーク電流モニタ方法、及び、半導体装置の製造方法に関し、複数種類のデバイス特性をできるかぎり同じ構造のモニタで評価する。

【解決手段】 形状或いはしきい値電圧の少なくとも一方が異なる複数種類のトランジスタを異なった領域に同じ間隔で配置するとともに、前記複数種類のトランジスタの内、設計データにおける設置頻度の比を反映した数のトランジスタのゲート電極同士、ソース電極同士、及び、ドレイン電極同士を電気的に共通に接続する。

(もっと読む)

半導体集積回路および電子機器

【課題】不揮発性記憶素子にフューズ素子を用いた半導体集積回路において、目的とするデータと、検査データとしての目的とするデータの論理否定データとを記憶し、フューズ素子の不可逆性を利用することで、記憶回路と検証回路の回路規模をあまり大きくすることなく、またデータ検証の処理時間の増大を招くことなく、記憶データの信頼性と正真性を保証する。

【解決手段】記憶すべき情報を示す特定データを不可逆的に記憶する不揮発性記憶回路100aを有する半導体集積回路100において、該不揮発性記憶回路100aを、該特定データの非反転データを記憶する第1の記憶回路101と、該特定データの反転データを記憶する第2の記憶回路102とを有する構成とした。

(もっと読む)

半導体装置

【課題】高周波動作向けの半導体装置を高性能化させる。

【解決手段】シリコン基板S1上に形成された抵抗素子TDR1および不揮発性メモリNVM1を有する半導体装置であって、不揮発性メモリNVM1は、シリコン基板S1上に埋め込み酸化層BOX1を介して配置されたシリコン層SOI1に形成されている。特に、抵抗素子TDR1と不揮発性メモリNVM1とは互いに電気的に接続され、不揮発性メモリNVM1のオン状態またはオフ状態により、抵抗素子TDR1の導通状態または非導通状態が切り替わる。

(もっと読む)

半導体集積回路及び電子機器

【課題】システマテックばらつきとランダムばらつきの両方を考慮した適応型電圧スケーリング技術を実現することにある。

【解決手段】適応型電圧スケーリングを実施するシステム構成において、プロセスばらつきの種類毎に最適な検出回路を設置する。すなわち、システマテックばらつき検出用にゲートディレイの平均値に対する相対値を生成する第1測定回路(100)、及び、ランダムばらつき検出用にゲートディレイの標準偏差に対する相対値を生成する第2測定回路(200)を別々に設置する。夫々の測定回路で生成された相対値に基づいて電源電圧を決定するための制御情報(VCNT)を生成する。これを生成するときは例えばテーブルデータを参照する。

(もっと読む)

不揮発性記憶素子およびその製造方法、並びにその不揮発性記憶素子を用いた不揮発性半導体装置

【課題】高速動作が可能で、しかも可逆的に安定した書き換え特性を有し、半導体製造プロセスと親和性の高い不揮発性記憶素子およびその製造方法、並びにその不揮発性記憶素子を用いた不揮発性半導体装置の提供を目的とする。

【解決手段】第1電極103と、第2電極105と、第1電極103と第2電極104との間に介在させ、両電極103,105間に与えられる電気的信号に基づいて可逆的に抵抗値が変化する抵抗変化層104とを備えている。この抵抗変化層104は少なくともハフニウム酸化物を含み、当該ハフニウム酸化物をHfOxと表した場合に、0.9<x<1.6を満足するように抵抗変化層104が構成されている。

(もっと読む)

半導体装置およびそれを用いた情報処理装置

【課題】LSIに複数の電源を供給して回路ブロックごとに必要な電圧の電源を供給し、LSIの必要情報処理能力を維持したまま消費電力を最小化するとともに、電源の供給に必要な配線を極力低減し、2種類の電源を供給することによって発生する、LSIのチップ面積の増加や信号配線の性能低下を抑えることである

【解決手段】2種類の電源が供給されるLSIにおいて、高い電圧の電源の配線の密度を、低い電圧の電源の配線の密度よりも高くする。これにより、回路ブロックの性能にしたがって供給する電源を選択することによって、LSIで処理される情報量を高く保ったまま、不必要な電力を抑制し、消費電力を低減することが可能である。

(もっと読む)

半導体装置、半導体装置を搭載した電子機器、プログラム

【課題】実際の使用条件も勘案して、動作周波数と消費電力の両方の要求仕様を満足させる。

【解決手段】予め半導体装置の製造試験時の消費電力に関わる半導体特性情報を不揮発性の記憶部に格納しておく。複数の特性の異なる半導体装置について、動作雰囲気温度、動作周波数、アプリケーションごとに、消費電力を計測することにより周波数消費電力プロファイルテーブルを作成し、不揮発性の記憶部に格納しておく。半導体装置の動作温度を監視し(S110)、温度情報と現状に対応する周波数消費電力プロファイルテーブルを読み込み(S120−S130)、現状の消費電力を特定する(S140)。温度情報と周波数消費電力プロファイルテーブルに基づいて、定格電力範囲内で効果的な動作周波数となるように、半導体装置の動作周波数を制御する(S150)。

(もっと読む)

半導体集積回路装置

【課題】レギュレータが生成する電源電圧の電圧降下を大幅に低減し、効率よく高精度に、安定した電源電圧を供給する。

【解決手段】メモリ用電源部13は、複数のトランジスタ、および誤差増幅器からなる。トランジスタのソースパッドS、およびドレインパッドDは、それぞれ交互に一列となるように半導体チップの任意の一辺の周辺部に沿って配列されている。また、トランジスタのゲートは、それぞれ交互に配列されたソースパッドS、およびドレインパッドDと平行するように(ソースパッドS、およびドレインパッドDの配列方向とゲートの長辺方向とが平行となる)形成されている。これにより、ドレイン、ソースと接続される配線の配線距離を短くすることが可能となり、シート抵抗を削減することができる。

(もっと読む)

半導体装置及びその制御方法

【課題】ヒューズトリミングなどによってチップ毎に異なる設定をした後の半導体チップに対して設定値を変化させて行う動作マージン試験などのテストを容易に行えるようにする。

【解決手段】ヒューズ素子13を用いて複数ビットからなる設定値を固定する設定回路10と、設定回路10によって固定された設定値に応じて所定の電圧レベルを持つ内部電圧を供給する電源回路20と、UP、DOWN信号などの制御信号と固定された設定値S2〜S0とを入力し、制御信号に応じた所定の値だけその設定値を増加又は減少させた場合の出力を行うカウンタ回路30とを備えている。

(もっと読む)

集積回路装置、および電子機器

【課題】フィルタ回路のキャパシタ素子の容量値の適正な調整を可能にする。

【解決手段】抵抗素子の抵抗値とキャパシタ素子の容量値の積であるRC値を調整する集積回路装置100であって、少なくとも1つの抵抗素子Rfと少なくとも1つのキャパシタ素子Cfを有し、RC値によってフィルタ特性が定まるフィルタ回路150と、フィルタ回路の抵抗素子およびキャパシタ素子にそれぞれ対応する調整用抵抗素子Rおよび調整用キャパシタ素子Cを有し、調整用抵抗素子と調整用キャパシタ素子の接続ノードNrcの電圧である接続ノード電圧Vrcをモニターして、接続ノード電圧が所定電圧に達するまでの充電時間に対応する容量値設定データQcdを出力するRCキャリブレーション回路110と、を含み、フィルタ回路は、容量値設定データに基づいてキャパシタ素子の容量値を調整する。

(もっと読む)

トリミング装置及び圧電デバイス

【課題】量産時の歩留まりの悪化を防ぎ、しかも生産時の工数を大幅に削減することがで

きるトリミング装置を提供する。

【解決手段】n個のヒューズトリミング選択回路21と、入力されるシリアルのデータを

パラレルのデータに変換してn個のヒューズトリミング選択回路21にトリミング信号を

出力するシリアルパラレル変換回路と、を備えたトリミング装置2であって、ヒューズト

リミング選択回路21には、第1のヒューズ切断回路33と、第2のヒューズ切断回路3

6と、セレクタ回路50とが設けられている。第1のヒューズ切断回路33は、ヒューズ

31と切断回路であるNPNトランジスタ32とにより構成される。また第2のヒューズ

切断回路36は、ヒューズ34とNPNトランジスタ35とにより構成される。

(もっと読む)

電子回路装置及び電子回路装置の制御方法

【課題】本発明の目的は、回路と電源との接続を遮断した後に電源との接続を復帰させた場合に、急激な電源電圧低下を防ぐことにより回路を高速に起動するための電子回路装置を提供することである。

【解決手段】上記の課題を解決するため、電子回路装置は、電源と回路とを接続または遮断する第一スイッチと、該電源と容量素子とを接続または遮断し、オフ時の漏れ電流が該容量素子の漏れ電流よりも小さい第二スイッチと、該第一スイッチと前記第二スイッチとをオフした後に該第二スイッチをオンし第一時間経過後に該第一スイッチをオンするスイッチ制御部とを有することを特徴とする。

(もっと読む)

半導体集積回路装置

【課題】 チップのリセット期間(時間)を短縮することができる半導体集積回路装置を提供すること。

【解決手段】 データ線プリチャージ完了後にトリミング情報の読出し動作をする不揮発性メモリと、電源投入に応答して動作を開始して不揮発性メモリの制御回路をリセットするパワーオンリセット回路64とを有する半導体集積回路装置は、電源投入に応答して動作を開始し、データ線プリチャージ動作を行うパワーオンプリチャージ回路66を有する。パワーオンリセット回路64は、電源投入から第1の所定時間T1が経過した時点で電圧レベルの切換りを示すリセット解除信号を出力する第1のCR動作回路642を有する。パワーオンプリチャージ回路66は、電源投入から第2の所定時間T2が経過した時点で電圧レベルの切換りを示すプリチャージ完了信号を出力する第2のCR動作回路662を有する。

(もっと読む)

終端抵抗調整方法および終端抵抗調整回路

【課題】終端抵抗を調整するためのレプリカ抵抗の抵抗値を寄生抵抗に依らずに正確に外付けのリファレンス抵抗に合わせることができるようにする。

【解決手段】LSI100内に設けられた終端抵抗調整回路101内には、レプリカ抵抗Rrepの外に電圧測定回路11、12、判定回路13および調整コード発生回路14が設けられている。レプリカ抵抗Rrepの一端は電源端子VDDに接続され、他端は電圧測定回路11に接続されると共に外付けのリファレンス抵抗Rrefに接続されている。リファレンス抵抗Rrefの一端は電圧測定回路12に接続されている。電圧測定回路11と電圧測定回路12との測定結果は、判定回路13に入力されて比較され、その結果に基づいて形成された判定結果コードが調整コード発生回路14宛て出力される。調整コード発生回路14が出力する調整コードにより、レプリカ抵抗Rrepの調整が行なわれる。

(もっと読む)

半導体集積回路装置及びその製造方法

【課題】本発明が解決しようとする課題は、ナノメートル世代の半導体集積回路装置の製造上で生じるトランジスタの特性ばらつきによる動作不良や性能劣化を製造後に検出し、その部分、又は回路全体の動作を良品レベルに引き上げ、歩留り及び性能を向上させようとするものである。

【解決手段】製造後のトランジスタの特性を補正できる回路素子を付加したトランジスタを含む半導体集積回路装置及びトランジスタの特性を補正できる回路素子をトランジスタに付加し、トランジスタの製造後、トランジスタの特性を補正できるようにしたことを特徴とする半導体集積回路装置の製造方法。

(もっと読む)

集積回路の性能制御

【課題】集積回路の性能を制御する方法を提供する。

【解決手段】検査回路素子及び1つ以上の追加的な回路素子を備える集積回路が提供される。性能制御パラメータの様々な設定における検査回路素子の性能が決定される。その性能制御パラメータは、その場合に、1つ以上の追加的な回路素子の全体にわたって適用される。集積回路は、メモリバンクを備え得ると共に、性能制御パラメータは、一般的に、センス増幅器タイミング、ディレイライン長、または、動作電圧、動作クロック周波数、及び回路タイミング値のような他のパラメータであり得る。

(もっと読む)

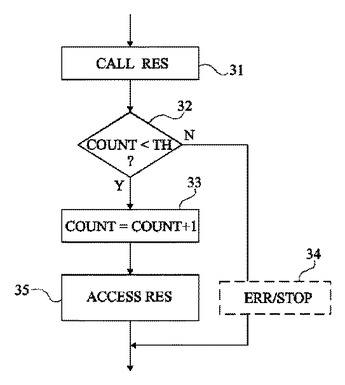

電子回路のリソースへのアクセス制限

【解決手段】本発明は、電子回路の少なくとも1つのリソースへのアクセスを制限するための方法及び回路に関し、リソースへのアクセスがカウンタ(COUNT) の少なくとも1ビットの値のテスト(32)の後に決定され、前記カウンタは、電子回路へ電力が供給されているか否かに無関係に、一定時間の終了の際に自動的に再起動される。  (もっと読む)

(もっと読む)

1 - 20 / 55

[ Back to top ]