Fターム[5F064FF07]の内容

ICの設計・製造(配線設計等) (42,086) | 切り換え、選択 (3,709) | 切り換え、選択目的 (1,053) | 特性、機能の切り換え (623) | 電流、電力の切り換え (60)

Fターム[5F064FF07]に分類される特許

1 - 20 / 60

半導体集積回路

【課題】設計する回路の中で電流の多く流れる信号線を容易に見つけ出すことができ、容

易にその部分の電流を測定できるスタンダードセルを提供することを課題とする。

【解決手段】電流検出用テストパッドを少なくとも2つ有するスタンダードセルを自動レ

イアウトで配置する。そして、2つのテストパッド間を接続する配線を切断することで、

該2つのテストパッドを電流測定用テストパッドとして利用する。なお、スタンダードセ

ル内の2つのテストパッド間は、過電流が流れることにより電流の流れる経路が遮断され

る配線によって接続される構成としてもよい。また、2つのテストパッド間をつなぐ配線

部にメモリ又はアナログスイッチを設ける構成としてもよい。

(もっと読む)

鍵格納回路、半導体集積回路、及びシステム

【課題】格納された鍵の値の推測を困難にすることができる、鍵格納回路、半導体集積回路、及びシステムを提供する。

【解決手段】LSI10に搭載された鍵格納ブロック20は、k個のヒューズメモリセル30を有するヒューズブロック22と、鍵生成回路24と、を備えており、ヒューズブロック22からは予め実装されているビット長kの固定出力値fout[k−1:0]が出力される。鍵生成回路24は、レジスタ及び復号器を含んで構成されており、復号器は、演算処理により、固定出力値fout[k−1:0]と、レジスタの出力値と、からビット長n(n>k)の鍵key[n−1:0]を生成して出力する。

(もっと読む)

半導体集積回路

【課題】SOI型の半導体集積回路において電源遮断時の低消費電力及び電源供給時の動作性能向上に資することができる電源遮断制御を可能にする。

【解決手段】本発明に係る半導体集積回路は、第1電源スイッチと、前記第1電源スイッチに直列接続される論理回路を有する。前記論理回路は、順序回路(FF1,FF2)及び組み合わせ回路(LOG1,LOG2)を含み、前記第1電源スイッチと前記組み合わせ回路との間に第2電源スイッチが接続される。第1モードにおいて前記第1電源スイッチをオフ状態に制御し、前記順序回路及び前記組み合わせ回路を非通電状態にし、第2モードにおいて前記第1電源スイッチをオン状態に維持し且つ前記第2電源スイッチをオフ状態に制御し、前記順序回路を通電状態、前記組み合わせ回路を非通電状態にする電源スイッチ制御回路を有する。

(もっと読む)

半導体装置およびその動作方法

【課題】省面積化を図ることが可能な半導体装置およびその動作方法を提供する。

【解決手段】各記憶素子21は、P型の半導体層211Pと、半導体層211P内で互いに分離するように配設されたN型の半導体層212N,213Nと、半導体層212Nと電気的に接続された電極215Aと、半導体層213Nと電気的に接続された電極215Bとを有する。駆動対象の記憶素子21に対して、電極215Aと電極215Bとの間に所定の閾値以上の電圧V1を印加して、半導体層212Nと半導体層213Nとの間の領域にそれらの半導体層同士を電気的に繋ぐ導電パスであるフィラメント210を形成することにより、情報の書き込み動作を行う。

(もっと読む)

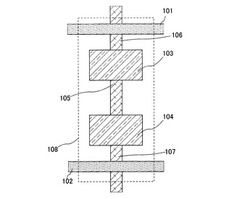

半導体装置

【課題】電源遮断がされる領域同士の場合であっても生じる、電源遮断移行時および復帰時の貫通電流の問題を解決しつつアイソレーション回路を不要とする半導体装置を提供する。

【解決手段】半導体装置は、第1の電源線601と、第1のスイッチ605を介して第1の電源線に接続される第2の電源線101、および第2の電源線に接続されるマクロセルコア508を有するマクロセルと、第2のスイッチ603を介して第1の電源線に接続される第3の電源線602と、第3の電源線に接続され、マクロセルコアの入力または出力の少なくともいずれかに接続される回路ブロック501とを備え、第2の電源線と第3の電源線とが接続される。

(もっと読む)

半導体装置

【課題】低消費電力かつ低占有面積で、パッケージ実装後においてもプログラムを行なうことができるヒューズ素子を備えるヒューズプログラム回路を実現する。

【解決手段】ヒューズプログラム回路(FPK1−FPKn)において、ヒューズ素子FSを、多層メタル配線の第3層以上のメタル配線(M(i))を用いて実現する。各ヒューズプログラム回路において、スキャンフリップフロップ(FSSRおよびPSR)を用いてプログラム情報およびヒューズ選択情報を順次転送して、選択的に、1本ずつヒューズを電気的に切断する。

(もっと読む)

ノイズ解析装置及びノイズ解析方法

【課題】半導体集積回路の設計初期において、電源制御回路により内部回路の電源の接続及び切断を行った際に発生する電源ノイズの解析を短時間で精度良く行えるようにする。

【解決手段】電源ノイズ解析に係る基本単位回路の解析モデルを作成し、それを半導体集積回路の内部回路の解析モデルとして組み込み、半導体集積回路のレイアウトの前段階で、内部回路への電源供給を制御する複数のスイッチ群を有する電源制御回路を用いた半導体集積回路にて内部回路の電源の接続及び切断を行った際に発生する電源ノイズを算出する。

(もっと読む)

プログラマブル論理回路装置及び画像処理装置

【課題】 節電効率を向上させることができるプログラマブル論理回路装置及び画像処理装置を提供する。

【解決手段】 本発明のプログラマブル論理回路装置100は、素子間の接続の変更により再構成される回路を備える複数の再構成領域R0−R5と、複数の再構成領域R0−R5の各々に対して、実行させる処理を割り当てて、複数の再構成領域R0−R5の各々が実行する処理の状態に基づいて、複数の再構成領域R0−R5を選択的に再構成して節電状態にする管理領域R0及びR5と、管理領域R0及びR5が複数の再構成領域R0−R5を選択的に再構成するタイミングを調整する同期管理部22及び42と、を備える複数のプログラマブル論理回路部50及び60を有し、同期管理部22は、他の同期管理部42と同期して、タイミングを調整する。

(もっと読む)

解析装置及び半導体装置

【課題】 本発明の課題は、複数段の電源スイッチを段階的にオンすることによって内部回路に電源供給する半導体装置において、電源供給開始から起動可能となるまでの復帰時間を短縮することを目的とする。

【解決手段】 上記課題は、複数段の電源スイッチを段階的にオンすることによって内部回路に電源供給する電源供給回路を解析する解析装置であって、前段までの電源スイッチをオン状態とし、オンすることによって発生する許容ノイズ量を超えない最大電源ノイズ量となる電源スイッチサイズを次段の電源スイッチとして決定する電源スイッチサイズ決定手段と、前記次段の電源スイッチサイズによる電源ノイズが前記オンされてから収束判定量以下となるまでの時間をオン時間間隔として決定するオン時間間隔決定手段とにより達成される。

(もっと読む)

プログラマブル論理回路装置及び画像処理装置

【課題】 節電効率を向上させることができるプログラマブル論理回路装置及び画像処理装置を提供する。

【解決手段】 本発明のプログラマブル論理回路装置100は、素子間の接続の変更により再構成される回路を備える複数の再構成領域R0、R1、R2、R3及びR4と、複数の再構成領域R1、R2、R3及びR4の各々に対して、実行させる処理を割り当てて、複数の再構成領域R1、R2、R3及びR4の各々が実行する処理の状態に基づいて、複数の再構成領域R1、R2、R3及びR4を選択的に再構成して節電状態にする管理領域である再構成領域R0と、を有する。

(もっと読む)

半導体集積回路及び半導体集積回路の電源スイッチ制御方法

【課題】電源スイッチを非導通状態から導通状態に遷移させる時間を最適化できる半導体集積回路及びその電源スイッチ制御方法を提供する。

【解決手段】共通電源配線と、第1の回路と、それぞれ電源スイッチ制御信号に基づいて導通、非導通が制御され共通電源配線と第1の回路との間を並列に接続する複数の電源スイッチと、電源スイッチ制御信号と複数の電源スイッチとの間に接続され電源スイッチ制御信号が非導通状態から導通状態に遷移するときに電源スイッチ制御信号の遷移をそれぞれ異なった遅延時間だけ遅延させて複数の電源スイッチに伝え複数の電源スイッチをそれぞれ時間をずらして非導通状態から導通状態に遷移させる遅延回路と、各遅延回路の遅延時間の増減を制御する遅延時間制御部と、を備える。

(もっと読む)

ザッピング素子及び半導体集積回路

【課題】ザッピング素子の破壊電圧を低電圧化すると共に、その製造コストを低減する。

【解決手段】ザッピング素子100のゲート電極14の幅は部分的に狭くなるように加工されている。即ち、ゲート電極14は、その中央部に、小さい第1のゲート幅W1を持った第1のゲート電極部分14Nと、その両側に、大きい第2のゲート幅W2を持った第2のゲート電極部分14Wを有して構成されている。したがって、第1のゲート電極部分14Nに対応したチャネル領域CHの第1のチャネル長LC1は、第2のゲート電極部分14Wに対応したチャネル領域CHの第2のチャネル長LC2より短くなっている。

(もっと読む)

論理回路設計方法及びプログラム

【課題】論理回路における信号伝播に応じて、回路データを修正し消費電力を削減する。

【解決手段】設計対象の論理回路の回路データ及びシミュレーション結果に基づいて、複数の出力先のフリップフロップの中から出力元のフリップフロップの出力変化が伝播されないときがあるフリップフロップを検出し、出力元のフリップフロップを複製して検出された出力先のフリップフロップに出力を供給しかつ出力変化が伝播されないときには複製したフリップフロップの出力を停止する変更後の論理回路の消費電力と変更前の論理回路の消費電力とを評価し、変更後の論理回路の消費電力が変更前のそれより低い場合には、出力元のフリップフロップを複製して検出された出力先のフリップフロップへの出力の供給経路を分離させる回路データの修正情報を生成する。

(もっと読む)

半導体集積回路のレイアウト装置及びクロックゲーティング方法

【課題】スイッチング時におけるセルによる消費電力を削減することができる半導体集積回路のレイアウト装置及びクロックゲーティング方法を提供すること。

【解決手段】本発明にかかるレイアウト装置51は、イネーブル信号生成処理部55と、クロックゲーティング回路追加処理部56とを備えている。イネーブル信号生成処理部55は、第1の分岐点よりも後段に位置する第1のクロックゲーティング回路に入力される第1の制御信号と、第1の分岐点よりも後段に位置する同期回路の位置とに基づいて、第2のクロックゲーティング回路に入力する第2の制御信号を生成する。クロックゲーティング回路追加処理部56は、第2の制御信号と、第2のクロックゲーティング回路よりも後段に位置する回路素子数と、に基づいて、第2のクロックゲーティング回路を配置する。

(もっと読む)

半導体装置

【課題】ヒューズの線幅の縮小化を図ることが可能な半導体装置を提供する。

【解決手段】この半導体装置1では、ヒューズFUに隣接してダミーヒューズDFUを設け、ヒューズFUおよびダミーヒューズDFUの各々の配線幅を最小線幅に設定し、ヒューズFUおよびダミーヒューズDFUの間隔を最小間隔に設定した。したがって、OPCによってヒューズFUおよびダミーヒューズDFUの露光条件が最適化されるので、最小線幅のヒューズFUを形成することができる。

(もっと読む)

論理回路設計支援方法及び装置

【課題】 実動作において低消費電力化が図れるゲーティッドクロック設計が可能な論理回路設計支援方法を提供する。

【解決手段】 最適化対象論理回路の回路構造を記述した回路データD1に基づいて、最適化対象論理回路に入力する複数のイネーブル信号の情報D2を抽出する第1ステップS1と、最適化対象論理回路と抽出された複数のイネーブル信号の生成論理に対して実動作モードの論理シミュレーションを実行して、イネーブル信号毎の動作時におけるアクティブ状態と非アクティブ状態間の状態遷移に係る時系列情報D4を取得する第2ステップS2と、時系列情報D4に基づいて、最適化対象論理回路とクロックゲーティング回路の合計消費電力が、クロックゲーティング回路を挿入する前の最適化対象論理回路の消費電力より低減されるように、クロックゲーティング回路の挿入個数及び挿入箇所を最適化する第3ステップS3〜S5を有する。

(もっと読む)

半導体集積回路およびパワーゲーティング制御方法

【課題】搭載される機能ブロックの個数によらず、一定数の少数の配線のみでパワーゲーティング制御を行うことのできる半導体集積回路およびパワーゲーティング制御方法を提供する。

【解決手段】パワーゲーティング制御情報生成部1が、機能ブロックBLK1〜BLK3に対するパワーゲーティング制御情報PGCを生成し、クロック信号制御部2が、クロック信号CK0にパワーゲーティング制御情報PGCを重畳し、機能ブロックBLK1〜BLK3へ供給するクロックとなるクロック信号CKを生成し、機能ブロックBLK1〜BLK3のそれぞれと一体に1個ずつ配置されたパワーゲーティング制御部31〜33が、クロック信号CKに重畳されたパワーゲーティング制御情報PGCを解読して、機能ブロックBLK1〜BLK3に対するパワーゲーティング制御信号PG1〜PG3をそれぞれ生成する。

(もっと読む)

半導体装置

【課題】半導体装置のレイアウトの自由度を向上させる。

【解決手段】本発明による半導体装置は、第1行おいて、行方向に連続的に配置される第1電源供給セル20及び複数の第1セル10と、第1行に隣接する第2行において、行方向に連続的に配置され、前記第1行に隣接する複数の第2セル10とを具備する。第1電源供給セル20は、行方向に直交する第1電源配線62に接続され、第1電源配線62から供給される電圧に応じた電源電圧を、複数の第1セル10及び複数の第2セル10に供給する。第2行において、第1行に配置された第1電源供給セル20に隣接する第2セルと第1電源配線62とは、直接接続されず第1行に配置された第1電源供給セル20を介して接続される。

(もっと読む)

半導体集積回路設計支援システム及び半導体集積回路

【課題】ソフトウェアによる部分的電源制御を行う半導体集積回路において、検証不足による不具合の発生を抑止することが出来るための半導体集積回路設計支援システム及び半導体集積回路を提供する。

【解決手段】部分的電源制御機構を有する半導体集積回路の設計支援システム1は、半導体集積回路21の回路記述41と電源仕様記述43に基づいて部分的電源制御シミュレーションを実行する部分的電源制御シミュレーションプログラム(PCS)と、部分的電源制御シミュレーション実行中に実行されたパワーモードを検出して、検査済みパワーモードのパワーモード情報を記録するパワーモード遷移検出プログラム(PTDP)と、部分的電源制御実行時に記録された検査済みパワーモードが使われているか否かを確認し、確認結果を出力するパワーモード遷移確認プログラム(PTCP)とを有する。

(もっと読む)

半導体集積回路装置

【課題】低電力制御が行われるエリアバンプ構造の半導体集積回路装置に最適化した電源供給を提供する。

【解決手段】論理ブロック領域2において、電源スイッチ部14は、論理ブロック領域2,3の両辺側にそれぞれレイアウトするのではなく、論理ブロック領域2の内側に分割して等間隔でレイアウトし、各々の基準電位VSS用のパッド11との距離が短くなるようにする。たとえば、論理ブロック領域2では、電源スイッチ部14が3つに分散されて配置されており、各々のパッド11と電源スイッチ部14との距離が短くなるようにしている。これにより、エリアバンプ構造の半導体集積回路装置における電源供給の電圧低下を大幅に低減することができる。

(もっと読む)

1 - 20 / 60

[ Back to top ]