Fターム[5F038AV13]の内容

半導体集積回路 (75,215) | 可変インピーダンス (2,334) | 可変回路(他素子のインピーダンスを使用) (1,117) | スイッチ素子による切換 (1,056)

Fターム[5F038AV13]の下位に属するFターム

Fターム[5F038AV13]に分類される特許

1 - 20 / 271

半導体集積回路

半導体装置

半導体集積回路

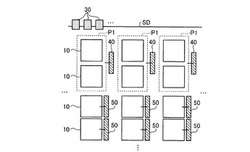

【課題】回路規模を低減しつつ任意の論理を実現可能な半導体集積回路を提供する。

【解決手段】実施形態の半導体集積回路は、第1論理ブロックを少なくとも1つ含む第1回路群と、第1論理ブロックよりも多い数の第2論理ブロックを含む第2回路群と、入力データを第1論理ブロックまたは第2論理ブロックへ入力する機能、および、第1論理ブロックまたは第2論理ブロックから出力される出力データを外部へ出力する機能を有する入出力部とを含む。第1回路群は、第1スイッチブロックと、第1電源制御回路とを有する。第1電源制御回路は、第1回路群に含まれる第1論理ブロックおよび第1スイッチブロックに対する電力の供給および停止を共通に制御する。第2回路群は、第2スイッチブロックと第2電源制御回路とを有する。第2電源制御回路は、第2回路群に含まれる論理ブロックおよび第2スイッチブロックに対する電力の供給および停止を共通に制御する。

(もっと読む)

トリミング回路及び調整回路

【課題】ヒューズ素子の仮想切断を可能にすると共に、高電圧又は大電流によるヒューズ溶断の際に、周辺回路を破損する確率も低減できる信頼性の高いトリミング回路を提供する。

【解決手段】ヒューズトリミングを行うための回路であって、トリミングヒューズと、

前記トリミングヒューズに接続されるトリミング用のパッド端子と、仮想切断時に制御信号を入力するテスト端子と、入力端子の一方が前記テスト端子に接続され他方が前記トリミングヒューズに接続され、入力された制御信号に応じた制御信号を出力する制御回路と、を有し、前記トリミングヒューズの切断により、前記制御回路の他方の入力端子がGNDレベルへプルダウンする手段を備えたことを特徴とする。

(もっと読む)

半導体集積回路

【課題】本発明の目的は,論理回路に電源電圧を供給するレギュレータを有する半導体集積回路において,C端子の数を削減する。

【解決手段】

半導体集積回路30は,第1,第2の出力端OTa,OTbと,外部容量C4に接続する外部接続端子CT4との間に設けられたスイッチ回路35を有し,

スイッチ回路35の一端は第1の出力端OTaに接続され,スイッチ回路35の他端は外部接続端子CT4および第2の出力端OTbに接続され,

スイッチ回路35は,第1のレギュレータA31が第1の電源電圧Vaを第1の論理回路A32に対して供給する期間はオンし,第1のレギュレータA31が第1の論理回路A32に対する電源電圧供給を停止する期間はオフする。

(もっと読む)

半導体集積回路

【課題】半導体集積回路に含まれる終端抵抗の抵抗値を4端子法によって測定をするためには、必要となる端子が増加し、半導体集積回路のチップサイズが増加するという問題がある。そのため、半導体集積回路のチップサイズ増加を抑制しつつ、終端抵抗の抵抗値を高精度で測定可能な半導体集積回路が、望まれる。

【解決手段】半導体集積回路は、第1乃至第4のパッドと、第2のパッドと第4のパッドの間に接続される第1の抵抗と、第3のパッドと第4のパッドの間に接続される第2の抵抗と、第1のパッドと第2のパッドの間に接続される第1のスイッチと、第1のパッド及び第3のパッドを4端子法における電圧測定端子として、第2のパッド及び第4のパッドを4端子法における電流供給端子として、それぞれ使用し第1の抵抗の抵抗値を測定するテストモードへの遷移指示を含む制御信号に基づき、第1のスイッチをオンする制御回路と、を備える。

(もっと読む)

半導体装置

【課題】発振周波数変動の許容範囲を任意に設定可能にする。

【解決手段】半導体装置(21)は、トリミングレジスタ(11)に保持されたトリミング値によって発振周波数が変更される発振器(12)と、発振周波数を補正可能な補正回路(20)とを含む。上記補正回路は、上限値を設定可能な上限値レジスタ(6)と、下限値を設定可能な下限値レジスタ(7)と、発振周波数を分周するための分周回路(13)と、分周回路の出力をカウントするカウンタ(3)とを含む。さらに上記補正回路は、カウンタの出力を保持可能なバッファレジスタ(4)と、バッファレジスタの保持値が、上限値と下限値との間に入っているか否かを判別する比較器(5)と、その判別結果に基づいてトリミング値を補正するトリミング値補正制御回路(8)とを含む。ユーザは、上限値と下限値とによって、発振周波数変動の許容範囲を任意に設定することができる。

(もっと読む)

半導体装置

【課題】半導体素子が有する寄生容量や寄生インダクタンスによる電力の損失を抑えるこ

とが出来る、整流回路の提供を課題とする。

【解決手段】入力された交流電圧の振幅に従い、前段の回路と該整流回路の間におけるイ

ンピーダンスを整合または不整合にする。入力される交流電圧が規定の振幅以下である場

合は、インピーダンスを整合にし、該交流電圧をそのまま整流回路に印加する。逆に入力

される交流電圧が規定の振幅よりも大きい場合は、インピーダンスを不整合にし、反射に

より該交流電圧の振幅を小さくしてから整流回路に印加する。

(もっと読む)

半導体集積回路

【課題】不具合の発生が抑制された半導体集積回路を提供する。

【解決手段】電圧レベルの高いHi信号、及び、該Hi信号よりも電圧レベルの低いLo信号が異なるタイミングで入力される第1入力端子と、Hi信号が常時入力される第2入力端子と、第1入力端子のHi信号によって第1動作状態、第1入力端子のLo信号によって第2動作状態に制御される素子と、を有する半導体集積回路であって、第2入力端子とグランドとの間にスイッチング素子が設けられており、該スイッチング素子は、第1入力端子にHi信号が入力されている時にOFF状態、第1入力端子にLo信号が入力されている時にON状態となる。

(もっと読む)

集積回路

【課題】電力消費量の増大を抑制しつつ、タイミング信号のスキューを低減する。

【解決手段】第1のクロック分配回路は、タイミング信号を複数の第1の分配点に分配する。第2のクロック分配回路は、タイミング信号を複数の第2の分配点に分配する。最小遅延クロック信号出力部は、複数の第1の分配点のいずれかに分配されたタイミング信号と複数の第2の分配点のいずれかに分配されたタイミング信号とのうち遅延が小さい方の信号を最小遅延タイミング信号として出力する。同期動作回路は、最小遅延タイミング信号に同期して動作する。

(もっと読む)

半導体装置

【課題】従来の半導体装置では、エンファシスの有無により消費電流が変動する問題があった。

【解決手段】本発明の半導体装置は、抵抗値を、エンファシスモードにおいて第1の抵抗値とし、非エンファシスモードにおいて第1の抵抗値よりも小さな第2の抵抗値とする可変抵抗30と、出力インピーダンスを、エンファシスモードにおいて第3の抵抗値とし、非エンファシスモードにおいて前記第3の抵抗値よりも大きな第4の抵抗値とする第1の駆動部10と、出力インピーダンスを、エンファシスモードにおいて第5の抵抗値とし、非エンファシスモードにおいて第5の抵抗値よりも大きな第6の抵抗値とする第2の駆動部11と、入力信号に応じて第1、第2の駆動部の導通状態を制御すると共に、エンファシスモードと非エンファシスモードとにおいて第1、第2の駆動部の出力インピーダンスと可変抵抗の抵抗値を切り換える制御部と、を有する。

(もっと読む)

半導体装置

【課題】製造プロセスによる閾値電圧の変動に起因する歩留まりの悪化を抑制可能な半導体装置を提供する。

【解決手段】半導体装置は、複数のトランジスタが並列に接続された所定並列回路と、複数のトランジスタのオンオフ状態を制御しつつ所定並列回路のインピーダンスが所定値になったかを検出し、該インピーダンスが所定値になったときの複数のトランジスタのオンオフ状態に応じた制御値を生成する制御値生成部と、電源電圧を生成する電圧発生部と、電源電圧で動作する動作トランジスタと、制御値に基づいて電源電圧を制御する制御部と、を含む。

(もっと読む)

半導体装置

【課題】インダクタンス値を広範囲に可変可能なインダクタを備える半導体装置を提供する。

【解決手段】半導体装置は、多層配線層と、多層配線層を用いて形成され、巻軸が、多層配線層に対して平行である複数のソレノイド型インダクタと、少なくても1以上のソレノイド型インダクタと接続され、ソレノイド型インダクタの状態を活性化、又は、非活性化する制御回路と、を含んで構成される可変インダクタを備えている。

(もっと読む)

半導体装置

【課題】プログラマブルなアナログデバイスを提供する。また、電源電位の供給が遮断されたときでもデータの保持が可能で、且つ、低消費電力化が可能なアナログデバイスを提供する。

【解決手段】アナログ素子を含むユニットセルにおいて、ユニットセルのスイッチとして、第1乃至第4のトランジスタを用い、第1のトランジスタと第2のトランジスタとが接続された第1のノード、及び、第3のトランジスタと第4のトランジスタが接続された第2のノードの電位を制御することで、ユニットセルの出力を導通状態、非導通状態、又はアナログ素子を介した導通状態のいずれかに切り替える半導体装置を提供する。

(もっと読む)

トリミング回路、トリミング回路の駆動方法

【課題】信頼性の高いトリミング回路を提供する。書き換え可能なトリミング回路を提供する。信頼性の高いトリミング回路の駆動方法を提供する。書き換え可能なトリミング回路の駆動方法を提供する。

【解決手段】オフリーク電流が極めて小さいトランジスタのソース電極またはドレイン電極に接続された記憶ノードと、該記憶ノードにゲート電極が接続されたトランジスタを用いてトリミング回路を構成する。また、該オフリーク電流が極めて小さいトランジスタを用いて、該記憶ノードにゲート電極が接続されたトランジスタのソース電極とドレイン電極に対して並列に接続された素子または回路のトリミング状態を制御する。

(もっと読む)

半導体集積装置

【課題】SiPのチップ間を接続するための端子数が増加する。

【解決手段】パッケージ内部に第1の半導体チップと第2の半導体チップが集積される半導体集積回路であって、前記第1の半導体チップは、第1の通信部と、複数のアナログ回路とを備え、前記第2の半導体チップは、第2の通信部と、前記複数のアナログ回路の特性調整用データを格納するメモリ部とを備え、前記第1の通信部と前記第2の通信部とがシリアルデータ通信線で接続され、前記シリアルデータ線を経由して前記第1の半導体チップが備える複数のアナログ回路の特性調整用データをそれぞれ複数のアナログ回路に転送する半導体集積回路。

(もっと読む)

半導体装置

【課題】 本実施形態は、出力ドライバのドライブ能力のキャリブレーション精度を向上することが可能な半導体装置を提供する。

【解決手段】 第1、第2のプルアップドライバユニットPUDUa、PUDUbは、プルアップドライバを調整する。プルダウンドライバユニットPDDUbは、プルダウンドライバを調整する。キャリブレーション回路CBCは、プルアップドライバのキャリブレーション時、基準電圧VREFと、基準抵抗RZQに基づく第1のプルアップドライバの出力電圧を比較して第1、第2のプルアップドライバユニットのドライブ能力を決定し、プルダウンドライバのキャリブレーション時、基準電圧と、第2のプルアップドライバとプルダウンドライバの接続ノードの電圧を比較してプルダウンドライバのドライブ能力を決定する単一の比較器COMPを有している。

(もっと読む)

可変インダクタ及びこれを用いた半導体装置

【課題】占有面積を大きくすることなく、インダクタンス値を変更できる可変インダクタを提供する。

【解決手段】本発明の可変インダクタ1は、スパイラルインダクタ2と、ループ導体5と、前記ループ導体5の一端を開放/短絡するスイッチ7と、を含む可変インダクタであって、前記ループ導体5は前記スパイラルインダクタ2に対して垂直方向に形成され、前記スイッチ7により前記ループ導体5の一端を開放/短絡することによって前記スパイラルインダクタ2のインダクタンス値を調整する機能を有する。

(もっと読む)

可変容量回路およびシステム

【課題】 電気信号の電圧振幅が大きいときにも、可変容量回路に形成されるトランジスタの寄生ダイオードがオンすることを防止し、電気信号の波形が歪むことを防止する。

【解決手段】 可変容量回路は、電気信号が伝達されるノードに一端が接続される容量素子と、容量素子の他端と第1電源線との間に配置される第1トランジスタと、他端と第2電源線との間に直列に配置される抵抗素子および第1トランジスタと極性が逆の第2トランジスタとを含んでいる。第1トランジスタはゲートで第1制御信号を受け、第1モード中にオンし、第2モード中にオフする。第2トランジスタは、ゲートで第2制御信号を受け、第1モード中にオフし、第2モード中にオンする。これにより、容量素子の他端の中心電圧は、第1トランジスタのオフ中に第2電源線の電圧に設定され、第2トランジスタのオフ中に第1電源線の電圧に設定される。

(もっと読む)

I/O積層体を含むシステム及びこのシステムを製造する方法

【課題】入出力(I/O)積層体を含むシステムを提供する。

【解決手段】入出力(I/O)積層体を含むシステム及びこのシステムを製造する方法が記述されている。一実装において、本方法は、I/O素子を含むと共に論理素子を含まないI/Oダイを積層するステップを有する。又、一実装において、本方法は、I/Oダイに対して集積回路ダイを積層するステップを更に含む。集積回路は、論理素子を含み、且つ、I/O素子を含まない。集積回路ダイからI/Oダイを分離することにより、それぞれのダイの独立的な開発や従来のダイのものとの比較におけるI/OダイのI/O基板上のI/O素子用の相対的に大きな空間などの様々な利益が得られる。空間の増大により、多数の論理素子を集積回路ダイの基板の同一の表面積内に収容する集積回路ダイの新しいプロセス世代が可能となる。

(もっと読む)

1 - 20 / 271

[ Back to top ]