Fターム[5F038AV17]の内容

半導体集積回路 (75,215) | 可変インピーダンス (2,334) | 可変回路(他素子のインピーダンスを使用) (1,117) | スイッチ素子による切換 (1,056) | 変更可能 (261)

Fターム[5F038AV17]の下位に属するFターム

制御回路 (138)

Fターム[5F038AV17]に分類される特許

1 - 20 / 123

磁気抵抗素子構造の製造方法

【課題】本発明は、磁気抵抗材料と集積回路とを巧みに統合することのできる、磁気抵抗素子構造の製造方法を提供する。

【解決手段】基板を提供する工程と、上記基板の上に金属ダマシン構造を形成する工程と、該金属ダマシン構造に電気的に接続するように該金属ダマシン構造の上にパターン化磁気抵抗ユニットを形成する工程とを含む、磁気抵抗素子構造の製造方法である。

(もっと読む)

半導体装置

【課題】高品質な半導体装置を提供する。

【解決手段】第1の絶縁膜111、第1の電極112、第2の絶縁膜113、及び第2の電極114を含むゲート構造を有するメモリセルMCが複数設けられた記憶部11と、少なくとも外部100からのデータを受信し、記憶部にデータを供給する端子15と、第1の絶縁膜、第1及び第2の電極とを含むゲート構造を有し、電流経路の一端に第1の電圧が印加される第1導電型の第1のトランジスタ16a、一端が第1のトランジスタの電流経路の他端に接続され、他端が端子に接続される第1の抵抗素子16b、一端が端子及び第1の抵抗素子の他端に接続される第2の抵抗素子16c及び、ゲート構造を有し、電流経路の一端が第2の抵抗素子の他端に接続され、電流経路の他端に第2の電圧が印加される第2導電型の第2のトランジスタ16dを含む第1の回路16と、を備える。

(もっと読む)

アナログ/デジタル変換器

【課題】変換精度が高いアナログ/デジタル変換器を提供する。

【解決手段】アナログ/デジタル変換器は、電圧生成部と複数の比較器とを備える。電圧生成部は、基準電圧を、複数の抵抗器で分圧して複数の比較用電圧を生成する。各比較器は、複数の比較用電圧のうちの何れかの比較用電圧とアナログの入力電圧との比較結果に応じたデジタル信号を出力する。各比較器は、2つの入力の電位差を検出する差動対回路を含む。差動対回路は、第1回路部50と第2回路部60とを有する。第1回路部は、第1入力トランジスタ51と、第1入力トランジスタと直列に接続される抵抗器Rrefとを含む。第2回路部は、第1入力トランジスタと差動対を形成する第2入力トランジスタ61と、第2入力トランジスタと直列に接続される可変抵抗器Rvとを含む。可変抵抗器は、直列に接続されるとともに、制御信号に応じて各々の抵抗値が可変に設定される複数の可変抵抗素子を含む。

(もっと読む)

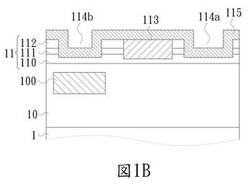

半導体装置

【課題】抵抗値が制御されることができる抵抗素子を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101と、絶縁膜14bと、半導体素子と、抵抗素子4tとを有する。絶縁膜14bは半導体基板101の少なくとも一部を被覆している。半導体素子は、半導体基板101の一部からなるチャネル領域と、電極とを有する。抵抗素子4tは、電極を流れる電流に対する抵抗となるように電極と電気的に接続され、かつ絶縁膜14bを介して半導体基板101上に設けられている。抵抗素子4tは半導体領域を含む。半導体基板101と抵抗素子4tとの間の電位差により半導体領域に空乏層が生じる。

(もっと読む)

集積回路

【課題】電力消費量の増大を抑制しつつ、タイミング信号のスキューを低減する。

【解決手段】主クロック分配回路は、タイミング信号を複数の主タイミング信号に分岐して分配する。副クロック分配回路は、タイミング信号の分配が指示された場合にはタイミング信号を複数の副タイミング信号に分岐して分配する。最小遅延タイミング信号出力部は、複数の主タイミング信号のいずれかと複数の副タイミング信号のいずれかとのうち先に分配された信号を最小遅延タイミング信号として出力する。同期動作回路は、最小遅延タイミング信号に同期して動作する。測定部は、複数の主タイミング信号のいずれかの遅延のばらつきを示す値を測定する。クロック分配回路制御部は、測定された値の示す前記ばらつきが前記所定値以上であるときに副分配回路に前記タイミング信号の分配を指示する。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの集積度が高い半導体装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、第1領域において上面に第1方向に延びる複数本のフィンが形成された半導体基板と、前記第1方向に対して交差した第2方向に延び、前記フィンを跨ぐ第1ゲート電極と、前記フィンと前記第1ゲート電極との間に設けられた第1ゲート絶縁膜と、前記第2領域において前記半導体基板上に設けられた第2ゲート電極と、前記半導体基板と前記第2ゲート電極との間に設けられた第2ゲート絶縁膜と、を備える。そして、前記第1ゲート電極の層構造は、前記第2ゲート電極の層構造とは異なる。

(もっと読む)

半導体装置及びその製造方法

【課題】容量値及びその変化量が大きく且つQ値の高い可変容量素子を備える半導体装置及びその製造方法を実現する。

【解決手段】半導体装置は、可変容量素子を備え、当該可変容量素子は、半導体基板11上に形成された下部電極13と、下部電極13上に形成された容量絶縁膜14と、容量絶縁膜14上に形成された上部電極15とを備える。上部電極15は、容量絶縁膜14上に位置する低濃度不純物層15aと、低濃度不純物層15a上に位置し且つ低濃度不純物層15aよりも不純物濃度が高い高濃度不純物層15bとを有する。

(もっと読む)

定電流回路

【課題】 1つのトリミング抵抗により出力電流の増加方向と減少方向の両方向の調整が可能な定電流回路を提供する。

【解決手段】 トリミング抵抗TR11と抵抗R11の電圧降下をトランジスタ対Q14、Q15により比較し、トリミング抵抗TR11の電圧降下が抵抗R11より小さい場合は、トランジスタQ11にトリミング抵抗に流れる電流のみを流し、トリミング抵抗TR11の電圧降下が抵抗R11より大きい場合は、トランジスタQ11にトリミング抵抗に流れる電流に加えて、トランジスタQ17から電流を供給する。この回路構成により、トリミング抵抗の抵抗値の増加に従い、出力電流Ioutが減少した後、増加する特性を得ることができる。

(もっと読む)

半導体集積回路の電源制御システムおよび電源制御方法

【課題】 半導体集積回路に電源ノイズが発生した場合に電源配線のインピーダンスおよび電源電圧を低下させることができ、これにより電源ノイズ振幅を抑えかつ消費電力を低減させることが可能な半導体集積回路の電源制御システムの提供。

【解決手段】 可変電圧源2と、その電源が供給される半導体集積回路3,4と、可変電圧源を制御する電源制御回路1とを含み、半導体集積回路は、インダクタンス31と内部素子容量43bとから構成される並列共振回路と、並列共振回路の電源配線上に設けられる可変抵抗41と、可変電圧源から並列共振回路に供給される電圧と基準電圧とを比較しその比較結果を出力する電圧センサー42とを含んでおり、電源制御回路は、電源配線に流れる信号の周波数に応じて可変抵抗の値を選択し、電圧センサーの出力結果に応じて可変電圧源に所定の電圧値を設定する。

(もっと読む)

集積回路装置及び電子機器

【課題】高精度にインピーダンスマッチングできる集積回路装置及び電子機器等を提供すること。

【解決手段】集積回路装置100は、アンテナANを介して入力される信号を受信する受信回路10と、アンテナANを介して信号を送信する送信回路20と、可変容量回路30と、を含む。受信回路10の入力ノードと、送信回路20の出力ノードは、一端がアンテナANに接続される整合回路200の他端のノードである第1のノードN1に接続される。可変容量回路30は、第1のノードN1に接続され、受信回路10及び送信回路20の少なくとも一方の動作状態に応じて容量値が可変に設定される。

(もっと読む)

半導体集積回路、半導体チップ、及び半導体集積回路の設計手法

【課題】容易な設計により、小規模な構成でクロックスキューを抑制させる半導体集積回路を提供する。

【解決手段】ラッチ回路31〜316のデータ入力端子とデータビットの供給元PDとの間に、クロック信号CLLの供給元PCD及びラッチ回路のクロック入力端子間のクロック信号経路中に含まれている論理素子の個数と同一数だけ当該論理素子を直列に接続してなる第1遅延部51,52と、クロック信号経路中の配線の配線長に対応した配線遅延時間と同一長の遅延時間を有する第2遅延部53と、を備える。

(もっと読む)

抵抗分割回路及び電圧検出回路

【課題】スイッチ素子のオン抵抗の影響を排除することにより、トリミングの誤差が特定の条件において大きくなることを回避することができる抵抗分割回路、さらには精度がよい電圧検出回路を提供する。

【解決手段】直列接続した抵抗値に重み付けをした複数の抵抗素子と、抵抗素子とそれぞれ並列に接続されたスイッチ素子とを備えた抵抗分割回路で、対応する抵抗素子の抵抗値とスイッチ素子がショート状態のときの抵抗値との比を一定となるように構成した。

(もっと読む)

半導体装置

【課題】広範囲、光分解能に周波数を可変することのできるクロック信号を生成する。

【解決手段】オペアンプAMP1は、正入力部と負入力部が等しい電圧となるようフィードバックがかかり、回路ノードfbckは、参照電圧VREFIに等しい電圧となる。デコーダDECは、制御信号CNT7,CNT6をデコードし、トランジスタT2〜T5のいずれか1つをオンさせる。この構成によって、回路ノードfbckが、参照電圧VREFIと同電位となるようフィードバック制御がかかるため、トランジスタT2〜T5のON抵抗を大幅に低減することができ、周波数精度の悪化を防止することができる。

(もっと読む)

半導体装置、回路基板装置及び情報処理装置

【課題】小規模な回路で送受信に応じた最適なインピーダンス調整を行う。

【解決手段】選択部15が、送信部11のインピーダンス調整時か、受信部12のインピーダンス調整時かに応じて異なる基準電圧を選択し、選択した基準電圧を基準電圧生成部14に生成させ、基準電圧生成部14が、選択部15により選択された基準電圧を生成して、インピーダンス調整部13に入力し、インピーダンス調整部13が、入力された基準電圧に応じて、送信部11または受信部12のインピーダンスを別々に調整する。

(もっと読む)

半導体装置

【課題】 制御端子が浮遊状態になると、予期しないリーク電流などにより電極に電荷が蓄積され、電極の電位が変動し、スイッチが誤動作してしまう可能性がある。

【解決手段】 クーロン力により湾曲させることで第1の信号電極と第2の信号電極とを接触または分離することが可能な架橋部と、前記架橋部を制御するための制御端子とを有するスイッチ素子と、前記制御端子に接続された第1の不揮発性半導体素子と、前記制御端子および前記第1の不揮発性半導体素子に接続された第2の不揮発性半導体素子とを備える。

(もっと読む)

半導体装置の製造方法

【課題】前工程においてトランジスタごとに不純物の種類や量を変えることによる、製造コストや製造時間の増大を抑制する。

【解決手段】本発明による半導体装置の製造方法は、第1の閾値電圧及び第1のドレイン・ソース間電流を呈するようなデバイスパラメータをもって設計された第1のトランジスタを含む半導体回路を形成する半導体回路形成工程(ステップS11)と、第1のトランジスタにストレス電圧を印加して第1の閾値電圧とは異なる第2の閾値電圧及び前記第1のドレイン・ソース間電流とは異なる第2のドレイン・ソース間電流の少なくとも一方を第1のトランジスタが呈するようにする特性制御工程(ステップS14)と、第1のトランジスタが第2の閾値電圧及び第2のドレイン・ソース間電流の少なくとも一方を呈する状態で出荷する出荷工程(ステップS16)とを備える。

(もっと読む)

抵抗値補償方法、抵抗値補償機能を有する回路、回路の抵抗値試験方法、抵抗値補償プログラム、回路の抵抗値試験プログラム及びシステム

【課題】簡易で精度の高いODT回路の抵抗補償方式を提供することを目的とする。

【解決手段】複数のトランジスタの組み合わせによって所望の抵抗値と同等の抵抗値を実現するODT回路200であって、組み合わせるべきトランジスタを順次選択することにより、選択されたトランジスタによって実現される抵抗値を順次変化させる構成である。

(もっと読む)

半導体集積回路装置

【課題】可変容量範囲が広く、単位面積当たりの容量値が大きいMOS型バラクタ素子を備えた半導体集積回路装置を提供する。

【解決手段】半導体集積回路装置において、P型基板PSubの表面にNチャネルトランジスタ1、Pチャネルトランジスタ2及びMOS型バラクタ素子3を設ける。そして、MOS型バラクタ素子3のゲート絶縁膜14を、Nチャネルトランジスタ1及びPチャネルトランジスタ2のゲート絶縁膜4よりも薄くする。また、MOS型バラクタ素子3のウエル端子Vbとゲート端子Vgとの間に印加するゲート電圧の最大値を、Nチャネルトランジスタ1及びPチャネルトランジスタ2に印加するゲート電圧の最大値よりも低くする。

(もっと読む)

半導体装置及びその製造方法

【課題】抵抗変化素子を半導体装置に組み込む際の必要なフォトマスクを削減しても高密度化が可能な抵抗変化素子を搭載した半導体装置及びその製造方法を提供すること。

【解決手段】配線溝を有する層間絶縁膜14と、配線溝に埋め込まれた配線16aと、配線16aを含む層間絶縁膜14上に形成されるとともに、配線16aに通ずる下穴を有する層間絶縁膜18と、少なくとも下穴が配置された領域における配線16a上に形成されるとともに、抵抗が変化する抵抗変化膜19aと、下穴が配置された領域における抵抗変化膜19a上に形成されたバリアメタル20aと、下穴が配置された領域におけるバリアメタル20a上に形成されたプラグ21aと、を備え、抵抗変化素子5は、第1電極と第2電極との間に抵抗変化膜19aが介在した構成となっており、配線16aは、第1電極を兼ね、バリアメタル20aは、第2電極を兼ねる。

(もっと読む)

温度センサと、半導体装置およびその較正方法

【課題】出力電圧の温度依存性を示す曲線の曲率が小さく、レイアウト面積が小さな温度センサを提供する。

【解決手段】この温度センサは、アノードがノードN1に接続されたダイオードD0と、アノードが抵抗素子8を介してノードN2に接続されたダイオードD1〜Dnと、ノードN1,N2の電圧を一致させる演算増幅器1と、抵抗素子9,10を介してノードN1,N2に接続され、抵抗素子9,10に流れる電流を調整し、温度センサの出力電圧VOの温度依存性を示す曲線の曲率を小さくする電圧調整回路12を備える。したがって、2つのサブ温度センサを設ける従来に比べ、レイアウト面積が小さくて済む。

(もっと読む)

1 - 20 / 123

[ Back to top ]