Fターム[5F038AV18]の内容

半導体集積回路 (75,215) | 可変インピーダンス (2,334) | 可変回路(他素子のインピーダンスを使用) (1,117) | スイッチ素子による切換 (1,056) | 変更可能 (261) | 制御回路 (138)

Fターム[5F038AV18]に分類される特許

1 - 20 / 138

半導体集積回路

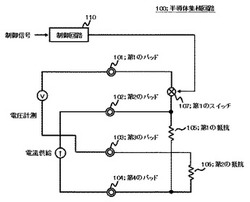

【課題】半導体集積回路に含まれる終端抵抗の抵抗値を4端子法によって測定をするためには、必要となる端子が増加し、半導体集積回路のチップサイズが増加するという問題がある。そのため、半導体集積回路のチップサイズ増加を抑制しつつ、終端抵抗の抵抗値を高精度で測定可能な半導体集積回路が、望まれる。

【解決手段】半導体集積回路は、第1乃至第4のパッドと、第2のパッドと第4のパッドの間に接続される第1の抵抗と、第3のパッドと第4のパッドの間に接続される第2の抵抗と、第1のパッドと第2のパッドの間に接続される第1のスイッチと、第1のパッド及び第3のパッドを4端子法における電圧測定端子として、第2のパッド及び第4のパッドを4端子法における電流供給端子として、それぞれ使用し第1の抵抗の抵抗値を測定するテストモードへの遷移指示を含む制御信号に基づき、第1のスイッチをオンする制御回路と、を備える。

(もっと読む)

半導体装置

【課題】発振周波数変動の許容範囲を任意に設定可能にする。

【解決手段】半導体装置(21)は、トリミングレジスタ(11)に保持されたトリミング値によって発振周波数が変更される発振器(12)と、発振周波数を補正可能な補正回路(20)とを含む。上記補正回路は、上限値を設定可能な上限値レジスタ(6)と、下限値を設定可能な下限値レジスタ(7)と、発振周波数を分周するための分周回路(13)と、分周回路の出力をカウントするカウンタ(3)とを含む。さらに上記補正回路は、カウンタの出力を保持可能なバッファレジスタ(4)と、バッファレジスタの保持値が、上限値と下限値との間に入っているか否かを判別する比較器(5)と、その判別結果に基づいてトリミング値を補正するトリミング値補正制御回路(8)とを含む。ユーザは、上限値と下限値とによって、発振周波数変動の許容範囲を任意に設定することができる。

(もっと読む)

半導体装置

【課題】電源線と機能回路の間に電源スイッチとして接続されるMOSトランジスタのオン時のバックゲートの電圧を簡単な構造で調整することができる半導体装置を提供する。

【解決手段】一対の電源線2、3と、機能回路4a0〜4anと、一対の電源線2、3との少なくとも一方と機能回路4a0〜4anの間に接続されるスイッチング回路6a0〜6an、7a0〜7anとを有し、スイッチング回路6a0〜6an、7a0〜7anは、ソース/ドレインの一方が機能回路4a0〜4anに接続され、他方が前記一対の電源線2、3の一方に接続される第1のMOSトランジス11と、第1のMOSトランジスタ11のゲートとバックゲートを接続する抵抗素子12、21と、第1のMOSトランジスタ11のゲートに接続されるゲート電圧制御回路13と、を有する。

(もっと読む)

アナログ/デジタル変換器

【課題】変換精度が高いアナログ/デジタル変換器を提供する。

【解決手段】アナログ/デジタル変換器は、電圧生成部と複数の比較器とを備える。電圧生成部は、基準電圧を、複数の抵抗器で分圧して複数の比較用電圧を生成する。各比較器は、複数の比較用電圧のうちの何れかの比較用電圧とアナログの入力電圧との比較結果に応じたデジタル信号を出力する。各比較器は、2つの入力の電位差を検出する差動対回路を含む。差動対回路は、第1回路部50と第2回路部60とを有する。第1回路部は、第1入力トランジスタ51と、第1入力トランジスタと直列に接続される抵抗器Rrefとを含む。第2回路部は、第1入力トランジスタと差動対を形成する第2入力トランジスタ61と、第2入力トランジスタと直列に接続される可変抵抗器Rvとを含む。可変抵抗器は、直列に接続されるとともに、制御信号に応じて各々の抵抗値が可変に設定される複数の可変抵抗素子を含む。

(もっと読む)

半導体装置

【課題】抵抗値が制御されることができる抵抗素子を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101と、絶縁膜14bと、半導体素子と、抵抗素子4tとを有する。絶縁膜14bは半導体基板101の少なくとも一部を被覆している。半導体素子は、半導体基板101の一部からなるチャネル領域と、電極とを有する。抵抗素子4tは、電極を流れる電流に対する抵抗となるように電極と電気的に接続され、かつ絶縁膜14bを介して半導体基板101上に設けられている。抵抗素子4tは半導体領域を含む。半導体基板101と抵抗素子4tとの間の電位差により半導体領域に空乏層が生じる。

(もっと読む)

集積回路

【課題】電力消費量の増大を抑制しつつ、タイミング信号のスキューを低減する。

【解決手段】第1のクロック分配回路は、タイミング信号を複数の第1の分配点に分配する。第2のクロック分配回路は、タイミング信号を複数の第2の分配点に分配する。最小遅延クロック信号出力部は、複数の第1の分配点のいずれかに分配されたタイミング信号と複数の第2の分配点のいずれかに分配されたタイミング信号とのうち遅延が小さい方の信号を最小遅延タイミング信号として出力する。同期動作回路は、最小遅延タイミング信号に同期して動作する。

(もっと読む)

半導体装置

【課題】従来の半導体装置では、エンファシスの有無により消費電流が変動する問題があった。

【解決手段】本発明の半導体装置は、抵抗値を、エンファシスモードにおいて第1の抵抗値とし、非エンファシスモードにおいて第1の抵抗値よりも小さな第2の抵抗値とする可変抵抗30と、出力インピーダンスを、エンファシスモードにおいて第3の抵抗値とし、非エンファシスモードにおいて前記第3の抵抗値よりも大きな第4の抵抗値とする第1の駆動部10と、出力インピーダンスを、エンファシスモードにおいて第5の抵抗値とし、非エンファシスモードにおいて第5の抵抗値よりも大きな第6の抵抗値とする第2の駆動部11と、入力信号に応じて第1、第2の駆動部の導通状態を制御すると共に、エンファシスモードと非エンファシスモードとにおいて第1、第2の駆動部の出力インピーダンスと可変抵抗の抵抗値を切り換える制御部と、を有する。

(もっと読む)

半導体装置

【課題】製造プロセスによる閾値電圧の変動に起因する歩留まりの悪化を抑制可能な半導体装置を提供する。

【解決手段】半導体装置は、複数のトランジスタが並列に接続された所定並列回路と、複数のトランジスタのオンオフ状態を制御しつつ所定並列回路のインピーダンスが所定値になったかを検出し、該インピーダンスが所定値になったときの複数のトランジスタのオンオフ状態に応じた制御値を生成する制御値生成部と、電源電圧を生成する電圧発生部と、電源電圧で動作する動作トランジスタと、制御値に基づいて電源電圧を制御する制御部と、を含む。

(もっと読む)

可変容量装置

【課題】 回路の小型化と消費電力の低減が可能な可変容量装置を提供する。

【解決手段】 容量検出回路31は、可変容量素子2の駆動容量C1のキャパシタンス値に応じた検出信号Sxと、基準となる基準信号Syとを出力する。駆動電圧制御回路21は、検出信号Sxと基準信号Syとを比較し、この比較結果に応じて駆動電圧Vcontを制御し、駆動容量C1を増加または減少させる。駆動容量C1の一端側には駆動電圧Vcontが印加され、他端側には容量検出回路31の検出用電流回路33から検出用電流Icontが周期的に入力される。このため、駆動容量C1が検出用電流回路33に接続されると、駆動容量C1のキャパシタンス値と検出用電流Icontの大きさとに応じて、駆動容量C1の他端側の電圧が上昇し、この電圧に応じた検出信号Sxが出力される。

(もっと読む)

半導体装置及びその駆動方法

【課題】信号処理回路に対する電源電圧の供給及び遮断を選択することができるスイッチとして機能する回路(電源供給制御回路)として好ましい回路を提供する。

【解決手段】信号処理回路に対する電源電位の供給を担う第1の配線と、電源電位を供給する第2の配線との電気的な接続を制御するトランジスタ、及び、信号処理回路に対する電源電位の供給を担う第1の配線を接地させるか否かを制御するトランジスタとを設け、当該2つのトランジスタの少なくとも一方として、チャネルが酸化物半導体層に形成されるトランジスタを適用する。これにより、2つのトランジスタの少なくとも一のカットオフ電流に起因する消費電力を低減することが可能となる。

(もっと読む)

インダクタ

【課題】基体上に形成された絶縁膜中の多層配線層を用いたインダクタの、上下隣接配線間の寄生容量を低減する。

【解決手段】基体16上の絶縁膜17中に配設された複数の配線層18のうち、隣接する少なくとも2つの配線層の各々に形成された一周回の周回配線(A-B又はB-C)を有し、前記少なくとも2つの配線層に形成された前記一周回の周回配線(A-B及びB-C)の一端(B)は相互にビア2で接続され、前記少なくとも2つの配線層に形成された前記一周回の周回配線(A-B及びB-C)は、基体上方から見て基体面内で実質的に同一位置に配設されることを特徴とするインダクタ。

(もっと読む)

集積回路装置及び電子機器

【課題】高精度にインピーダンスマッチングできる集積回路装置及び電子機器等を提供すること。

【解決手段】集積回路装置100は、アンテナANを介して入力される信号を受信する受信回路10と、アンテナANを介して信号を送信する送信回路20と、可変容量回路30と、を含む。受信回路10の入力ノードと、送信回路20の出力ノードは、一端がアンテナANに接続される整合回路200の他端のノードである第1のノードN1に接続される。可変容量回路30は、第1のノードN1に接続され、受信回路10及び送信回路20の少なくとも一方の動作状態に応じて容量値が可変に設定される。

(もっと読む)

抵抗値補償方法、抵抗値補償機能を有する回路、回路の抵抗値試験方法、抵抗値補償プログラム、回路の抵抗値試験プログラム及びシステム

【課題】簡易で精度の高いODT回路の抵抗補償方式を提供することを目的とする。

【解決手段】複数のトランジスタの組み合わせによって所望の抵抗値と同等の抵抗値を実現するODT回路200であって、組み合わせるべきトランジスタを順次選択することにより、選択されたトランジスタによって実現される抵抗値を順次変化させる構成である。

(もっと読む)

可変抵抗回路を備えた半導体集積回路

【課題】トリミング用のスイッチ素子のオン抵抗によって抵抗値に誤差が生じることがなく、電源電圧依存性や温度依存性もなくレイアウト面積も小さい可変抵抗回路を備えた半導体集積回路を提供すること。

【解決手段】複数の抵抗を直列に接続した抵抗回路と、複数の抵抗の直列に接続する数を選択する複数のスイッチ素子を有する選択回路と、スイッチ素子のオン抵抗値を制御する制御回路と、を備え、制御回路はスイッチ素子のオン抵抗値と抵抗回路の抵抗の抵抗値とが所定の比になるように制御する、構成とした。

(もっと読む)

アナログ電圧調整回路、及びアナログ電圧調整方法

【課題】検査工程と調整工程をほぼ同時に実行可能な、アナログ電圧調整回路を提供する。

【解決手段】アナログ電圧調整回路1は、外部装置から、目標電圧を示す目標電圧信号を入力する、目標電圧入力端子12と、目標電圧信号に基づいて生成された目標電圧を示すデータを取り込み、期待値データとして格納する、期待値データ格納回路7と、トリミングデータを格納し、トリミングデータに応じたトリミング信号を出力する、トリミングデータ格納回路11と、トリミング信号を取得し、トリミングデータに応じた電圧レベルで、アナログ出力信号を出力する、アナログ信号出力回路2と、アナログ出力信号の電圧レベルを示す測定データと、格納された前記期待値データとを比較し、比較結果を示す比較結果信号を生成する比較回路8と、比較結果信号に基いて、トリミングデータを変更するか否かを決定する、制御回路10とを具備する。

(もっと読む)

プログラマブル論理回路装置及び画像処理装置

【課題】 節電効率を向上させることができるプログラマブル論理回路装置及び画像処理装置を提供する。

【解決手段】 本発明のプログラマブル論理回路装置100は、素子間の接続の変更により再構成される回路を備える複数の再構成領域R0、R1、R2、R3及びR4と、複数の再構成領域R1、R2、R3及びR4の各々に対して、実行させる処理を割り当てて、複数の再構成領域R1、R2、R3及びR4の各々が実行する処理の状態に基づいて、複数の再構成領域R1、R2、R3及びR4を選択的に再構成して節電状態にする管理領域である再構成領域R0と、を有する。

(もっと読む)

半導体装置及び半導体装置の試験方法

【課題】テストコストの低減及び不良解析の精度向上を図った半導体装置を提供する。

【解決手段】半導体装置100は、被調整電源13の出力である被調整電源出力電圧Vaを調整するトリミングコードTRMC(=TRMC1)を変化させながら発生し、被調整電源出力電圧Vaが入力電圧Vinに対応する値となった場合、電圧供給回路25の出力電圧Voutの基準電圧Vrefと同じ電圧レベルに出力変更し、入力初段回路へ供給する。また、トリミングコードTRMCをトリミングコード記憶回路16に記憶し、記憶したトリミングコードTRMC(=TRMC2)に基づき被調整電源出力電圧Vaを設定する。

(もっと読む)

半導体集積回路装置及びその温度補正方法

【課題】簡単な構成で基準信号の温度補正を行うことができる半導体集積回路装置及びその温度補正方法を提供することを目的とする。

【解決手段】少なくとも3つの異なる温度で半導体集積回路の信号発生手段21,22の出力する基準信号の値を測定し、測定した基準信号の値を目標値とするため信号発生手段のトリミング手段に与える補正制御データを求め、3つの温度で得た信号発生手段のトリミング手段に与える補正制御データから半導体集積回路の使用温度範囲における各温度の補正制御データを算出し、各温度の補正制御データを温度と対応付けて格納手段56に格納し、半導体集積回路の温度検出手段23で検出した温度に応じて格納手段から信号発生手段のトリミング手段に与える補正制御データを読み出して信号発生手段のトリミング手段に設定し、信号発生手段が出力する基準信号の温度補正を行う。

(もっと読む)

半導体装置、及びその設計方法

【課題】小さいチップサイズで、ノイズを低減することできる半導体装置、及びその設計方法を提供すること。

【解決手段】本発明の一態様に係る半導体装置は、入力に応じて容量が変化する素子13を備え、所定の機能を有する機能マクロ11と、機能マクロ11の不使用時において、素子13によって機能マクロ11の容量を制御するものである。これにより、小さいチップサイズで、ノイズを低減することできる半導体装置、及びその設計方法を提供することができる。

(もっと読む)

インピーダンス調節装置

【課題】小さい面積でも正確なインピーダンス値でターミネーション動作をするインピーダンス調節装置を提供する。

【解決手段】基準電圧VREFとキャリブレーションノードZQの電圧とを比較する比較部410と、比較部410の比較結果UP/DOWNに応じてインピーダンスコードPCODE<0:N>をカウントするカウント部420と、インピーダンスコードPCODEによって決定されるインピーダンス値を有し、キャリブレーションノードZQに連結されるレファレンスインピーダンス部430と、インピーダンスコードPCODEの生成完了時に、比較部410の比較結果を保存する保存部440と、インピーダンスコードPCODE<0:N>に応答してオン・オフされる複数の並列抵抗611〜615と、保存部440に保存された信号TRIMに応答してオン・オフされる抵抗616とで、所定のパッドをターミネーションするターミネーション部とを備える。

(もっと読む)

1 - 20 / 138

[ Back to top ]