Fターム[5F064FF27]の内容

ICの設計・製造(配線設計等) (42,086) | 切り換え、選択 (3,709) | 切り換え、選択部分の素子 (1,619) | フューズ (1,286) | 切断するもの (497)

Fターム[5F064FF27]に分類される特許

1 - 20 / 497

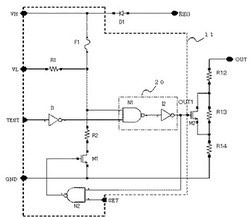

トリミング回路及び調整回路

【課題】ヒューズ素子の仮想切断を可能にすると共に、高電圧又は大電流によるヒューズ溶断の際に、周辺回路を破損する確率も低減できる信頼性の高いトリミング回路を提供する。

【解決手段】ヒューズトリミングを行うための回路であって、トリミングヒューズと、

前記トリミングヒューズに接続されるトリミング用のパッド端子と、仮想切断時に制御信号を入力するテスト端子と、入力端子の一方が前記テスト端子に接続され他方が前記トリミングヒューズに接続され、入力された制御信号に応じた制御信号を出力する制御回路と、を有し、前記トリミングヒューズの切断により、前記制御回路の他方の入力端子がGNDレベルへプルダウンする手段を備えたことを特徴とする。

(もっと読む)

半導体集積回路およびそれを用いた光センサ機器

【課題】修正前の特性値がその特性値の出現頻度分布における平均値±2×(標準偏差)の範囲に入る製造品に対するヒューズ溶断本数を少なくする。

【解決手段】素子アレイ14には抵抗アレイを設け、特性値の分布の平均値を素子アレイ14で得られる合成抵抗値の中央値に対応付け、トリミング情報生成回路12における上記中央値より大きい合成抵抗値に対応するトリミング情報の配列を、10進数で「15」〜「8」の降順に、上記中央値以下の合成抵抗値に対応するトリミング情報の配列を、10進数で「0」〜「7」の昇順に設定する。変換回路13は、トリミング情報生成回路12からのトリミング情報を変換して、素子アレイ14の抵抗アレイから各合成抵抗値を得るためにオフする抵抗を選択する素子選択情報を生成する。こうして、上記分布における「平均値±2σ」の範囲内に対応付けられトリミング情報を生成する場合のヒューズ溶断数を大幅に削減する。

(もっと読む)

半導体回路装置およびその製造方法

【課題】ビアヒューズ素子の径を小さくし、ビアヒューズ素子を低電流で溶断することが可能な半導体回路装置およびその製造方法を提供する。

【解決手段】一方向に配置された複数の配線層と、前記複数の配線層のうちの少なくとも2つの前記配線層の間に設けられたビアヒューズ素子と、前記複数の配線層の配置方向に直交する平面内において前記ビアヒューズ素子に隣接する穴と、前記穴内に設けられた貫通ビアとを備えた半導体回路装置。

(もっと読む)

半導体装置及びトリミング方法

【課題】ヒューズ素子の列数増に伴うトリミング時間の伸長を抑制する。

【解決手段】x方向に延伸する接地配線Gと、接地配線のy方向の一方側に設けられたヒューズ素子領域Aにx方向に沿って3列に並べて配置され、かつそれぞれの一端が接地配線Gに共通に接続される複数のヒューズ素子と、ヒューズ素子領域Aを挟んで接地配線Gの反対側に設けられ、ヒューズ素子領域Aに配置された複数のヒューズ素子それぞれの他端と接続される救済回路とを備え、上記複数のヒューズ素子は、それぞれ1つの欠陥選択線を示すアドレス情報を記憶する複数のヒューズ素子グループに所定個ずつグループ化され、同一のヒューズ素子グループに属する所定個のヒューズ素子は、同一列に配置されることを特徴とする

(もっと読む)

ヒューズ素子読み出し回路

【課題】十分な読み出しマージンを確保し、ヒューズ素子のデータ読み出しの際に誤判定を防止することができるヒューズ素子読み出し回路を提供することを課題とする。

【解決手段】切断済みと未切断とで抵抗値が異なる第1のヒューズ素子(115)と、通常モードと試験モードとで異なる抵抗値を有する第1の抵抗回路(701,702)と、前記第1のヒューズ素子の抵抗値及び前記第1の抵抗回路の抵抗値に応じた読み出し電圧を出力する読み出し電圧出力回路(101)とを有することを特徴とするヒューズ素子読み出し回路が提供される。

(もっと読む)

半導体装置および半導体パッケージ

【課題】パッドが設けられた面の向きを変えても、パッドを基板に接続するボンディングワイヤが交差しない半導体装置を提供する。

【解決手段】複数のパッドを含む第1のパッド群と、第1のパッド群に平行に一列に配置された複数のパッドを含む第2のパッド群と、第1のパッド群を基準にして第2のパッド群とは反対側に設けられた複数のバッファ回路を含む第1のバッファ回路群と、第2のパッド群を基準にして第1のパッド群とは反対側に設けられた複数のバッファ回路を含む第2のバッファ回路群と、第1のパッド群の複数のパッドのそれぞれを第2のバッファ回路群の複数のバッファ回路のそれぞれに対応して接続する複数の第1の配線と、第2のパッド群の複数のパッドのそれぞれを第1のバッファ回路群の複数のバッファ回路のそれぞれに対応して接続する複数の第2の配線と、を有する。

(もっと読む)

半導体記憶素子及び半導体記憶装置

【課題】LSI素子の性能劣化及びヒューズ素子の欠陥の増加を抑制できる半導体記憶素子及び半導体記憶装置を提供する。

【解決手段】半導体記憶素子100は、第1ヒューズ線111と、第1ヒューズ線111と並列接続された第2ヒューズ線112とを有し、切断されているか否かによって2値のデータを保持するヒューズ素子110と、一端がワード線130に接続されており、ヒューズ素子110に電流を流すか否かを選択する選択素子120と、を備える。

(もっと読む)

半導体装置

【課題】多層配線プロセスでSOGエッチバックにて平坦化を行なうプロセスにて、ヒューズ開口部に起因する水分の浸入における長期信頼性の劣化を防止する半導体装置の製造方法を提供する。

【解決手段】ヒューズ開口部からの水分侵入を防ぐためのメタル1層目のガードリングの下部まで多結晶シリコンが伸びているヒューズ形状にする。これによりヒューズの電極をとるためのメタル配線とガードリングのメタル配線の高さがそろい、SOG層がIC内部に到達することを防ぐことが可能となる。

(もっと読む)

半導体ウエハ、半導体装置、および、半導体装置の製造方法

【課題】半導体チップのチップ面積の削減を図るとともに、半導体チップへの入力を記憶させる時間を短縮する。

【解決手段】本発明の半導体ウエハ1は、チップ領域10に形成され、絶縁膜を有し、電圧の印加による絶縁膜の絶縁破壊により導通状態となる複数のアンチヒューズ14を有するアンチヒューズ回路12と、チップ領域10を区画するダイシング領域20に複数のアンチヒューズ14の各々に対応して形成され、配線を有し、レーザー照射による配線の切断により非導通状態となる複数のレーザーヒューズ24を有するレーザーヒューズ回路22と、複数のアンチヒューズ14のうち、半導体チップへの入力に応じて非導通状態とされたレーザーヒューズ22に対応するアンチヒューズ14の有する絶縁膜に、電源からの電圧を印加させて、そのアンチヒューズ14を導通状態とする制御回路13と、を有する。

(もっと読む)

半導体装置

【課題】抵抗体とヒューズ素子が並列に接続された半導体装置において、ヒューズ素子切断時に抵抗体への損傷がなく、抵抗体とヒューズ素子とを積層すること。

【解決手段】半導体基板上に第1の絶縁膜を介して形成された抵抗体を設け、抵抗体の上に第2の絶縁膜を介して形成された遮光層を設け、遮光層の上に第3の絶縁膜を介して形成されたヒューズ素子のヒューズ部を有し、抵抗体と遮光層とヒューズ部を重畳した半導体装置とする。

(もっと読む)

半導体装置

【課題】ヒューズ開口部からの水分侵入による電特異常及び配線腐食を防止する半導体装置を提供する。

【解決手段】ヒューズ配線4の下方には凸領域となるTEOS膜14の下敷きがあり、ヒューズ配線4はTEOS膜14を跨ぐように設けられ、ヒューズ配線4の上方にはTEOS膜14よりも小さい領域のヒューズ開口部13が設けられる。さらに、TEOS膜14の無い領域にてヒューズ配線14の両端に設けられたヒューズ端子15には第1金属配線7が電気的に接続されている。

(もっと読む)

半導体装置

【課題】ヒューズ開口部からの水分侵入による電特異常及び配線腐食を防止する半導体装置を提供する。

【解決手段】シリコン基板1上に絶縁膜2とゲート酸化膜3を設け、ゲート酸化膜2上の一部にヒューズ配線4の両端にヒューズ端子15を有するヒューズを設ける。ヒューズを構成するヒューズ配線4の上方には酸化膜5を介して窒化膜14が形成された凸領域があり、ヒューズ端子15は第1金属配線7と電気的に接続している。

(もっと読む)

半導体集積回路装置

【課題】過電流に対して内部回路を保護する半導体集積回路装置を提供することを目的としている。

【解決手段】多層配線構造を有する半導体集積回路装置であって、半導体集積回路装置の内部にある内部回路と半導体集積回路装置の外部にある外部回路とを接続するために半導体集積回路装置の内部に設けられたパッドパターンにおいて、第1の配線層と、第1の配線層が形成されている層とは別の層に形成されている第2の配線層と、第1の配線層と第2の配線層を接続するビアと、を備え、第2の配線層にヒューズパターンが形成されており、ヒューズパターンを経由して内部回路と外部回路とを電気的に接続する。

(もっと読む)

半導体装置及びその製造方法

【課題】トリミングや冗長に用いられるヒューズを有する半導体装置に関し、安定且つ確実に溶断しうるヒューズを有する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上に、第1の絶縁膜を形成し、第1の絶縁膜上に、ヒューズを形成し、ヒューズが形成された半導体基板上に、第1の絶縁膜に接して第2の絶縁膜を形成し、ヒューズ上の第2の絶縁膜に、開口部を形成し、第2の絶縁膜上及び開口部内に第3の絶縁膜を形成する。

(もっと読む)

鍵格納回路、半導体集積回路、及びシステム

【課題】格納された鍵の値の推測を困難にすることができる、鍵格納回路、半導体集積回路、及びシステムを提供する。

【解決手段】LSI10に搭載された鍵格納ブロック20は、k個のヒューズメモリセル30を有するヒューズブロック22と、鍵生成回路24と、を備えており、ヒューズブロック22からは予め実装されているビット長kの固定出力値fout[k−1:0]が出力される。鍵生成回路24は、レジスタ及び復号器を含んで構成されており、復号器は、演算処理により、固定出力値fout[k−1:0]と、レジスタの出力値と、からビット長n(n>k)の鍵key[n−1:0]を生成して出力する。

(もっと読む)

半導体集積回路装置

【課題】過電圧がLSIの電源端子に印加されたことを確認できるようにする。

【解決手段】半導体集積回路装置(10)は、内部回路(11)と、上記内部回路に電源電圧を供給するための電源端子(15,16)とを含む。このとき、上記内部回路の電源電圧として想定されるレベルを越える電圧(過電圧)が上記電源端子に印加された事実を記録するための過電圧印加情報記録回路(12)を設ける。過電圧印加情報記録回路には、過電圧が上記電源端子に印加された事実が記録されているため、それに基づいて、過電圧がLSIの電源端子に印加されたことを確認することができる。

(もっと読む)

半導体ダイ上にフィーチャをめっきするためのヒューズバス

【課題】半導体ダイ上に相互接続部又はボンドパッドなどのフィーチャ構造を電気めっきする方法を提供する。

【解決手段】方法は半導体基板の上方に複数のヒューズ(208)を形成する工程と、半導体基板の上方の複数の相互接続層(400〜408)と、該複数の相互接続層の上面の複数の相互接続パッド(502)とを形成する工程と、を含む。シールリング(202)が、半導体基板(302)と、前記複数の相互接続パッド(502)と、前記複数のヒューズ(208,320)とに形成された能動回路を包囲する。各ヒューズ(208,320)は、対応する相互接続パッド(502)とシールリング(202)とに電気的に接続される。各ヒューズ(208)が導通状態にあるとき、該ヒューズは対応する相互接続パッド(502)をシールリング(202)に電気的に接続する。

(もっと読む)

半導体装置およびその製造方法

【課題】トリミングヒューズの上の絶縁膜が、トリミングヒューズの機能を高めるために適正な状態を維持することが可能な半導体装置を提供する。

【解決手段】表面を有する絶縁膜III上のヒューズ配線F1と、ヒューズ配線F1上の層間絶縁層II1,II2,PIと、層間絶縁層II1,II2,PIの内部に位置する、ヒューズ配線F1と平面視において重ならない領域に形成された電極部PDとを備える。上記ヒューズ配線F1の真上のうち少なくとも一部の第1の領域において、層間絶縁層II1,II2,PIの厚みが、第1の領域以外の第2の領域における層間絶縁層II1,II2,PIの厚みより薄くなるようにトリミング開口部LTCが形成される。トリミング開口部LTCの内側において側壁および底面の少なくとも一部を覆うアルミニウム薄膜部SALを備える。アルミニウム薄膜部SALは、側壁の少なくとも一部から、底面より上側において上記表面に沿う方向に連なる。

(もっと読む)

ヒューズ回路及びトリミング良否判定方法

【課題】ヒューズ開口部の端部に必ず切断すべきヒューズを配設することにより、レーザー照射後のその切断/未切断をもって、端部のポリイミド膜の膜厚の良否を容易に判定する。

【解決手段】ヒューズ回路は、ヒューズ開口部FAの、ポリイミド膜の厚さが不本意に厚く残りやすい端部に配設された2つの切断確認用ヒューズ1a,1bと、ポリイミド膜の厚さ変動が端部に比べ少ない領域RAに配設された複数の実使用ヒューズ7a〜7dと、2つの切断確認用ヒューズ1a,1bからの信号を入力して当該ヒューズ1a,1bが確実に切断されているかを判定するヒューズ未切断判定回路2と、を備えている。なお、ヒューズ未切断判定回路2は、更にテストモード信号を入力すると共に、出力回路(例えばDQ回路)に判定結果を出力している。

(もっと読む)

半導体装置

【課題】回路規模が増大化する。

【解決手段】抵抗値が順に小さい値となって直列接続される複数のヒューズを備えるヒューズ部と、前記ヒューズ部の複数のヒューズのそれぞれ一端と、第1の電源電圧との間に接続される複数の選択スイッチと、前記第1の電源電圧から所定の電位差を有するヒューズ溶断用電圧を、前記ヒューズ部の最も小さい抵抗値のヒューズ側に出力するヒューズ溶融電圧出力回路と、ヒューズ溶断時に、前記ヒューズ溶融電圧出力回路が前記ヒューズ溶断用電圧を出力し、前記ヒューズ部の最も大きい抵抗値のヒューズに接続される選択スイッチから最も小さい抵抗値のヒューズに接続される選択スイッチまでを順に導通させる制御回路と、を備える半導体装置。

(もっと読む)

1 - 20 / 497

[ Back to top ]