Fターム[5F038DF11]の内容

半導体集積回路 (75,215) | 集積回路機能及び回路ブロック構成 (8,544) | 複数機能、回路ブロックの搭載、接続 (1,821)

Fターム[5F038DF11]の下位に属するFターム

アナログ、デジタル混載 (397)

回路ブロック配列(チップ上の配置に無関係) (191)

機能回路切換用構成 (929)

Fターム[5F038DF11]に分類される特許

1 - 20 / 304

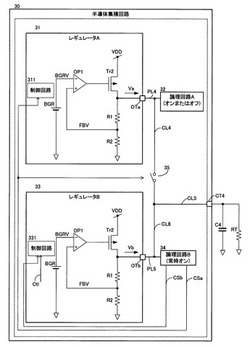

半導体集積回路

【課題】本発明の目的は,論理回路に電源電圧を供給するレギュレータを有する半導体集積回路において,C端子の数を削減する。

【解決手段】

半導体集積回路30は,第1,第2の出力端OTa,OTbと,外部容量C4に接続する外部接続端子CT4との間に設けられたスイッチ回路35を有し,

スイッチ回路35の一端は第1の出力端OTaに接続され,スイッチ回路35の他端は外部接続端子CT4および第2の出力端OTbに接続され,

スイッチ回路35は,第1のレギュレータA31が第1の電源電圧Vaを第1の論理回路A32に対して供給する期間はオンし,第1のレギュレータA31が第1の論理回路A32に対する電源電圧供給を停止する期間はオフする。

(もっと読む)

スキャン・チェーン用動的クロック領域バイパス

【課題】スキャン・テスト回路およびスキャン・テスト回路を使用して試験を受けるさらなる回路を備える集積回路を提供すること。

【解決手段】スキャン・テスト回路は、それぞれ別個のクロック領域に関連した複数のサブチェーンを有する少なくとも1つのスキャン・チェーン、および1つまたは複数のサブチェーンを選択的にバイパスするように構成されたクロック領域バイパス回路を備える。スキャン・チェーンは、スキャン・シフト・モードの動作において、サブチェーンを全部よりは少なく含む直列シフト・レジスタを形成するように構成可能であり、サブチェーンの少なくとも残りの1つが、スキャン・シフト・モードにおいて直列シフト・レジスタの部分でないように、クロック領域バイパス回路によりバイパスされる。特定のクロック領域に関連するスキャン・チェーンの部分を選択的にバイパスすることにより、クロック領域バイパス回路は、スキャン・テスト期間の試験時間と電力消費を減らす役割を果たす。

(もっと読む)

半導体装置

【課題】無線通信により交信可能な半導体装置において、個体識別子を容易に付けることができるようにする。

【解決手段】薄膜トランジスタ119と、薄膜トランジスタ上に第1の層間絶縁膜156と、第1の層間絶縁膜上の、ソース領域またはドレイン領域の一方に電気的に接続される第1の電極114と、ソース領域またはドレイン領域の他方に電気的に接続される第2の電極110と、第1の層間絶縁膜、第1の電極、及び第2の電極上に形成された第2の層間絶縁膜135と、第2の層間絶縁膜上の、第1の電極または第2の電極の一方に電気的に接続される第1の配線177と、第2の層間絶縁膜上の、第1の電極または第2の電極の他方に電気的に接続されない第2の配線178とを有し、第2の配線と前記第1の電極または第2の電極の他方は、第2の層間絶縁膜中の分断領域169によって、電気的に接続されない半導体装置及びその作製方法に関するものである。

(もっと読む)

信号処理回路及びその駆動方法

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる信号処理回路の提供する。

【解決手段】入力された信号の位相を反転させて出力する論理素子を2つ(第1の位相反転素子及び第2の位相反転素子)と、第1の選択トランジスタと、第2の選択トランジスタと、を有する記憶素子であって、酸化物半導体層にチャネルが形成されるトランジスタと容量素子との組を2つ(第1のトランジスタと第1の容量素子との組、及び第2のトランジスタと第2の容量素子との組)有する。そして、信号処理回路が有する記憶装置に上記記憶素子を用いる。例えば、信号処理回路が有するレジスタ、キャッシュメモリ等の記憶装置に上記記憶素子を用いる。

(もっと読む)

半導体集積回路

【課題】突入電流が周辺の回路へ及ぼす影響を低減しつつ、停止状態にある回路を短時間に動作状態とすることが可能な半導体集積回路を提供することである。

【解決手段】本発明にかかる半導体集積回路1は、領域PD1と、制御回路25と、回路26と、を備える。領域PD1には、電源線VDDと電源線VSDとの間にそれぞれ接続されたスイッチ21_1、22_1、23_1と、電源線VSDと電源線VSSとの間に接続された回路35と、が配置されている。回路26は、電源線VDDおよび電源線VSSから電源が供給され、回路35よりも最低動作電圧が高い回路である。スイッチ22_1はスイッチ21_1よりもオン抵抗が低い。スイッチ22_1は領域PD1のうち回路26と最も離れた頂点の近傍に配置されている。

(もっと読む)

半導体試験装置及びそのテスト方法

【課題】メモリのテスト時の消費電流を抑え、メモリテスト時の周波数を高速化する。

【解決手段】制御回路103は、第1及び第2のテストパタンジェネレータ104、105によるテストがともにライトの場合、一方のテストパタンジェネレータによるテストシーケンスの実行を許可し、他方のテストパタンジェネレータに対してテストシーケンスの実行を不許可とし、一方のテストパタンジェネレータからメモリグループ101、102の対応する一方のグループに対してライトのテストパタンを出力し、他方のグループに対するライトの実行を、一方のグループのライトのテストサイクル単位で時間的にずらし、一方のテストパタンジェネレータによる一方のグループのライトの終了後、他方のテストパタンジェネレータによるテストシーケンスの実行を許可し、他方のテストパタンジェネレータから対応する他方のグループに対するライトのテストパタンを出力する。

(もっと読む)

半導体装置

【課題】電源制御領域を電源遮断状態から電源供給状態に切り換えた際に生じる突入電流と電源ノイズを低減した半導体装置を提供する。

【解決手段】第1、第2のスイッチセルSWa、SWbと、を有し、第1のスイッチセルSWaは、制御信号CNTに応じてグローバル電源配線GVDDからローカル電源配線LVDDへの電源電圧の供給を開始する第1のスイッチトランジスタ11と、制御信号CNTを伝達する第1の信号伝達部と、を有し、第2のスイッチセルSWbは、制御信号CNTの論理レベルに応じてグローバル電源配線GVDDからローカル電源配線LVDDへの電源電圧の供給を開始する第2のスイッチトランジスタ21と、ローカル電源配線LVDDの電圧値が閾値電圧に達するまでの期間、制御信号CNTの後段回路への伝達を遮断する第2の信号伝達部と、を有する。

(もっと読む)

半導体装置

【課題】実行するプログラムの種類又は発生する異常の種類などの、動作開始後の状況に合わせて外部端子の状態をプログラマブルに設定する。

【解決手段】プログラム処理回路によるデータ処理状態、プログラム処理回路が実行するプログラム若しくはデータ処理の種類、あるいはデータ処理による異常の種別毎に、異常発生時の入出力端子の端子状態を制御する制御データを予め不揮発性記憶部(140)に保存する。プログラム実行前若しくはプログラムの実行時に逐次に不揮発性記憶部に制御データを特定する検索キーを設定し、異常が発生した場合は、当該検索キーに基づいて参照された制御データに従って、入出力端子の状態をプルアップ、プルダウン、ハイインピーダンス又は前値保持の状態に設定する。

(もっと読む)

半導体集積回路装置

【課題】低電源電圧が入力された際に昇圧動作を行い、高電源電圧が入力された際に該高電源電圧と同じ程度の電圧を出力する。

【解決手段】インバータ11にLo信号が入力されるとインバータ12〜14の出力がLo信号となる。そして、トランジスタ15がONし、静電容量16、ダイオード17の逆バイアス容量に電源電圧VCC2の電荷が充電され、ノードXの電位は電源電圧VCC2となる。続いて、インバータ11にHi信号が入力されると、トランジスタ14aがONし、ノードXとノードX’との電位が略同じとなる。インバータ13を構成するPチャネルMOSトランジスタがONし、静電容量16の容量カップリングによりノードX,X’が昇圧されて出力される。ここで、ダイオード17は、電源電圧VCC1が高電圧領域の電圧レベルの際には、電源電圧VCC1の電圧レベルがダイオード17を介して直流的に出力される。

(もっと読む)

I/O積層体を含むシステム及びこのシステムを製造する方法

【課題】入出力(I/O)積層体を含むシステムを提供する。

【解決手段】入出力(I/O)積層体を含むシステム及びこのシステムを製造する方法が記述されている。一実装において、本方法は、I/O素子を含むと共に論理素子を含まないI/Oダイを積層するステップを有する。又、一実装において、本方法は、I/Oダイに対して集積回路ダイを積層するステップを更に含む。集積回路は、論理素子を含み、且つ、I/O素子を含まない。集積回路ダイからI/Oダイを分離することにより、それぞれのダイの独立的な開発や従来のダイのものとの比較におけるI/OダイのI/O基板上のI/O素子用の相対的に大きな空間などの様々な利益が得られる。空間の増大により、多数の論理素子を集積回路ダイの基板の同一の表面積内に収容する集積回路ダイの新しいプロセス世代が可能となる。

(もっと読む)

半導体集積回路

【課題】回路モジュール毎に電力供給のオン/オフを切り換える電源制御機能を有する半導体集積回路であって、回路規模及び配線規模の増加を極力抑えながら、ある回路モジュールへの電力供給のオン/オフを切り換える際に発生するインラッシュ電流による影響を根本的に除去する。

【解決手段】電源制御機能を有する半導体集積回路1は、回路モジュール11,12,21,22と電源制御回路3とを含む。回路モジュール21,22への電力供給は、電源制御回路3の制御下でオン/オフ制御される。電源制御回路3は、1つの回路モジュールへの電力供給のオン/オフを切り換えるとき、他の回路モジュールに、当該他の回路モジュールの内部におけるデータ転送を停止させるように制御する。

(もっと読む)

集積回路および中継基板

【課題】本発明は、マイクロ波帯やミリ波帯において、1つの集積回路で複数の機能を実現する集積回路と、その集積回路が表面実装される中継基板とに関し、特性の劣化の原因となる広帯域設計をすることなく、多様に異なる帯域に柔軟に対応可能とすることを目的とする。

【解決手段】基板上に個別に形成された複数の回路と、前記基板上で前記複数の回路に隔たって形成され、前記複数の回路の何れにも接続され得る特定の回路とを備え、前記特定の回路と前記複数の回路とは、表面実装型の中継基板との突起電極を介する接続に供されるパッドを有する。

(もっと読む)

起動回路、スイッチング電源用IC及びスイッチング電源装置

【課題】起動回路を構成するJFETのピンチオフ維持のために生じる電力損失を低減できる起動回路、スイッチング電源用IC及びスイッチング電源装置を提供する。

【解決手段】起動電源(電源コンデンサ)と平滑コンデンサによる補助電源との間に接続され、起動電源による起動電流を平滑コンデンサに流すMOSFETと、ドレイン端子がMOSFETのドレイン端子に接続され、ソース端子が抵抗を介してMOSFETのゲート端子に接続されたJFETと、起動時にJFETのピンチオフ電圧が第1基準電圧値となるように制御し、起動後にJFETのピンチオフ電圧が第1基準電圧値未満の値である第2基準電圧値となるように制御するピンチオフ電圧制御部(可変電圧源)とを備える。

(もっと読む)

半導体装置

【課題】回路面積の増大を抑え、回路ブロックに電源供給するための複数の電源スイッチをオンするための時間間隔を適切に制御できるようにする。

【解決手段】回路ブロックに対する電源供給を管理する電源管理ユニット11と、回路ブロックA12への電源供給を制御する複数の電源スイッチPSWAと、回路ブロックAに供給する電源で動作し、その電位に応じた遅延を生成する遅延生成器13とを備え、電源スイッチは、電源供給を行うためにオン状態に制御されるときに、電源管理ユニット及び遅延生成器13の出力に基づいて回路ブロックAに供給される電源電位に応じた時間間隔で順次オン状態にするようにして、電源スイッチをオンするための時間間隔を回路ブロックAに供給される電源電位に応じて自動的に調整して電源供給を行う。

(もっと読む)

未知の半導体装置の機能の非破壊的な決定

【課題】外部放射線に対して応答する接合を分析することを通して機能を推測することによる、集積回路の非破壊的なリバースエンジニアリングのためのシステム及び技術を提供する。

【解決手段】少なくとも1つの電源と電気的に導通している複数の半導体接合を含む半導体装置の機能を決定するための以下を含む方法。

・半導体装置の表面を照射すること;

・照射に応答する複数の半導体接合のうち少なくとも幾つかのレイアウトを決定すること;

・決定されたレイアウト内で、複数の半導体接合の少なくとも幾つかのグルーピングを同定し、各ブルーピングはそれぞれの機能セルを表すこと;

・複数の外部アクセス可能な接点のうち少なくとも1つへの刺激を変化させること;及び

・前記変化した刺激に応答して複数の相互接続された機能セルの1つ以上の接続を推測すること。

(もっと読む)

半導体集積回路装置およびテストモード設定方法

【課題】簡易な回路で、よりセキュリティ性を向上させる。

【解決手段】半導体集積回路装置(100)は、複数の機能ブロック(125−127)と、取り込み部(131)と、検出部(132)と、判定部(150)とを具備し、動作パターンが所定の規則に従って変化したときにテストモードに移行する。複数の機能ブロック(125−127)は、制御装置(200)からの指示に応答して動作する。取り込み部(131)は、複数の機能ブロック(125−127)のそれぞれの動作状態を示す信号を取り込む。検出部(132)は、複数の機能ブロック(125−127)のうちの少なくとも1つの機能ブロックの動作状態の変化を検出する。判定部(150)は、取り込まれた動作状態を示す信号によって示される動作パターンが所定の規則に従って変化するか否かを判定する。

(もっと読む)

半導体装置

【課題】交流リークが電圧検出回路に流れるのを防ぐことができる半導体装置を提供する。

【解決手段】半導体装置は、アンテナ回路102と、共振周波数調整回路126と、電圧検出回路と、第1の容量素子と、を有する。共振周波数調整回路126は、一方の端子がアンテナ回路102の第1の端子と電気的に接続された第2の容量素子と、第1の端子が第2の容量素子の他方の端子と電気的に接続され、第2の端子がアンテナ回路102の第2の端子と電気的に接続され、ゲートが第1の容量素子及び電圧検出回路と電気的に接続されたトランジスタと、を有する。

(もっと読む)

半導体集積回路装置

【課題】内部回路の電源電圧の安定性を確保しつつ、効率を改善したオンチップ電源回路を搭載した半導体集積回路装置を提供する。

【解決手段】半導体集積回路装置は、電源ノードと電源ライン38との間に接続される上層負荷30と、電源ライン40と接地ノードとの間に接続される下層負荷32と、電源ライン38を所定電圧に維持するためのVDC66と、電源ライン40を所定電圧に維持するためのVDC52と、電源ライン38,40接続状態と、電源ライン38とVDC66との接続状態と、電源ライン40とVDC52との接続状態とを変更可能な接続回路33とを備える。

(もっと読む)

半導体装置

【課題】プロセスを簡素化し低コスト化を実現するとともに、さらに、システムを簡素化しノイズ対策を可能にするMEMSレゾネータ及びMEMSレゾネータの製造方法を提供する。

【解決手段】MEMSレゾネータの製造方法は、基板10上に形成された半導体デバイスとMEMS構造体部4とを有するMEMSレゾネータ2の製造方法であって、半導体デバイスは、上部電極30と下部電極26とを有するONOキャパシタ部6と、CMOS回路部8と、を含み、ONOキャパシタ部6の下部電極26を、第1シリコン層26を用いて、形成する。MEMS構造体部4の下部構造体16とONOキャパシタ部6の上部電極30とを、第2シリコン層52を用いて、形成する。及び、MEMS構造体部4の上部構造体18とCMOS回路部8のゲート電極34とを、第3シリコン層54を用いて、形成する。

(もっと読む)

半導体集積回路

【課題】低消費電力で動作し、かつ、端子数を減らすことが可能な半導体集積回路を提供する。

【解決手段】半導体集積回路は、第1の回路と、第2の回路と、信号伝播制御回路と、を備える。第2の回路は、前記第1の回路の電源端子とは独立の電源端子を有する。信号伝播制御回路は、前記第2の回路に電源が投入されてから所定期間、所定の固定値を前記第2の回路へ入力し、前記所定期間経過後、前記第1の回路からの出力信号および前記所定の固定値のいずれを前記第2の回路へ入力するかを制御する。

(もっと読む)

1 - 20 / 304

[ Back to top ]