Fターム[5F038DF14]の内容

半導体集積回路 (75,215) | 集積回路機能及び回路ブロック構成 (8,544) | 複数機能、回路ブロックの搭載、接続 (1,821) | 回路ブロック配列(チップ上の配置に無関係) (191)

Fターム[5F038DF14]に分類される特許

1 - 20 / 191

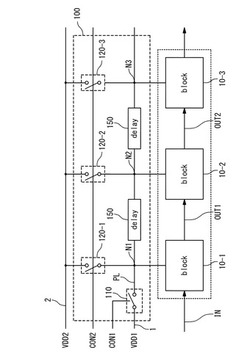

半導体装置

【課題】半導体装置の回路ブロックへの電力供給復帰時に、無駄な充放電を削減すること。

【解決手段】半導体装置は、第1電源電圧を供給する第1電源線と、第1電源電圧よりも高い第2電源電圧を供給する第2電源線と、前段回路ブロックと、前段回路ブロックの出力信号に基づいて動作する後段回路ブロックと、前段回路ブロック及び後段回路ブロックに対する第1電源電圧及び第2電源電圧の供給を制御する電力供給制御回路と、を備える。電力供給制御回路は、後段回路ブロックへの第1電源電圧の供給開始タイミングを前段回路ブロックへの第1電源電圧の供給開始タイミングよりも遅延させる。更に、電力供給制御回路は、前段回路ブロック及び後段回路ブロックに第1電源電圧が供給された後に、第2電源電圧を前段回路ブロックと後段回路ブロックの両方に供給する。

(もっと読む)

半導体装置

【課題】直流電源配線に電流が流れたか否かを検出可能な回路を備えた半導体装置を提供する。

【解決手段】半導体装置において、駆動回路BLDU,BLDD,BLBDU,BLBDDは、電流磁界またはスピン注入によってトンネル磁気抵抗素子TMR,TMRBを第1の磁化状態に初期設定するために、制御信号線BL,BLBに直流電流を流す。電源配線DLは、トンネル磁気抵抗素子TMR,TMRBに近接して設けられる。ここで、トンネル磁気抵抗素子TMR,TMRBは、電源配線DLに直流電流が流れるときに生じる電流磁界によって第2の磁化状態に変化する。センスアンプ10は、トンネル磁気抵抗素子TMR,TMRBが第1の磁化状態から第2の磁化状態に変化したか否かを判定するために、制御信号線BL,BLBを介してトンネル磁気抵抗素子TMR,TMRBに流れる電流を検出する。

(もっと読む)

半導体装置

【課題】寿命が長い半導体装置を提供する。

【解決手段】このLSIは、2つのCPU1,2と、CPU1,2のうちのいずれか1つのCPUを示す論理レベルのデータ信号が書き込まれた記憶回路4と、リセット信号REが非活性化レベルにされてLSIのリセットが解除された場合、記憶回路4の記憶データの論理レベルに対応するCPUのみに電源電圧を供給するとともに、記憶回路4の記憶データを現在の論理レベルと異なる論理レベルのデータ信号に書き換える制御回路3,5とを備える。したがって、故障の検知や、厳密なタイミング制御を必要とせずに、CPUの長寿命化を図ることができる。

(もっと読む)

半導体装置

【課題】積層チップシステムにおいて、各チップのIO回路の大きさを、そのドライブ能力やESD耐性能力を維持した上で、従来のサイズから縮小し、積層システムでは積層数に応じてIO数を変化させることができる半導体装置を提供する。

【解決手段】積層チップシステムにおいて、各チップは、各IO用の貫通ビア接続用パッド201に接続するIO回路202、スイッチ回路206にてIOチャネル207を構成し、このIOチャネル207を最大積層予定数のIOチャネル分まとめて接続してIOグループを構成し、このIOグループを1個以上持つ。各IO用の貫通ビア接続用パッド201は、貫通ビアにて別層のチップの同一位置のIO端子と接続される。インターポーザにおいては、実際の積層数が最大積層予定数に満たない場合はインターポーザ上で隣接するIOグループ内のIO用の接続用パッドが導体で接続されている。

(もっと読む)

鍵格納回路、半導体集積回路、及びシステム

【課題】格納された鍵の値の推測を困難にすることができる、鍵格納回路、半導体集積回路、及びシステムを提供する。

【解決手段】LSI10に搭載された鍵格納ブロック20は、k個のヒューズメモリセル30を有するヒューズブロック22と、鍵生成回路24と、を備えており、ヒューズブロック22からは予め実装されているビット長kの固定出力値fout[k−1:0]が出力される。鍵生成回路24は、レジスタ及び復号器を含んで構成されており、復号器は、演算処理により、固定出力値fout[k−1:0]と、レジスタの出力値と、からビット長n(n>k)の鍵key[n−1:0]を生成して出力する。

(もっと読む)

半導体集積回路装置

【課題】レベル変換回路のレイアウト面積の縮小を図る。

【解決手段】半導体集積回路装置(10)は、レベル変換回路(14)と、D/A変換回路(12)とを備える。このとき、パラレル形式のデジタル信号をシリアル形式に変換して上記レベル変換回路に供給するためのパラレル・シリアル変換回路(15)と、上記レベル変換回路の出力をパラレル形式のデジタル信号に変換して上記D/A変換回路に供給するためのシリアル・パラレル変換回路(13)とを設ける。上記レベル変換回路は、シリアル形式のデジタル信号に対応するレベル変換機能を備えていれば良く、パラレル形式のデジタル信号に対応させる場合に比べて、レベル変換回路のレイアウト面積を縮小することができる。

(もっと読む)

半導体集積回路装置

【課題】電源遮断領域の信号配線の自由度を低下させないで、電源遮断用スイッチから電源遮断領域に至る電圧伝達経路における電圧降下を抑える。

【解決手段】半導体集積回路装置(80)は、電源遮断用スイッチ(90)と電源遮断領域(763)とが形成された半導体チップ(22)とを含む。半導体チップは基板(21)に結合される。上記電源遮断領域の外側に上記電源遮断用スイッチを配置することで、電源遮断領域内の配線チャネル数の低減を回避する。そして上記基板には、上記半導体チップ内から上記電源遮断用スイッチを介して上記半導体チップの外に伝達された電源電圧を再び上記半導体チップ内に伝達して上記電源遮断領域へ給電するための基板側給電路(30)を形成することで、上記電源遮断用スイッチと上記電源遮断領域との間の電圧降下を抑える。

(もっと読む)

半導体装置

【課題】複数の回路ブロックの特性を正確に一致させる。

【解決手段】例えば、端子31A,31Bと、これら端子間に設けられた回路110A,110Bを備える。回路110Aは端子31Aに接続され、端子31Aから端子31Bへ向かって配置されたセル120A,130A,140Aを含む。回路110Bは端子31Bに接続され、端子31Bから端子31Aへ向かって配置されたセル120B,130B,140Bを含む。セル120A,120Bのレイアウトは、形状、サイズ及び向きがトランジスタレベルで同一である。セル130A,130B及びセル140A,140Bのレイアウトは、形状及びサイズが同一であり、トランジスタの向きが180°相違している。これにより各セルを対称配置しつつ、センシティブなセル120A,120Bにおいては電流方向の違いによる特性差が生じない。

(もっと読む)

半導体集積回路及び半導体集積回路の動作制御方法

【課題】温度が高くなりすぎたりあるいは低くなりすぎたりする発振状態となって、半導体集積回路が誤動作、動作停止等することを防止する。

【解決手段】実施形態によれば、半導体集積回路1は、回路部の温度又は動作速度に基づいて、温度が安定するように、回路部の制御パラメータを調整して、フィードバック制御を実行する制御部と、温度の時系列データである第1の履歴データと、制御パラメータの時系列データである第2の履歴データとを含む履歴データを格納する履歴レジスタ17と、履歴データからフィードバック制御の有効性を判定する有効性判定部24とを有する。

(もっと読む)

半導体装置及びデータ取込方法

【課題】電源ノイズによるデジタル信号の取込エラーを低減すること。

【解決手段】パルス制御信号に応じてスイッチング動作を行なうスイッチング回路120と、デジタル信号を取り込むデジタル信号保持回路111と、を備え、デジタル信号保持回路111は、スイッチング動作による電源ノイズの発生期間におけるデジタル信号の取り込みを回避するためのマスク信号をパルス制御信号から生成するマスク信号生成回路114を含み、電源ノイズの発生期間にはデジタル信号を取り込まず、電源ノイズの非発生期間に前記デジタル信号を取り込む半導体装置。

(もっと読む)

半導体集積回路のレイアウト設計方法

【課題】LSIのレイアウト設計において、TAT(Turn Around Time)を増加させることなくタイミング収束を実現する。

【解決手段】LSIのレイアウト設計方法は、レイアウト対象の集積回路のネットリストに基づいて、前記集積回路をクロックドメインに分けることでクロックドメイン回路集合体に区分する工程と、前記クロックドメイン回路集合体の各々に対するタイミング制約を作成する工程と、所定の基準に基づいて前記クロックドメイン回路集合体間の配置順序を決定する工程と、前記クロックドメイン回路集合体を前記配置順序に従って配置し配線することにより前記集積回路のレイアウトを作成する工程とを備える。レイアウト設計後のタイミング収束のTATを短縮することが可能となる。

(もっと読む)

半導体回路

【課題】レイアウトの複雑化や面積増大を伴わずにオフリーク電流の抑制と高速化を両立した半導体回路の実現。

【解決手段】通常動作モードと、少なくとも一部の回路に供給する信号を固定して、少なくとも一部の回路の状態を固定する低消費電力モードと、を備え、少なくとも一部の回路20において、低消費電力モード時にオン状態になるトランジスタPT1,PT3,NT2,NT4の閾値電圧が、低消費電力モード時にオフ状態になるトランジスタPT2,PT4,NT1,NT3の閾値電圧より小さい。

(もっと読む)

半導体装置

【課題】広範囲、光分解能に周波数を可変することのできるクロック信号を生成する。

【解決手段】オペアンプAMP1は、正入力部と負入力部が等しい電圧となるようフィードバックがかかり、回路ノードfbckは、参照電圧VREFIに等しい電圧となる。デコーダDECは、制御信号CNT7,CNT6をデコードし、トランジスタT2〜T5のいずれか1つをオンさせる。この構成によって、回路ノードfbckが、参照電圧VREFIと同電位となるようフィードバック制御がかかるため、トランジスタT2〜T5のON抵抗を大幅に低減することができ、周波数精度の悪化を防止することができる。

(もっと読む)

半導体装置

【課題】複数の電圧レベルの電源電圧が供給される入出力バッファ回路に対して、従来よりも少ない電源配線スペースで十分な電源供給を可能にする。

【解決手段】半導体装置3において、入出力バッファ回路BFは電圧レベルの変換を行なう。第1の電源配線HVLは、入出力バッファ回路BFの第1の回路部分HCと接続され、第1の回路部分HCに第1の電源電圧VCC1を供給する。第2の電源配線LVLは、入出力バッファ回路BFの第2の回路部分LCと接続され、第2の回路部分LCに第2の電源電圧VCC2を供給する。複数のスイッチ部SWは、第3の電源配線SVLに沿った複数箇所にそれぞれ設けられる。複数のスイッチ部SWの各々は、内部回路10から出力された制御信号に応じて、第1および第2の電源配線HVL,LVLのうち選択された一方の電源配線と第3の電源配線SVLとを接続する。

(もっと読む)

半導体チップ、半導体装置及びLSI設計装置

【課題】チップコストの低下とチップ歩留りの向上とを同時に実現する。

【解決手段】実施形態に係わる半導体チップは、パッド領域11及び方形でないゲート領域12を備える第1のレイアウトL1と、第1のレイアウトL1を180°回転させた第2のレイアウトL2とを備える。第1及び第2のレイアウトL1,L2は、点対称かつ重なり合わずに結合されることによりチップレイアウトを構成する。チップレイアウトは、方形のチップ領域内に配置され、第1及び第2のレイアウトL1,L2は、それぞれ独立に動作するLSIを構成する。

(もっと読む)

2つのタイプの減結合コンデンサを備えた集積回路および方法

【課題】デュアル電圧パワーアイランドアーキテクチャにおいて、低いオフ状態リークを実現する事が可能な最適な減結合キャパシタンスのための方法およびシステムを提供する。

【解決手段】チップの低電圧領域において、誘電体膜厚の異なる2つの異なるタイプのコンデンサが使用される。膜厚の薄いコンデンサは常時オン状態の領域で使用され、膜厚の厚いコンデンサーは条件付きで起動される領域で使用される。これによって低いオフ状態リークをで減結合コンデンサーを使用できる。

(もっと読む)

半導体集積回路装置

【課題】バイアス電流を配給する際のノイズ耐性を大幅に向上させる。

【解決手段】基準バイアス電流回路11は、基準バイアス電流Ipと該基準バイアス電流Ipと電流の極性が逆となる基準バイアス電流Inとを生成し、2本の配線を1ペアとしたバイアス電流用配線H1を介してバイアス電流回路2aに供給する。ペアの配線のうち、一方の配線は他方の線の近傍に平行してレイアウトされており、これら配線の配線長が略同じとしている。バイアス電流回路2aでは、基準バイアス電流Ipを反転させ、基準バイアス電流Inに加算した後、必要なバイアス電流となるように調整し、バイアス電流を生成する。

(もっと読む)

モータ制御用半導体装置

【課題】モータ制御用半導体装置に対するコンタクト用ピンからの影響を低減する

【解決手段】ホール素子102からの出力のオフセット電圧を取り除くオフセットキャンセル回路104に含まれるオシレータ回路12と、オフセットキャンセル回路104からの出力信号を受けて、当該出力信号と基準信号とを比較して比較信号を生成して出力するコンパレータ回路106と、モータを駆動するための駆動信号を生成して出力する出力回路110と、モータの制御に関係しないテスト回路112と、を有し、オシレータ回路12の回路パターン上、コンパレータ回路106の回路パターン上、及び、テスト回路112の回路パターン上のいずれか1つに重なるようにパルス幅変調信号の入出力パッドP1を形成する。

(もっと読む)

半導体装置

【課題】低電位領域と高電位の配線が交差することの無い優れた耐圧性能を示す半導体装置を提供することを課題とする。

【解決手段】本発明の半導体装置は、ロジック回路(501)と、ロジック回路からの制御信号に従い低電位側パワー素子を駆動する低電位側駆動回路(502)と、ロジック回路からの制御信号がレベルシフト回路を介して入力され、高電位側パワー素子(506)を駆動する高電位側駆動回路(505)と、複数に重なったトレンチ分離領域により、前記高電位側パワー素子を含む高電位島を分離する多重トレンチ分離領域(508)と、を有する。

(もっと読む)

内部回路と静電保護回路を具備する半導体集積回路

【課題】電源電圧の分離数や接地電圧の分離数の増大により静電保護回路の回路数もしくは静電保護素子数の増大を軽減する。

【解決手段】半導体集積回路1は、第1と第2と第3の動作電圧供給端子21、22、23と、第1と第2と第3の内部回路11、12、13と、第1と第2と第3の静電保護回路41、42、43と、接続中Cdとを具備する。第1と第2と第3の内部回路11、12、13は、第1と第2と第3の動作電圧供給端子21、22、23の第1と第2と第3の動作電圧でそれぞれ動作する。第1と第2と第3の静電保護回路41、42、43は、第1と第2と第3の動作電圧供給端子21、22、23と接続中点Cdの間にそれぞれ接続される。すなわち、第1と第2と第3の静電保護回路41、42、43は、従来のΔ(デルタ)接続ではなく、接続中点Cdに関してY(スター)接続される。

(もっと読む)

1 - 20 / 191

[ Back to top ]