Fターム[5F064FF60]の内容

ICの設計・製造(配線設計等) (42,086) | 切り換え、選択 (3,709) | その他 (20)

Fターム[5F064FF60]に分類される特許

1 - 20 / 20

半導体装置及びトリミング方法

【課題】ヒューズ素子の列数増に伴うトリミング時間の伸長を抑制する。

【解決手段】x方向に延伸する接地配線Gと、接地配線のy方向の一方側に設けられたヒューズ素子領域Aにx方向に沿って3列に並べて配置され、かつそれぞれの一端が接地配線Gに共通に接続される複数のヒューズ素子と、ヒューズ素子領域Aを挟んで接地配線Gの反対側に設けられ、ヒューズ素子領域Aに配置された複数のヒューズ素子それぞれの他端と接続される救済回路とを備え、上記複数のヒューズ素子は、それぞれ1つの欠陥選択線を示すアドレス情報を記憶する複数のヒューズ素子グループに所定個ずつグループ化され、同一のヒューズ素子グループに属する所定個のヒューズ素子は、同一列に配置されることを特徴とする

(もっと読む)

鍵格納回路、半導体集積回路、及びシステム

【課題】格納された鍵の値の推測を困難にすることができる、鍵格納回路、半導体集積回路、及びシステムを提供する。

【解決手段】LSI10に搭載された鍵格納ブロック20は、k個のヒューズメモリセル30を有するヒューズブロック22と、鍵生成回路24と、を備えており、ヒューズブロック22からは予め実装されているビット長kの固定出力値fout[k−1:0]が出力される。鍵生成回路24は、レジスタ及び復号器を含んで構成されており、復号器は、演算処理により、固定出力値fout[k−1:0]と、レジスタの出力値と、からビット長n(n>k)の鍵key[n−1:0]を生成して出力する。

(もっと読む)

半導体装置およびその製造方法

【課題】トリミングヒューズの上の絶縁膜が、トリミングヒューズの機能を高めるために適正な状態を維持することが可能な半導体装置を提供する。

【解決手段】表面を有する絶縁膜III上のヒューズ配線F1と、ヒューズ配線F1上の層間絶縁層II1,II2,PIと、層間絶縁層II1,II2,PIの内部に位置する、ヒューズ配線F1と平面視において重ならない領域に形成された電極部PDとを備える。上記ヒューズ配線F1の真上のうち少なくとも一部の第1の領域において、層間絶縁層II1,II2,PIの厚みが、第1の領域以外の第2の領域における層間絶縁層II1,II2,PIの厚みより薄くなるようにトリミング開口部LTCが形成される。トリミング開口部LTCの内側において側壁および底面の少なくとも一部を覆うアルミニウム薄膜部SALを備える。アルミニウム薄膜部SALは、側壁の少なくとも一部から、底面より上側において上記表面に沿う方向に連なる。

(もっと読む)

ヒューズ回路及びトリミング良否判定方法

【課題】ヒューズ開口部の端部に必ず切断すべきヒューズを配設することにより、レーザー照射後のその切断/未切断をもって、端部のポリイミド膜の膜厚の良否を容易に判定する。

【解決手段】ヒューズ回路は、ヒューズ開口部FAの、ポリイミド膜の厚さが不本意に厚く残りやすい端部に配設された2つの切断確認用ヒューズ1a,1bと、ポリイミド膜の厚さ変動が端部に比べ少ない領域RAに配設された複数の実使用ヒューズ7a〜7dと、2つの切断確認用ヒューズ1a,1bからの信号を入力して当該ヒューズ1a,1bが確実に切断されているかを判定するヒューズ未切断判定回路2と、を備えている。なお、ヒューズ未切断判定回路2は、更にテストモード信号を入力すると共に、出力回路(例えばDQ回路)に判定結果を出力している。

(もっと読む)

半導体装置

【課題】回路規模が増大化する。

【解決手段】抵抗値が順に小さい値となって直列接続される複数のヒューズを備えるヒューズ部と、前記ヒューズ部の複数のヒューズのそれぞれ一端と、第1の電源電圧との間に接続される複数の選択スイッチと、前記第1の電源電圧から所定の電位差を有するヒューズ溶断用電圧を、前記ヒューズ部の最も小さい抵抗値のヒューズ側に出力するヒューズ溶融電圧出力回路と、ヒューズ溶断時に、前記ヒューズ溶融電圧出力回路が前記ヒューズ溶断用電圧を出力し、前記ヒューズ部の最も大きい抵抗値のヒューズに接続される選択スイッチから最も小さい抵抗値のヒューズに接続される選択スイッチまでを順に導通させる制御回路と、を備える半導体装置。

(もっと読む)

半導体装置

【課題】占有面積の小さな直線状の電気ヒューズを有する半導体装置を提供する。

【解決手段】複数の突出部10fは、電気ヒューズ部10aの中央位置からずれた位置、より具体的には、ビア10dに近くかつビア10eから遠い位置に設けられている。また、複数の突出部20fは、電気ヒューズ部20aの中央位置からずれた位置、より具体的には、ビア20dから遠くかつビア20eに近い位置に設けられている。つまり、突出部10fおよび突出部20fは、ジグザグ状に配置されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】レイアウト面積の増大を抑制しつつ、容量を拡張することが可能な不揮発性半導体記憶装置を提供する。

【解決手段】メモリセルに複数のアンチヒューズ素子F1、F2を設け、各アンチヒューズ素子F1、F2の電界効果トランジスタのゲートを互いに接続することで、アンチヒューズ素子F1、F2の一端をノードAに共通に接続し、メモリセルを多値化する。

(もっと読む)

半導体装置の製造方法

【課題】ヒューズ(FUSE)を備えた半導体装置の信頼性を向上する。

【解決手段】半導体基板11の主面上に形成にされた多層配線を構成する層M1〜M6のうちの層M4に設けられた電気溶断型の救済用のヒューズ4aおよび試験用のヒューズ4bと、ヒューズ4aの近傍であって層M2および層M6に設けられた一対の導電板10aと、ヒューズ4bの近傍であって層M3および層M5に設けられた一対の導電板10bとから構成する。ヒューズ4bと導電板10bとの間が、ヒューズ4aと導電板10aとの間より近いものとする。

(もっと読む)

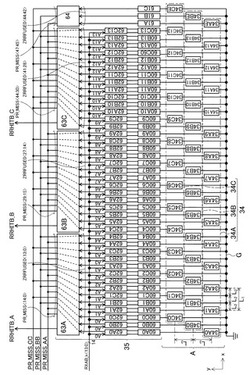

プログラマブル論理集積回路

【課題】 異なったLVTTL I/O規格に対して互換性を持つように集積回路の各I/Oを個別に再構成する回路を提供する。

【解決手段】 上述課題は1つのI/O電源電圧のみを用いて達成でき、この電圧は特定の用途に要求されるI/O電圧のうち最も高いものである。回路はI/Oセルの出力電圧を、適合されるべきLVTTL規格のVOHよりも高く最高VIHよりも低くなるように調節することによって動作する。I/Oセルは、I/O電源電圧とパッドの間に接続されるプルアップトランジスタと、該パッドの電圧と対応の規格に応じた基準電圧とを差動増幅する差動増幅器と、差動増幅器の出力信号と出力制御信号とにプルアップトランジスタを選択的にオン状態とするロジックゲートを備える。各I/Oセルは別個に再構成可能であるため、任意のI/Oを任意のLVTTL仕様に適合させることができる。

(もっと読む)

低電力多重状態電子ヒューズ(eヒューズ)をプログラミング及び再プログラミングするための回路構造体及び方法

【課題】 低電力多重状態の電子ヒューズをプログラミング及び再プログラミングするための回路構造体及び方法を提供する。

【解決手段】 eヒューズのプログラミング/再プログラミング回路の実施形態を開示する。一実施形態において、eヒューズ(150)は、長い低原子拡散抵抗導体層(120)の同じ端部に両側(121、122)上に配置された2つの短い高原子拡散抵抗導体層(110、130)を有する。電圧源(170)を用いて端子(第1の端子=170/161/110、第2の端子=170/162/130、第3の端子=170/163/導体層120の近位端123、及び第4の端子=170/164/導電層120の遠位端124)に印加する電圧の極性及び随意的に大きさを変化させて、長い導体層内の電子の2方向の流れを制御し、これにより長い導体層と短い導体層との界面(125、126)における開路及び/又は短絡の形成を制御する。このような開路及び/又は短絡の形成を用いて異なるプログラミング状態(11、01、10、00)を実現することができる。他の回路構造体の実施形態は、さらに多くのプログラミング状態を可能にするように、付加的な導体層及び付加的な端子を有するeヒューズ(650)を組み込む。さらに、関連したeヒューズのプログラミング及び再プログラミング方法の実施形態を開示する。

(もっと読む)

電気ヒューズ、半導体装置、および電気ヒューズの切断方法

【課題】ヒューズの切断状態を精度よく判定する。

【解決手段】電気ヒューズ101は、ポリシリコン層102と、ポリシリコン層102上に形成されたシリサイド層104と、シリサイド層104上に互いに間隔を隔てて配置された第1の金属コンタクト108および第2の金属コンタクト112とを含む。電気ヒューズ101は、切断後に、シリサイド層104が、第2の金属コンタクト112直下および第2の金属コンタクト112と第1の金属コンタクト108との間の領域に存在しない構成となる。

(もっと読む)

ヒューズ素子

【課題】微細化しても溶断位置の制御が容易なヒューズ素子を得ること。

【解決手段】半導体基板に形成された回路素子と、半導体基板上に形成された複数の層間絶縁膜と、複数の層間絶縁膜それぞれに設けられて層間接続された複数の配線とを有する半導体装置に設けられるヒューズ素子を構成するにあたり、半導体基板上に、または複数の層間絶縁膜IL1〜IL3のいずれかにヒューズ本体43を配置すると共に、複数の層間絶縁膜のいずれかに電気伝導には寄与しない複数のダミービア45a〜45dを金属材料により形成し、複数のダミービアの各々は、ヒューズ本体に一端を接続してヒューズ本体での長手方向の一方の端部と他方の端部とに分けて配置する。

(もっと読む)

ポリシリコンヒューズを有する半導体装置のトリミング方法

【課題】ポリシリコンヒューズを有する半導体装置の安定なトリミング(書き込み)方法を実現する。

【解決手段】半導体装置のトリミング方法は、溶断部101aを有するポリシリコンヒューズ101を備えた半導体装置において、ポリシリコンヒューズ101に電圧を印加することによって溶断部101aを溶融すると共に、電圧の印加開始から所定の時間の後、溶融したポリシリコンヒューズに電流が流れている状態において電圧の印加を停止する。

(もっと読む)

再構成可能回路およびそのプログラミング方法

【課題】面積、消費電力、待ち時間が減少され、かつ再構成可能な集積回路を提供する。

【解決手段】再構成可能回路は、複数のロジックブロック(1)と、前記複数のロジックブロック(1)の間を接続する複数の配線(5,6)と、前記複数の配線(5,6)の間に選択的に挿入され、1kΩ以下のオン抵抗を有する複数のスイッチブロック(2)とを具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】製造時に電荷蓄積層に電荷が蓄積されてしまうことを抑制することが可能な半導体装置およびその製造方法を提供すること。

【解決手段】本発明は、半導体基板10上に設けられた電荷蓄積層20と、電荷蓄積層20に電荷をプログラムする際に用いられるゲート電極22と、ゲート電極22と接続するヒューズ56と、を有し、ヒューズ56は、ゲート電極22に電圧が印加される際は電気的に切断されている半導体装置およびその製造方法である。

(もっと読む)

半導体集積回路および半導体集積回路の設計方法

【課題】 クロックスキューの低減化およびチップ面積の削減化が図られた半導体集積回路を提供する。

【解決手段】 第1の半導体集積回路チップと第2の半導体集積回路チップとが互いに積層され、電気的に接続された半導体集積回路において、第1の半導体集積回路チップに配置されたクロック配線からクロック信号が供給された複数のフリップフロップ11と、第2の半導体集積回路チップに配置された組み合わせ論理回路群21とが、交互に接続されて形成された同期論理回路を備えた。

(もっと読む)

半導体装置及びその製造方法

【課題】安定して溶断することが可能な導電膜ヒューズを備える半導体装置及びその製造方法を提供することを目的とする。

【解決手段】フィールド絶縁膜上に形成された導電膜ヒューズ上に導電膜ヒューズの融点よりも高い高融点絶縁膜が形成され、導電膜ヒューズの被溶断部上には高融点絶縁膜除去部が形成され、高融点絶縁膜よりも融点の低い上部絶縁膜が高融点絶縁膜除去部を介して導電膜ヒューズと接するようにして高融点絶縁膜上に形成されている。

(もっと読む)

ラッチアップ防止を有する調整可能なボディバイアス生成回路網

【課題】調整可能なpチャネル金属酸化物半導体トランジスタボディバイアス生成回路網を備える集積回路を提供すること。

【解決手段】ボディバイアス経路を介してボディバイアス信号を受けるボディ端子を有する、pチャネル金属酸化物半導体トランジスタと、該ボディバイアス信号を該ボディバイアス経路に供給する調整可能なpチャネル金属酸化物半導体ボディバイアス生成回路網であって、該調整可能なpチャネル金属酸化物半導体トランジスタボディバイアス生成回路網は、高電力供給端子と該ボディバイアス経路との間に結合されたpチャネル制御トランジスタと、該pチャネル金属酸化物半導体トランジスタがラッチアップするのを防止するために、該ボディバイアス経路に接続された能動ラッチアップ防止回路とを含む、調整可能なpチャネル金属酸化物半導体トランジスタボディバイアス生成回路網とを備える、集積回路。

(もっと読む)

トリミング方法、半導体装置、及びトリミング用チップ部品

【課題】 その目的は、その目的は、基板に受動素子を設ける場合でも受動素子の特性の悪化を抑制すると共に、基板に設けた受動素子のトリミングを容易とするトリミング方法、半導体装置、及びトリミング用チップ部品を提供することにある。

【解決手段】 本発明は、基板の能動面に設けられた能動素子と、基板の厚さ方向に貫通する貫通電極12と、基板の能動面とは反対側の面10bに設けられると共に、貫通電極12を介して能動素子と電気的に接続された受動素子28と、を有し、基板をモジュール化した後、受動素子28の電気的特性を測定し、測定した電気的特性に基づいて、受動素子28の配線を切断若しくは接続、又は配線の一部を除去することにより、受動素子28の電気的特性のトリミングを行う。

(もっと読む)

半導体装置及びその製造方法

【課題】 Cuの埋め込み配線構造に於けるバリアメタルで構成したヒューズを少ない工程で容易に作製できるように、また、埋め込み配線表面とヒューズ表面とが同一面にある構造を実現しようとする。

【解決手段】 バリアメタル膜5とCuからなる配線7とが順に積層されて絶縁膜4中に埋め込まれた構造の一対のヒューズ電極を備え、バリアメタル膜5は両ヒューズ電極を隔てる絶縁膜4上を越えて両ヒューズ電極を結ぶと共に該絶縁膜4上に在る部分の表面がヒューズ電極及びその周辺と略同一面を成し且つ該絶縁膜4上に在る部分がヒューズ5Aを成している。

(もっと読む)

1 - 20 / 20

[ Back to top ]