Fターム[5F038AV06]の内容

半導体集積回路 (75,215) | 可変インピーダンス (2,334) | 可変素子(自身のインピーダンスを使用) (1,002) | MOSFET (453)

Fターム[5F038AV06]の下位に属するFターム

抵抗ゲート (22)

EPROM、EEPROM (55)

Fターム[5F038AV06]に分類される特許

1 - 20 / 376

半導体装置

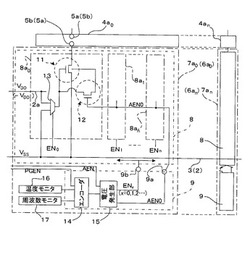

【課題】電源線と機能回路の間に電源スイッチとして接続されるMOSトランジスタのオン時のバックゲートの電圧を簡単な構造で調整することができる半導体装置を提供する。

【解決手段】一対の電源線2、3と、機能回路4a0〜4anと、一対の電源線2、3との少なくとも一方と機能回路4a0〜4anの間に接続されるスイッチング回路6a0〜6an、7a0〜7anとを有し、スイッチング回路6a0〜6an、7a0〜7anは、ソース/ドレインの一方が機能回路4a0〜4anに接続され、他方が前記一対の電源線2、3の一方に接続される第1のMOSトランジス11と、第1のMOSトランジスタ11のゲートとバックゲートを接続する抵抗素子12、21と、第1のMOSトランジスタ11のゲートに接続されるゲート電圧制御回路13と、を有する。

(もっと読む)

半導体装置

【課題】高品質な半導体装置を提供する。

【解決手段】第1の絶縁膜111、第1の電極112、第2の絶縁膜113、及び第2の電極114を含むゲート構造を有するメモリセルMCが複数設けられた記憶部11と、少なくとも外部100からのデータを受信し、記憶部にデータを供給する端子15と、第1の絶縁膜、第1及び第2の電極とを含むゲート構造を有し、電流経路の一端に第1の電圧が印加される第1導電型の第1のトランジスタ16a、一端が第1のトランジスタの電流経路の他端に接続され、他端が端子に接続される第1の抵抗素子16b、一端が端子及び第1の抵抗素子の他端に接続される第2の抵抗素子16c及び、ゲート構造を有し、電流経路の一端が第2の抵抗素子の他端に接続され、電流経路の他端に第2の電圧が印加される第2導電型の第2のトランジスタ16dを含む第1の回路16と、を備える。

(もっと読む)

集積回路

【課題】電力消費量の増大を抑制しつつ、タイミング信号のスキューを低減する。

【解決手段】第1のクロック分配回路は、タイミング信号を複数の第1の分配点に分配する。第2のクロック分配回路は、タイミング信号を複数の第2の分配点に分配する。最小遅延クロック信号出力部は、複数の第1の分配点のいずれかに分配されたタイミング信号と複数の第2の分配点のいずれかに分配されたタイミング信号とのうち遅延が小さい方の信号を最小遅延タイミング信号として出力する。同期動作回路は、最小遅延タイミング信号に同期して動作する。

(もっと読む)

集積回路

【課題】電力消費量の増大を抑制しつつ、タイミング信号のスキューを低減する。

【解決手段】主クロック分配回路は、タイミング信号を複数の主タイミング信号に分岐して分配する。副クロック分配回路は、タイミング信号の分配が指示された場合にはタイミング信号を複数の副タイミング信号に分岐して分配する。最小遅延タイミング信号出力部は、複数の主タイミング信号のいずれかと複数の副タイミング信号のいずれかとのうち先に分配された信号を最小遅延タイミング信号として出力する。同期動作回路は、最小遅延タイミング信号に同期して動作する。測定部は、複数の主タイミング信号のいずれかの遅延のばらつきを示す値を測定する。クロック分配回路制御部は、測定された値の示す前記ばらつきが前記所定値以上であるときに副分配回路に前記タイミング信号の分配を指示する。

(もっと読む)

半導体装置

【課題】酸化物半導体層を用いて作製された抵抗素子及び薄膜トランジスタを利用した論理回路、並びに該論理回路を利用した半導体装置を提供する。

【解決手段】抵抗素子354に適用される酸化物半導体層905上にシラン(SiH4)及びアンモニア(NH3)などの水素化合物を含むガスを用いたプラズマCVD法によって形成された窒化シリコン層910が直接接するように設けられ、且つ薄膜トランジスタ355に適用される酸化物半導体層906には、バリア層として機能する酸化シリコン層909を介して、窒化シリコン層910が設けられる。そのため、酸化物半導体層905には、酸化物半導体層906よりも高濃度に水素が導入される。結果として、抵抗素子354に適用される酸化物半導体層905の抵抗値が、薄膜トランジスタ355に適用される酸化物半導体層906の抵抗値よりも低くなる。

(もっと読む)

半導体装置

【課題】製造プロセスによる閾値電圧の変動に起因する歩留まりの悪化を抑制可能な半導体装置を提供する。

【解決手段】半導体装置は、複数のトランジスタが並列に接続された所定並列回路と、複数のトランジスタのオンオフ状態を制御しつつ所定並列回路のインピーダンスが所定値になったかを検出し、該インピーダンスが所定値になったときの複数のトランジスタのオンオフ状態に応じた制御値を生成する制御値生成部と、電源電圧を生成する電圧発生部と、電源電圧で動作する動作トランジスタと、制御値に基づいて電源電圧を制御する制御部と、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】チップ面積の増加を抑えつつ、金属等からなるゲート電極を有するMISトランジスタと、抵抗体とを同一基板上に不具合なく形成する。

【解決手段】半導体装置は、半導体基板1上にそれぞれ設けられたMISトランジスタと抵抗素子とを備える。MISトランジスタは、活性領域1aと、活性領域1a上に設けられたゲート絶縁膜18と、ゲート絶縁膜18上に設けられたゲート電極19とを有する。抵抗素子40は、素子分離領域2上に設けられた抵抗体10を有しており、ゲート電極19の少なくとも一部は、抵抗体10よりも小さな抵抗率を有しており、活性領域1a上においてはゲート電極19の上面を覆っておらず、抵抗体10の上面を覆っている層間絶縁膜16がさらに設けられる。

(もっと読む)

半導体装置およびその製造方法

【課題】メタルゲート電極とポリシリコン抵抗素子とを同じ半導体基板に混載するとともに、半導体装置の設計の自由度を向上し、また、半導体装置の小型化を図る。

【解決手段】半導体基板1の主面上にゲート絶縁膜を介してMISFET用のメタルゲート電極が形成され、また、半導体基板1の主面上に積層パターンLPを介してポリシリコン抵抗素子用のシリコン膜パターンSPが形成されている。メタルゲート電極は金属膜とその上のシリコン膜とを有し、積層パターンLPは絶縁膜3aとその上の金属膜4aとその上の絶縁膜5aとを有し、絶縁膜3aは、前記ゲート絶縁膜と同層の絶縁膜により形成され、金属膜4aはメタルゲート電極の金属膜と同層の金属膜により形成され、シリコン膜パターンSPは、メタルゲート電極のシリコン膜と同層のシリコン膜により形成されている。シリコン膜パターンSPは、平面視で絶縁膜5aに内包されている。

(もっと読む)

半導体装置

【課題】 本実施形態は、出力ドライバのドライブ能力のキャリブレーション精度を向上することが可能な半導体装置を提供する。

【解決手段】 第1、第2のプルアップドライバユニットPUDUa、PUDUbは、プルアップドライバを調整する。プルダウンドライバユニットPDDUbは、プルダウンドライバを調整する。キャリブレーション回路CBCは、プルアップドライバのキャリブレーション時、基準電圧VREFと、基準抵抗RZQに基づく第1のプルアップドライバの出力電圧を比較して第1、第2のプルアップドライバユニットのドライブ能力を決定し、プルダウンドライバのキャリブレーション時、基準電圧と、第2のプルアップドライバとプルダウンドライバの接続ノードの電圧を比較してプルダウンドライバのドライブ能力を決定する単一の比較器COMPを有している。

(もっと読む)

半導体装置及びその製造方法

【課題】 シリコンビームを使用しかつダブルゲートを有する半導体装置のおけるプロセスばらつきによる抵抗値ばらつきを防止する。

【解決手段】 端部に凹部を有する基板1と、基板1の凹部に一部が埋め込まれた一対のゲート電極4と、基板1の表面であって一対のゲート電極4の間に形成された拡散層7を有し、ゲート電極4と拡散層7の間の電位を変化させることにより、拡散層7の抵抗値を変化させる。

(もっと読む)

半導体装置および基準電圧生成回路

【課題】所望の温度特性を有することによって回路規模を小さくできるMOSトランジスタを提供する。

【解決手段】ゲート電極はP型半導体層及びN型半導体層からなるので、P型半導体層とN型半導体層との接合面に、空乏層13が生じる。温度が変化すると、空乏層13の領域の面積が変化し、P型半導体層11及びN型半導体層12の領域の面積もそれぞれ変化することで、MOSトランジスタに所望の温度特性を与えられる。その結果、温度補正回路を簡単にする、あるいは不要にすることができる。

(もっと読む)

半導体装置及びその製造方法並びに抵抗器及び半導体素子

【課題】pn接合におけるリーク電流を抑制する。

【解決手段】N−型半導体層10と、シリサイド層20sがその表面に形成されたP−型半導体層20とが、絶縁体9上に形成される。半導体層10にはPMOSトランジスタを、半導体層20にはNMOSトランジスタを、それぞれ形成することができる。半導体層10,20がpn接合J50aを形成する場合、これはシリサイド層20sの端部から近く、結晶欠陥が小さい位置に存在するので、ここにおけるリーク電流は非常に小さい。半導体層10,20が形成するpn接合は、シリサイド層20sの端部から2μm以下の距離にあることが望ましい。

(もっと読む)

定電圧回路とその半導体装置

【課題】 ツェナーダイオードと同等の動作を行える回路ないしは半導体装置を提供することを目的とする。

【解決手段】 実施形態の基準電圧発生回路は、第1のFETと、第2のFETと、一方を電源に接続し他方を前記第1のFETのドレインに接続した第1の抵抗と、前記第1のFETのドレイン−ゲート間に接続した第2の抵抗とを有し、前記第2のFETのゲート−ソース間を接続し、前記第2のFETのドレインを前記第1のFETのゲートに接続し、前記第1のFETのドレインが基準電圧を出力し、前記第1のFETのソースと前記第1のFETのソースがグランド又は他の回路と接続していることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】高誘電率の絶縁膜を有するnチャネル型トランジスタやpチャネル型トランジスタを有する半導体装置の製造方法において、nチャネル型トランジスタのゲート絶縁膜の側面への異物の付着を抑制する。

【解決手段】半導体基板の主表面上の、p型不純物領域PWLに機能用nチャネル型トランジスタが、n型不純物領域NWLに機能用pチャネル型トランジスタが形成される。p型不純物領域PWLの、平面視における機能用nチャネル型トランジスタ以外の領域に形成される複数の第1の周辺用トランジスタは、周辺用n型ゲート構造体と周辺用p型ゲート構造体とが混在するように形成される。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】実用上限温度をより向上させた炭化珪素半導体装置の製造方法を提供する。

【解決手段】ゲート窓6が形成された炭化珪素基板1の表面に、前駆酸化シリコン膜を成膜する工程と、前駆酸化シリコン膜を酸化窒素ガス雰囲気で熱処理して第1の酸化シリコン膜(O)とする工程と、窒化シリコン膜(N)を積層する工程と、窒化シリコン膜を酸化させて、表面から所定の深さまで第2の酸化シリコン膜(O)を形成して、ONO絶縁膜を形成する工程と、ONO絶縁膜の上にゲート電極を形成する工程とを備える。ゲート電極を形成する工程は、ONO絶縁膜の上に多結晶シリコン膜を成膜する工程と、所望のマスクを用いて、多結晶シリコン膜、第2の酸化シリコン膜、窒化シリコン膜、を連続的にエッチングして、ゲート電極と第2の酸化シリコン膜と窒化シリコン膜の外縁を定義する工程と、ゲート電極の側面及び上部と窒化シリコン膜の外縁を酸化する工程を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜をHigh−k材料で構成し、ゲート電極をメタル材料で構成するHK/MGトランジスタと、抵抗素子とを同一基板に有する半導体装置において、安定したHK/MGトランジスタの動作特性を得ることのできる技術を提供する。

【解決手段】TiN膜と多結晶Si膜との積層膜からなるHK/MGトランジスタのゲート電極を形成し、同様に、TiN膜と多結晶Si膜との積層膜からなる抵抗素子を形成した後、抵抗素子の側壁に形成したオフセットサイドウォール9aおよびサイドウォール9の一部を除去し、そのオフセットサイドウォール9aおよびサイドウォール9が除去された箇所から薬液を浸入させることによりTiN膜を除去して空洞18を形成し、多結晶Si膜のみからなる抵抗部RESを形成する。

(もっと読む)

半導体装置、回路基板装置及び情報処理装置

【課題】小規模な回路で送受信に応じた最適なインピーダンス調整を行う。

【解決手段】選択部15が、送信部11のインピーダンス調整時か、受信部12のインピーダンス調整時かに応じて異なる基準電圧を選択し、選択した基準電圧を基準電圧生成部14に生成させ、基準電圧生成部14が、選択部15により選択された基準電圧を生成して、インピーダンス調整部13に入力し、インピーダンス調整部13が、入力された基準電圧に応じて、送信部11または受信部12のインピーダンスを別々に調整する。

(もっと読む)

半導体装置の製造方法

【課題】半導体素子単体の駆動力にはバラツキがあっても、搭載回路の駆動力のウェーハ間のバラツキを抑制することのできる半導体装置の製造方法を提供する。

【解決手段】実施形態の製造方法は、複数の半導体素子が並列に配置された回路を有する半導体装置の製造方法であって、上層配線形成工程用に、複数の半導体素子の並列接続数がそれぞれ異なる複数のマスクを製作しておき(工程S01)、半導体基板上に半導体素子を形成し(工程S02)、上層配線を形成する工程の前に、半導体基板上に形成された半導体素子のオン電流の測定を行い(工程S03)、その測定の結果にもとづいて、上層配線形成工程用の複数のマスクから1枚のマスクを選択し(工程S04)、選択したマスクを用いて上層配線を形成する(工程S05)。

(もっと読む)

半導体装置、半導体集合部材及び半導体装置の製造方法

【課題】様々なオン抵抗の素子を容易に製造することができる半導体装置、半導体集合部材及び半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、素子部と、第1の電極部と、第2の電極部と、延出部と、を備える。素子部は、基板に設けられる。第1の電極部は、素子部の上に設けられ、素子部と導通する。第2の電極部は、素子部の上において第1の電極部と離間して設けられ、素子部と導通する。延出部は、素子部の上に設けられ、第1の電極部及び第2の電極部の周縁部から基板の周縁部に向けて延出して設けられる。

(もっと読む)

半導体装置及びサンプルホールド回路

【課題】ON状態での低いオン抵抗とOFF状態での小さいオフリーク電流を持つMOSトランジスタスイッチを用いた半導体装置及びサンプルホールド回路を実現する。

【解決手段】PMOSトランジスタM11がON状態の場合には、PMOSトランジスタM12がON状態になりPMOSトランジスタM11のバックゲート端子をPMOSトランジスタM11のソース端子に接続し、PMOSトランジスタM11がOFF状態の場合には、PMOSトランジスタM13がON状態になりPMOSトランジスタM11のバックゲート端子を電源電圧端子VDD1に接続する。

(もっと読む)

1 - 20 / 376

[ Back to top ]