Fターム[5F038AV11]の内容

Fターム[5F038AV11]の下位に属するFターム

マスクワーク (49)

スイッチ素子による切換 (1,056)

Fターム[5F038AV11]に分類される特許

1 - 12 / 12

半導体装置の製造方法

【課題】高い回路性能と安定動作とを両立した半導体装置を製造することが可能な半導体装置の製造方法を提供する。

【解決手段】試験結果に応じた調整を行う調整回路を含む半導体装置の製造途中において、当該半導体装置を試験し(ステップS3)、その試験結果に応じて電子ビーム描画装置による電子ビーム描画によって、配線パターンやビアパターンなどを形成することにより、調整回路の回路パターンを確定させる(ステップS4)。その後は、残りの半導体製造工程を行い半導体装置を完成させる(ステップS5)。

(もっと読む)

半導体装置

【課題】Depletion型MOS TrとEnhance型MOS Trによって形成される半導体装置において、回路的な付加によって半導体装置の面積を増大させることなく、温度特性やアナログ特性を向上させた基準電圧回路を提供する。

【解決手段】異なる濃度を有するDepletion型MOS TrとEnhance型MOS Trのウェル領域を作製する。

(もっと読む)

発振装置の製造方法及び発振装置

【課題】発振装置の発振周波数の調整において、歩留りを向上させやすくする。

【解決手段】半導体基板7に形成された第1電極に、圧電体で構成される圧電体膜を重ねて形成し、前記圧電体膜に、前記圧電体膜を挟んで前記第1電極に対向する第2電極を形成して、前記第1電極、前記圧電体膜及び前記第2電極を構成の一部として有する第1キャパシタを形成する工程と、容器3の底となる第3基板45に、容器3の内側及び外側の間を貫通する貫通孔61が設けられた容器3内に、半導体基板7を、半導体基板7が貫通孔61を塞ぐように、且つ平面視で、前記第1キャパシタが貫通孔61に重なるように実装する工程と、前記発振回路の発振周波数を測定した結果に基づいて、半導体基板7によって塞がれた貫通孔61内に容器3の外側から圧力P1を付与した状態で、貫通孔61を容器3の外側から塞ぐ工程と、を有する。

(もっと読む)

レベルシフト回路

【課題】回路面積の増加を抑制して耐圧を向上することが可能なレベルシフト回路を提供する。

【解決手段】第1、第2のトランジスタP13, P14は電流通路の一端に高電圧が供給され、ゲートと電流通路の他端が互いに交差接続される。第3のトランジスタP15は第1のトランジスタの電流通路の他端に挿入され、ゲートに一定電圧が供給され電流通路の一端とウェルとが接続されている。第4のトランジスタP16は第2のトランジスタの電流通路の他端に挿入され、ゲートに一定電圧が供給され、電流通路の一端とウェルとが接続されている。第5、第6のトランジスタN11, N12は第3、第4のトランジスタの電流通路の他端に接続され、ゲートに相補入力信号が供給される。第7、第8のトランジスタN13, N14は、第3、第4のトランジスタのウェルに接続され、ゲートに相補出力信号が供給される。

(もっと読む)

設定可能な入出力を有するダイ装置およびその制御方法

集積回路用の金属製の設定可能なI/O構造が開示される。この金属製の設定可能なI/O構造は複数のI/O仕様の任意のものに対して構成することができる。共通電圧参照および共通電流参照が複数のI/O構造に対して提供されるために生成されることが好ましい。  (もっと読む)

(もっと読む)

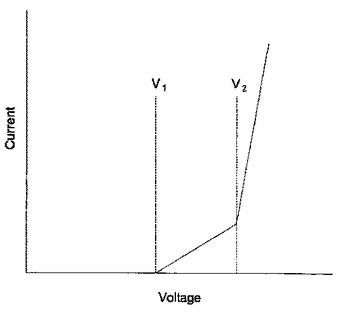

ステップ電圧応答を有する電圧切り換え可能な誘電体材料の組成及び該誘電体材料の製造方法

電圧切り換え可能な誘電材料の組成は、誘電母体材料内に均一に分散する2種類以上の異なる半導体材料を有する。前記半導体材料は、生成された電圧切り換え可能な誘電材料に様々な過電圧のレベルに対するステップ応答を供するため、それぞれ異なるバンドギャップエネルギーを有するように選ばれる。前記半導体材料は、無機の粒子、有機の粒子、又は前記誘電母体材料内で可溶であるか、又は該誘電母体材料と混和可能な有機材料を有して良い。組成はまた任意で電気伝導性材料をも有して良い。組成中での前記伝導性材料又は前記半導体材料のうちの少なくとも1つはアスペクト比が少なくとも3以上であることを特徴とする粒子を有して良い。  (もっと読む)

(もっと読む)

半導体集積回路装置

【課題】制御される電流値の合わせ込みが可能で、比較的大きい電流を制御するものであっても組み立て前のウェハ検査を可能とする。

【解決手段】IC11のチップ12に、実使用時に使われるシャント抵抗Rmよりも高抵抗のシャント抵抗Rsを形成する。ウェハ検査ではスイッチ回路SW1、SW2をオフ、SW3、SW4をオンとし、制御信号生成回路16にシャント抵抗Rsの両端電圧を入力する。IC11の実使用時にはスイッチ回路SW1、SW2をオン、SW3、SW4をオフとし、制御信号生成回路16にシャント抵抗Rmの両端電圧を入力する。ウェハ検査の結果、シャント抵抗Rmの抵抗値が目標値に等しい場合、組み立て工程でパッドPmとリード電極Tbとを接続し、パッドPsをオープンとする。シャント抵抗Rmの抵抗値が目標値よりも高い場合、組み立て工程においてさらにパッドPsとリード電極Tbを接続する。

(もっと読む)

調整可能なオンチップ・サブキャパシタ設計

【課題】 その目標値の約1%と5%との間の範囲内で正確に較正される容量値を有するキャパシタがその上にマウントされた、シリコン半導体チップを提供すること。

【解決手段】 1つ又は複数のオンチップVNCAP又はMIMCAPキャパシタは、キャパシタの均一な静電容量値を改良するために、可変MOSキャパシタを使用する。これにより、その設計値の約1%と5%との間の範囲内に正確に調整される静電容量値を有するキャパシタがその上にマウントされた、シリコン半導体チップの製造が可能となる。この最適化は、DC減結合のために、一対の可変MOSキャパシタ間のバック・ツー・バック接続を使用することによって、達成されることができる。それは、一対のバック・ツー・バック可変MOSキャパシタをFEOL中に挿入することによる、VNCAP及び/又はMIMCAPキャパシタのオンチップBEOL静電容量の並列化を伴う。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】IDタグに使用する搬送波の周波数に応じて入力インピーダンスを変更し、アンテナ整合回路部の変更や半導体チップの品種変更などを不要とし、低コスト化を実現する。

【解決手段】RFIDチップ1には、搬送波の周波数に応じて入力インピーダンスの整合を行うインピーダンス整合回路6,7が設けられている。搬送波の周波数が2.4GHz帯の際には、インピーダンス整合回路6を用いてインピーダンス整合を行い、搬送波の周波数が900MHz帯の際には、インピーダンス整合回路6とインピーダンス整合回路7との両方の回路を用いてインピーダンス整合を行う。インピーダンス整合回路7を接続する際には、スルーホールTH1,TH2を介してアンテナ用パッド1aとグランドパッド1bとの間に接続する。スルーホールTH1,TH2は、配線工程において、電子ビーム直接描画装置を用いて形成する。

(もっと読む)

集積回路の相互接続システム

【課題】相互接続システムの周波数応答の種々の特性を大幅に改善する手段を提供すること。

【解決手段】多数の回路デバイスが共通のI/O端子にアクセスできるようにするための相互接続システムにおいて、それらの各々のデバイスに、IC内において個別の接触パッドが提供される。接触パッドは、ボンディングワイヤやIC内の金属被膜パターン、または、石版印刷によってICに形成された二また構造のばね接触部の足のような誘導性の導体を介して、互いに接続されるとともにICのI/O端子に接続される。さらに、ESDの保護機能は、直列インダクタによって相互接続された複数のESDデバイスに分散され、各ICの端子において多極フィルタが形成される。導体のインダクタンス及び相互接続システムの種々の容量を適切に調整することによって、所望の相互接続システムの周波数応答特性が最適化される。

(もっと読む)

半導体装置及びその製造方法

【課題】アンテナ搭載ICチップの小型化、低コスト化を図りつつ、共振周波数の適切な調整を行うことが可能な半導体装置とその製造方法を提供する。

【解決手段】電極3Aを一方の面に有する半導体基板2の一面を覆うように絶縁樹脂層4を形成する。次いで、絶縁樹脂層4が形成された半導体基板2の上に、電極3Aと整合する位置に開口部を形成し、前記電極3Aを露出させる。次に、絶縁樹脂層4の上に、開口部の一つを通して一端5aが電極3Aと電気的に直接接続されるアンテナ本体5、及び図示しない他の開口部を介して一端6aa,6ba,6caが全て、図示しない他の電極と電気的に直接接続される、前記アンテナ本体5の長さを調整する長さの異なる複数の調整部6a,6b,6cを有するアンテナ長調整用配線6をそれぞれ形成することにより、半導体装置1とする。

(もっと読む)

マルチチップパッケージ型半導体装置

【課題】 複数の半導体チップの実装状態の管理が可能なマルチチップパッケージ型半導体装置を提供する。

【解決手段】 本発明のマルチチップパッケージ型半導体装置は、モジュール基板10、第1の半導体チップ15、第2の半導体チップ25、およびこのモジュール基板10上に実装され、書き込み可能で電気的に読み出し可能な不揮発性メモリチップ35とを備え、この不揮発性メモリチップ35に、第1の半導体チップ15および第2の半導体チップ25の実装状態を示す実装管理データ、製造履歴を示す製造管理データ、および購入履歴を示す購入管理データを記憶させている。

(もっと読む)

1 - 12 / 12

[ Back to top ]