Fターム[5F045HA20]の内容

気相成長(金属層を除く) (114,827) | 他プロセスとの組合せ (2,158) | 後処理(膜形成が先) (953) | 不純物拡散 (10)

Fターム[5F045HA20]に分類される特許

1 - 10 / 10

光電変換素子の製造方法および光電変換素子

【課題】 結晶性を向上させることが可能な光電変換素子の製造方法および光電変換素子。

【解決手段】 本発明の光電変換素子の製造方法は、p型シリコン基板2上に、ガリウムヒ素を含む第1半導体層3を成長させる工程と、第1半導体層3を成長させたp型シリコン基板2を、リンを含む第1ガスの雰囲気内において第1温度で加熱することにより、第1半導体層3を経由させてp型シリコン基板2内にリンを拡散させる工程と、第1半導体層3上に、格子定数が、シリコンよりもガリウムヒ素に近い第2半導体層4を成長させる工程とを有する。そのため、p型シリコン基板内にリンを拡散させるとともに、第1半導体層の表面に成長させる半導体層の結晶性を向上させることができる。

(もっと読む)

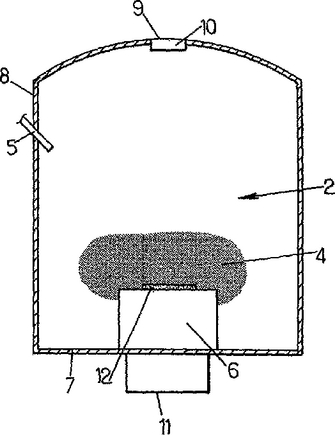

半導体装置の製造方法及び基板処理装置

【課題】 低コストで必要な仕事関数及び耐酸化性を有する金属膜を備えた半導体装置を提供する。

【解決手段】 表面に金属膜が形成された基板を処理容器内に搬入する工程と、処理容器内に原料ガスと酸化源とを供給し排気することで、基板の表面に形成された金属膜上に所定膜厚の金属酸化膜を形成する処理を行う工程と、処理済基板を処理容器内から搬出する工程と、を有し、処理を行う工程では、酸化源としてオゾンガス、酸素ガスまたはプラズマにより活性化された酸素ガスを用い、所定膜厚の金属酸化膜を形成する過程において形成される金属酸化膜越しに、酸化源に含まれる酸素原子を、金属膜の表面に導入することで、金属膜の表面を酸化して導電性の金属酸化層に改質する。

(もっと読む)

半導体基板の製造方法

【課題】SiCを用いた半導体装置を効率よく製造するための半導体基板の製造方法を提供する。

【解決手段】第1の裏面B1を有する第1の炭化珪素基板11と、第2の裏面B2を有する第2の炭化珪素基板12とが準備される。第1および第2の裏面B1、B2の各々が一の方向に露出するように第1および第2の炭化珪素基板11、12が配置される。炭化珪素からなり、かつ第1および第2の裏面B1、B2を互いにつなぐ成長層30が化学気相成長法によって形成される。

(もっと読む)

圧力制御機器、圧力制御方法および基板処理装置

【課題】複数の処理工程(プロセス)を連続して行う基板処理装置において、チャンバー内の処理ガス流量や処理ガス圧力の大幅な変動に対して短時間で連続的に応答可能な圧力制御を行う圧力制御機器、圧力制御方法および該圧力制御機器を備える基板処理装置を提供する。

【解決手段】処理ガスが供給される減圧状態の処理室で複数の処理工程を行う基板処理装置であって、処理室に処理ガスを供給する処理ガス供給機構と、処理室の内部を排気する排気機構と、排気機構の排気量を調節する排気バルブと、複数の処理工程それぞれに最適な処理ガス圧力を算出するための演算テーブルを複数有し、演算テーブルに基づいて排気バルブの開度を制御する演算制御機構と、を備える基板処理装置が提供される。

(もっと読む)

炭化シリコン膜の製造方法

【課題】エッチングが困難な炭化シリコン膜をエッチングすることなく、パターニングされた炭化シリコン膜を得ることが可能な炭化シリコン膜の製造方法を提供する。

【解決手段】本発明の炭化シリコン膜13の製造方法は、基板11上にアモルファスシリコンとポリシリコンとの少なくとも一方を含むシリコン膜14を形成する工程と、シリコン膜14をパターニングするパターニング工程と、パターニング工程の後にシリコン膜14を炭化処理し炭化シリコン膜13を形成する工程と、を有することを特徴とする。

(もっと読む)

半導体構造のドープ方法およびその半導体デバイス

核種を歪み半導体層の中に導入する方法であって、露出した歪み半導体層を含む第1領域を備えた基板を用意し、該基板を反応チャンバの中に投入するステップと、少なくとも露出した歪み半導体層の上に、気相堆積(VPD)によって等方性の第1核種含有層を形成するステップと、続いて、第1熱処理を実施し、これにより第1核種含有層から第1核種の少なくとも一部を歪み半導体層の中に拡散し、歪み半導体層の中に拡散した第1核種の少なくとも一部を活性化するステップとを含む。  (もっと読む)

(もっと読む)

半導体素子の製造方法

【課題】p型半導体層とp側電極などのと接触状態を良好なオーミックコンタクトとすることが可能な半導体素子の製造方法を提供すること。

【解決手段】基板1にp型不純物がドープされたGaN層2Aを形成する工程と、GaN層2Aに対して活性化処理を施すことによりp型半導体層2を形成する工程と、を有する半導体素子の製造方法であって、上記活性化処理を、GaN層2Aが形成された基板1を、溶融したGaに浸漬させた状態で行う。

(もっと読む)

半導体基板上にエピタキシャル層を形成する方法およびこの方法によって形成するデバイス

本発明は、エピタキシャル層の製造に関し、半導体基板を用立てるステップと、第1の深さを有するSi−Ge層を半導体基板上に設けるステップと、第1の深さよりも十分に深い第2の深さを有し、かつ、n型のドーパント材料でドープした層を、半導体基板に設けるステップと、Ge原子およびn型原子が、二酸化シリコン/シリコン界面にて二酸化シリコンによって半導体基板内へ押し込まれるように、二酸化シリコン層を形成すべく酸化処理を行うステップであって、n型原子が、Ge原子よりも深く半導体基板内に押し込まれて、その結果頂部層のn型原子の濃度を低減させるようにするステップと、二酸化シリコン層を取り除くステップと、半導体基板上にシリコンのエピタキシャル層を、外方拡散またはオートドーピングを低減させて成長させるステップとを含む。  (もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 トランジスタの信頼性の劣化を抑制しつつ、高電圧駆動を可能とするとともに高速化を図る。

【解決手段】 酸化防止膜4をマスクとしてエピタキシャル成長を行うことにより、第1単結晶半導体層3上に第2単結晶半導体層5を形成し、酸化防止膜4をマスクとして第2単結晶半導体層5の熱処理を行うことにより、第2単結晶半導体層5の構成成分を第1単結晶半導体層3内に拡散させ、第1単結晶半導体層3の一部を第3単結晶半導体層7に変換した後、第1単結晶半導体層3上および第3単結晶半導体層7上に第4単結晶半導体層8を形成し、第3単結晶半導体層7上に配置された第4単結晶半導体層8上にゲート絶縁膜11を形成するとともに、オフセットゲート層15bおよびドレイン層15cを第1単結晶半導体層3および第4単結晶半導体層8に形成する。

(もっと読む)

高い電気伝導率を有するn−型ダイヤモンドを製造する方法

本発明は、n−型ダイヤモンドを製造する方法に関する。本発明の方法は、n−ドーピングステップを含み、その間において、アクセプタとドナー種との間に形成された錯体の解離温度以下、またはその温度と等しい温度で、ドナー種を含んだドナー基を形成するために、ドナー種が、最初にアクセプタ(12)でドーピングされたダイヤモンド中で真空拡散される。  (もっと読む)

(もっと読む)

1 - 10 / 10

[ Back to top ]