Fターム[5F046EA23]の内容

半導体の露光(電子、イオン線露光を除く) (57,085) | 位置合わせマーク (981) | マークの製造 (140) | エッチング (43)

Fターム[5F046EA23]に分類される特許

1 - 20 / 43

基板作製方法

【課題】アライメントマークが形成された基板を作製するにあたって、光によるアライメントマークの検出を可能としつつ、アライメントマークを形成する時間を短縮させる。

【解決手段】基板に対してアライメントマークを形成する際の基板作製方法において、前記基板を覆うようにレジスト層を形成する工程と、前記レジスト層にエネルギービームを照射することにより、所定のパターンの描画又は露光を行う露光工程と、前記描画又は露光されたレジスト層を現像し、凹凸からなるレジストパターンを形成するレジストパターン形成工程と、前記レジストパターン形成工程後、前記レジストパターンを有する部分における基板の少なくとも一部に対してウェットエッチングを行い、前記一部におけるレジストパターンの凹部よりも大きく、且つ、光を用いて検出可能な大きさを有するアライメントマークを前記基板上に形成するアライメントマーク形成工程と、を有する。

(もっと読む)

ワイドギャップ半導体基板およびワイドギャップ半導体装置の製造方法

【課題】ワイドギャップ半導体基板の位置検出を、可視光を用いて高精度に行う。

【解決手段】一実施形態によれば、ナローギャップ半導体基板(例えばSi基板2)の主面の所定の位置に彫り込み型のアライメントマーク4が形成されたナローギャップ半導体基板のその主面上にワイドギャップ半導体層(例えばGaN層19)をエピタキシャル成長したことにより、基板位置決め用のアライメントマークが予め埋め込まれているワイドギャップ半導体基板を提供する。

(もっと読む)

半導体装置の製造方法

【課題】アライメントマーク形成工程時のエピタキシャル層の侵食を低減させる手段を提供すること。

【解決手段】異方性エッチングすることにより、アライメントマークの段差21の側壁にのみ珪素系膜22を形成する。段差21の側壁に珪素系膜22が形成されることにより、エピタキシャル層30がアライメントマーク領域A全体に積層された場合であっても、側壁においてエピタキシャル層30の成長を抑制させることができ、段差21は順テーパー形状を維持することが可能となる。

(もっと読む)

半導体装置の製造方法

【課題】チップパターンを複数の領域に分け、各領域を別々に露光し繋ぎ合わせる分割露光を行なう際に、各領域間の繋ぎ合わせ精度を高精度にする。

【解決手段】分割パターン領域を露光する際に位置合せを行なうアライメントマークの形成を、先行の分割露光領域の外周近傍にX方向用Y方向用を1対とするアライメントマークを少なくとも1対以上設け、後行の分割露光領域は先行の分割露光領域の外周近傍にある少なくとも1対のアライメントマークを含む重複領域を持ち、後行の露光領域から見た前記アライメントマーク座標で位置合せを行なうことを繰り返すことにより、チップパターンの全ての分割パターン領域用のアライメントマークを設ける。さらに、重ね合わせ層の露光において、高配置精度で設けた各分割パターン領域露光用アライメントマークに対して、ダイ・バイ・ダイ・アライメント法を用いて位置合せを行なう。

(もっと読む)

半導体基板及び半導体基板の製造方法

【課題】半導体基板のアライメントマークを繰り返し使用する。

【解決手段】ベース基板にアライメントマークを形成する段階と、アライメントマークを形成する段階の後に、ベース基板上のアライメントマークを含む領域に、結晶成長を阻害する阻害層を形成する段階と、アライメントマークの位置を基準とする開口を形成すべき位置を示す情報に基づいて、阻害層におけるアライメントマークが設けられていない領域に、ベース基板を露出する開口を形成する段階と、開口内に半導体結晶を成長させる段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

半導体装置の製造方法

【課題】半導体素子構造を構成する半導体層の成長用基板として、該半導体層と同種の半導体材料を用いる場合に、半導体層を成長した後の露光時に認識可能なアライメントマークを形成できるようにする。

【解決手段】アライメントマーク検出用光源に対して透明な材料からなる基板101の上に、該基板101と異なる屈折率を有する材料からなる第2のアライメントマーク120を形成する。続いて、基板101の上に、活性層105を含むGaN系エピタキシャル層を第2のアライメントマーク120を埋め込むように成長する。続いて、第2のアライメントマーク120を参照しながら、GaN系エピタキシャル層に対する露光の位置合わせを行う。

(もっと読む)

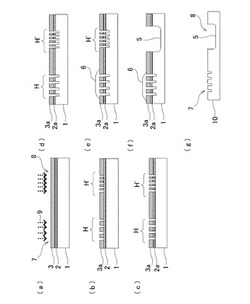

半導体装置及び半導体装置の製造方法

【課題】透過膜に覆われた状態でも画像認識精度の低下を抑制し得るアライメントマークを備えた半導体装置、および半導体装置の製造方法を得る。

【解決手段】アライメントマーク11のマーク本体領域15にストライプ状の周期構造を形成する。その周期構造により、位置合わせのための撮像時の照射光の反射が大幅に抑制され、マーク本体領域15の輝度が低くなる。一方、マーク本体領域15の周囲のベース領域17は、反射性に優れ、輝度が高くなる。その結果、コントラストが良好になり、画像認識精度が向上する。さらに、マーク本体領域15での照射光の反射が大幅に抑制されるため、アライメントマーク11を光透過性の膜が覆っている場合でも、薄膜による干渉等によってコントラストが低下しにくくなっており、画像認識精度の低下を抑制し得る。

(もっと読む)

重ね合わせ測定マーク及びパターン形成方法

【課題】重ね合わせ測定の精度を向上できる重ね合わせ測定マークを提供する。

【解決手段】第1パターンと第2パターンの重ね合わせ測定のためのマークにおいて、プラグ用ホールの開口パターンからなる第1パターンが形成された層間絶縁膜に該プラグ用ホールと同時に形成された第1ホールの開口パターンからなる第1マークと、前記層間絶縁膜に第1ホールと同時に形成され、前記プラグ用ホールの開口サイズと同程度で且つ第1ホールの開口サイズより小さい開口サイズを有する第2ホールの開口パターンからなる第2マークと、前記層間絶縁膜上の導電膜上に形成されたレジスト膜をパターニングして第2パターンと同時に形成されたレジストパターンからなる第3マークを含む構成とする。

(もっと読む)

デバイスの製造方法

【課題】デバイスの性能に影響を与えず、高精度の検出が可能なアライメントマークを形成することができるデバイスの製造方法の提供。

【解決手段】上層側の第1の膜が、下層側の第2の膜に対するエッチングに耐性を有する材料で構成される積層膜を形成する工程と、素子形成領域及びアライメントマーク形成領域の前記第1の膜をパターニングする工程と、少なくとも前記アライメントマーク形成領域の前記パターニングした第1の膜近傍を除く領域を、前記第2の膜に対するエッチングに耐性を有する材料で保護する工程と、前記パターニングした第1の膜をマスクとして、前記第2の膜を選択エッチングするエッチング工程と、を少なくとも有し、前記パターニングした第1の膜の周囲を掘下げることにより、前記第1の膜からなるアライメントマークの段差を増大させる。

(もっと読む)

マーカの形成方法、マーカを有する基板及びデバイス製造方法

【課題】 改良されたマーカの形態、特にアラインメント及びオーバレイマーカ、及び基板上にこれらのマーカを形成する方法を提供する。

【解決手段】 第一に、プロダクトフィーチャと同等のピッチP1を有する2つの化学的に異質のフィーチャタイプのパターンを形成する。次にこのパターンを、パターンより大きいピッチP2を有する所望のマーカの形態のレジスト11によってマスキングする。最後に、2つのフィーチャタイプの一方を、開放領域内で選択的にエッチングする。その結果は、長い波長の放射で読み取るのに適切な大きいピッチP2を有するマーカであるが、フィーチャの縁部は、プロダクトフィーチャと同等のピッチP1を有する露光ステップで画定される。

(もっと読む)

パターン形成方法およびオフセット値の決定方法

【課題】精度の高い位置計測に有利なパターン形成技術を提供する。

【解決手段】パターン形成方法は、膜の形成、第1レジストを塗布する第1塗布、前記第1レジストを露光する第1露光、前記第1レジストを現像する第1現像および前記膜をエッチングする第1エッチングを含む第1リソグラフィー工程により少なくとも1つの第1エッジ対を含む第1エッジ群を前記膜に形成する第1工程と、第2レジストを塗布する第2塗布、前記第2レジストを露光する第2露光、前記第2レジストを現像する第2現像および前記膜をエッチングする第2エッチングを含む第2リソグラフィー工程により少なくとも1つの第2エッジ対を含む第2エッジ群を前記膜に形成する第2工程とを含み、前記第1エッジ対は、第1対称軸に関して対称な位置に配置された2つの第1エッジで構成され、前記第2エッジ対は、第2対称軸に関して対称な位置に配置された2つの第2エッジで構成される。

(もっと読む)

半導体装置の製造方法

【課題】トレンチ形成工程を有する半導体装置の製造方法において、並列pn構造の形成と同時に位置合わせマーカを形成し、製造プロセスの効率化を図ること。

【解決手段】n型シリコン基板21の表面にn型半導体22を形成し、n型半導体22の表面にマスク酸化膜を形成する。次いで、フォトリソグラフィおよびエッチングによってマスク酸化膜を開口し、シリコン基板21に達する第1のトレンチを形成する。同時に、第1のトレンチよりも深い第2のトレンチが形成される。次いで、第1のトレンチをp型半導体27で埋める。同時に、第2のトレンチがp型半導体28で埋められる。次いで、n型半導体22の表面を研磨し平坦化する。ここまでのプロセスで、並列pn構造が形成される。このとき、第2のトレンチの上部はp型半導体28で埋まらずに残り、並列pn構造の表面に窪みが形成される。この窪みが、後の工程において位置合わせマーカとして機能する。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】SiC基板1にデバイスを形成するための第1のトレンチ2およびアライメントマークとして利用するための第2のトレンチ4を形成し、第1のトレンチ2内および第2のトレンチ4内にエピタキシャル層6を成長させた際にもアライメントマークとして利用することができるようにするSiC半導体装置の製造方法を提供する。

【解決手段】第1のトレンチ2の立体角が第2のトレンチ4の立体角より大きくなるように第1のトレンチ2および第2のトレンチを形成する。これにより、エピタキシャル層6を成長させた際に、第1のトレンチ2の底部の成長レートを第2のトレンチ4の底部の成長レートより大きくすることができる。このため、SiC基板1の表面を平坦化した際に、第2のトレンチ4が形成されていた部分に表面が凹まされた凹部7が形成されている状態にすることができ、この凹部7をアライメントマークとして利用することができる。

(もっと読む)

半導体装置とその製造方法、及び露光用マスク

【課題】ダイシング時にプロセスマークが飛散するのを防止できる半導体装置とその製造方法、及び露光用マスクを提供すること。

【解決手段】シリコン基板11の上方に導電膜を形成する工程と、導電膜をパターニングすることにより、平面形状が矩形状のデバイス領域13にゲート電極(デバイスパターン)52を形成すると供に、該デバイス領域13よりも外側であって、スクライブライン15よりも内側の空き領域E1にプロセスパターン12を形成する工程とを有し、プロセスパターン12を、デバイス領域13の隣接する二辺L1、L2の近傍のみに形成し、残りの二辺L3、L4の近傍には形成しない半導体装置の製造方法による。

(もっと読む)

光半導体デバイスの作製方法

【課題】工程数の増加を抑えつつアライメントマークを適切に保護できる光半導体デバイスの作製方法を提供する。

【解決手段】InP基板12となるウェハ上に半導体メサ14となる半導体積層を形成する工程と、半導体メサ14及びアライメントマーク50の平面形状を含むエッチングマスクを用いて半導体積層をエッチングすることにより、半導体メサ14及びマーク用メサを形成する第1のエッチング工程と、半導体メサ14及びマーク用メサをInP埋込領域28で埋め込む工程と、マーク用メサ及びその周辺のInP埋込領域28をエッチングする第2のエッチング工程とを行う。第2のエッチング工程の際に、InPを選択的にエッチングすることで、マーク用メサの一部を残存させてアライメントマーク50を形成する。

(もっと読む)

不透明なゲート層の位置合わせ用マーカ、このようなマーカの製作方法、及びリソグラフィ機器でのこのようなマーカの使用

【課題】順に繰り返して配置されたライン要素及びトレンチ要素を含むマーカ構造を製作する方法を提供すること。

【解決手段】この方法は、トレンチ要素に二酸化シリコンを充填し、マーカ構造を平坦化するステップを含む。半導体表面上で犠牲酸化物層を成長させ、ライン要素の第1サブセットを、ドーパント種を含むイオン注入ビームに露出させて、この第1サブセットをドープし、そのエッチング速度を変化させる。この基板をアニールしてドーパント種を活性化させ、半dの歌い表面をエッチングして犠牲酸化物層を取り除き、第1サブセットを第1レベルの高さにし、第1サブセットが、第1サブセットと異なるマーカ構造表面部分の第2レベルと異なる第1レベルを有するようにトポロジーを生成する。

(もっと読む)

半導体装置の製造方法及び合わせマークの形成方法、半導体装置

【課題】合わせマークのサイズが大きい場合でもその異常酸化を防止できるようにした半導体装置の製造方法及び合わせマークの形成方法、半導体装置を提供する。

【解決手段】基板1から第3層間絶縁層9の上面に至るプラグ電極を第1プラグ電極5と第2プラグ電極13とに分け、第1プラグ電極5と第2プラグ電極13とを繋ぐと共に、第1層間絶縁層3をエッチングストッパ層として使用し、第1層間絶縁層3上に合わせマーク15を形成する。開口部Hを浅く形成することができるので、開口部H内をW層11で埋め込むことが容易となり、合わせマーク15を覆う酸化バリア層17の段差被覆性を向上させることができる。

(もっと読む)

アライメント方法、アライメントマーク認識装置およびアライメント検査ファイルの作成方法と検査装置

【課題】作製が簡単であり、認識が容易であるアライメントマークを用いたアライメント方法を提供する。

【解決手段】アライメントマークは、暗部を形成する凹凸領域と、明部を形成する平坦領域からなる。凹凸領域は、アライメントマーク認識装置が前記アライメントマークを認識するとき、凹凸領域を形成する凹部または凸部のエッジ部が暗く認識される幅の2倍と、前記アライメントマーク認識装置の認識限界幅の合計幅以下の幅を有する。平坦領域は、アライメントマーク認識装置がアライメントマークを認識するとき、平坦領域の両側に形成されるエッジ部が暗く認識される幅を除きアライメントマーク認識装置が認識するために必要とする幅以上の幅を有する。

(もっと読む)

半導体装置の製造方法

【課題】 精度の高いマスクのアライメントを行うことができる半導体装置の製造方法を実現する。

【解決手段】 半導体基板10の基板面10aに第1アライメントマーク11を形成し、第1アライメントマーク11の上方にその形状に対応した第2アライメントマーク13が形成されるエピタキシャル層12を基板面10a上に形成する。続いて、KOH溶液を用いてエピタキシャル層12をエッチングすることにより、第2アライメントマーク13が基板面10aである(110)面と異なる方位の(111)面に沿って優先的にエッチングされるので、エピタキシャル層12の表面と第2アライメントマーク13との境界を明確にすることができる。これにより、露光装置により第2アライメントマーク13の位置及び形状を正確に認識することができ、精度の高いマスクのアライメントを行うことができる。

(もっと読む)

半導体素子の製造方法

【課題】オーバーレイバーニア形成時に半導体基板に段差を形成し、段差の形態が維持され得るように上部に積層膜を形成してハードマスクを形成することで、ドレインキーオープンマスク工程とドレインキーオープンエッチ工程を別途設けるずとも、オーバーレイバーニアの形成が可能な半導体素子の製造方法を提供する。

【解決手段】ソースコンタクトプラグ及びドレインコンタクトプラグを形成する半導体素子100を製造するに際して、その半導体基板100の一部をエッチングして段差を形成することでオーバーレイバーニアを形成し、上記段差が維持されるように上記段差の上部にハードマスク108を形成する。ハードマスク108がたとえば光を透過しない不透明な膜の場合でも、オーバーレイバーニアを別途形成する工程を追加せずとも、工程が単純化し、また工程時間が短縮されて製造コストの低減に有効であり、素子の信頼性も向上する。

(もっと読む)

1 - 20 / 43

[ Back to top ]