Fターム[5F048AA03]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 目的 (7,359) | ラッチアップ防止、寄生バイポーラ防止 (198)

Fターム[5F048AA03]に分類される特許

1 - 20 / 198

半導体装置

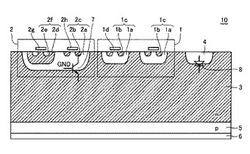

【課題】本発明は、半導体装置に負電流が流れた場合でも、回路素子を構成する深い半導体層の電位に対して、半導体基板の電位が低くなるのを抑制して寄生素子を作動させず、半導体装置の誤動作を防止する。

【解決手段】本発明は、n型の半導体基板3と、半導体基板3の一面に形成し、接続する負荷に電力を供給する電力素子1と、n型のソース・ドレイン領域を有するMOSトランジスタ2cを少なくとも1つ含む回路素子2と、電力素子1および回路素子2に対し独立して配置したp型の半導体層4と、半導体基板3および半導体層4と接続する外部回路とを備えている。外部回路は、電源と、電源に一端を接続する抵抗素子と、抵抗素子の他端にアノード電極を接続し、カソード電極をGND接地するダイオードとを有し、抵抗素子の他端に半導体層4を接続する。

(もっと読む)

半導体装置

【課題】IGBT終端部でのリカバリ破壊を防ぎ、ダイオードのスナップバックを抑制することができる半導体装置を提供する。

【解決手段】N−型のドリフト層30の上に形成されたP型のチャネル層31を含む半導体基板32のうちチャネル層31側の一面33とは反対側の他面34側に、P++型のコレクタ層53とN++型のカソード層54とが同じ階層に形成されている。そして、P++型のコレクタ層53がトレンチ35の延設方向における表面IGBT専用領域10および表面ダイオード専用領域20の周辺部25にそれぞれ設けられていることによりN++型のカソード層54は四角形状にレイアウトされている。また、P++型のコレクタ層53がエミッタ領域39の終端部39aから距離aを半径とする円形状に設けられていることにより当該四角形状の角部が窪んだ形状にレイアウトされている。

(もっと読む)

半導体集積回路装置

【課題】半導体集積回路装置において、I/Oセルの高さを低減すると同時に幅の増大を防ぐことでI/Oセルの占める領域の面積を削減すること。

【解決手段】レベルシフタ回路、I/Oロジック回路およびI/Oバッファ回路を含むI/Oセルがコア領域の周囲に配置された半導体集積回路装置であって、I/Oロジック回路が配置されたI/Oロジック領域、および、I/Oバッファ回路が配置されたI/Oバッファ領域は、I/Oセルに対するパッドが配置された領域と重なり合うとともに、コア領域の辺に平行な方向に互いに並んで配置されている。

(もっと読む)

半導体装置

【課題】チップ面積を増大させずにスナップバック現象を抑制することのできる、IGBTと他の半導体素子とが一体化して配置された半導体装置を提供する。

【解決手段】IGBTとドリフト層を有する他の半導体素子とを備えた半導体装置であって、IGBTのドリフト層と他の半導体素子のドリフト層とが互いに接しており、IGBTのエミッタ層と他の半導体素子のドリフト電界を発生させる電圧が印加される一方の極性層とが互いに導電的に接続されており、IGBTのコレクタ層と他の半導体素子の他方の極性層とが互いに導電的に接続されており、IGBTのドリフト層の他の半導体素子のドリフト層との境界から離れた領域に絶縁層を介して対向する領域をドリフト方向に沿って延伸し、Nチャネル型IGBTではコレクタ側からエミッタ側に向けて電流が流され、Pチャネル型IGBTではエミッタ側からコレクタ側に向けて電流が流される配線部が設けられている。

(もっと読む)

ESD保護検証装置

【課題】 寄生バイポーラの生成を抑制しつつ、開発遅延を効果的に防止できるESD保護検証装置を提供する。

【解決手段】 回路図データを受け付ける回路図データ取得手段11aと、回路図データから外部端子を抽出する外部端子抽出手段11bと、回路図データからESD保護素子を抽出するESD保護素子抽出手段11cと、寄生バイポーラの発生する可能性のある2つの素子間の関係を規定した第1判定条件に基づき、第1判定条件を満たすESD保護素子を対象素子として設定する第1判定手段11dと、配置配線処理において、寄生バイポーラの発生しないように設定されたレイアウト条件を満たすように対象素子の配置処理を実行して、レイアウトデータを作成するレイアウト作成手段11eと、レイアウトデータを出力するレイアウトデータ出力手段11fと、を備える。

(もっと読む)

金属酸化物半導体出力回路およびそれを形成する方法

【課題】金属酸化物半導体(MOS)出力回路とその形成方法の提供。

【解決手段】第一パッド61と、ゲート、第一の供給電圧に電気的接続のソース、ドレインを含む基板で第一型の第一MOSトランジスタ62と、ゲート、制御信号を受信する構成のソース、第一MOSトランジスタのゲートに電気的接続のドレイン、本体を含む基板で第一型と反対の第二型の第二MOSトランジスタ65と、バイアス信号を受信する構成のゲート、第二供給電圧に電気的接続のドレイン、第二MOSトランジスタのソースに電気的接続のソース、第一参照電圧に電気的接続の本体を含む基板で第一型の第三MOSトランジスタ66とを含み、第二MOSトランジスタの本体は第三MOSトランジスタのソースに電気的接続、一時的な信号イベントの第一パッド上の受信の場合、第二MOSトランジスタのドレインから第二供給電圧まで第二MOSトランジスタの本体を流れる電流を妨げる集積回路。

(もっと読む)

ガードバンドセル及びガードバンド

【課題】電源供給が遮断されるIO領域が存在する場合でも、ランダムロジック領域内でのラッチアップの発生を防止するガードバンドセル及びガードバンドを提供すること。

【解決手段】本発明の一態様に係るガードバンドセル11は、NウェルNW1を有する。また、本発明の一態様に係るガードバンドセル11は、NウェルNW1の上に形成された、Nウェル層と同じ導電型であるN型ガードバンド拡散層NGB1を有する。N型ガードバンド拡散層NGB1は、十分な低抵抗の配線により、ランダムロジック領域2の電源電位と接続される。

(もっと読む)

埋め込みガードリング及び耐放射線性分離構造並びにその製造方法

【課題】大量の商業マイクロエレクトロニクスメーカーがアクセスし易い最先端の基礎設備を使用して、高性能且つ費用対効果に優れた耐放射線性集積回路(RHICs)を提供する。

【解決手段】様々な形式の放射線エネルギーによって引き起こされる有害な影響を減少し、又は排除するために、従来の設計及びプロセスを使用する一方で特殊構造を含んで半導体デバイスを作成する。このような半導体デバイスは本願で開示された1台以上の寄生的な分離デバイス、及び/又は、埋め込みガードリング構造を含む。これら新規な構造に対応する設計、及び/又は、工程ステップの導入には、従来のCMOS製作工程との互換性がある。したがって、比較的低い費用で比較的簡単に実施することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】寄生バイポーラトランジスタのゲインを低下することにより、誤動作や動作特性の変動が少ない半導体装置及びその製造方法を得る。

【解決手段】シリコン層3の上面上には、シリコン酸化膜6が部分的に形成されている。シリコン酸化膜6上には、ポリシリコンから成るゲート電極7が部分的に形成されている。ゲート電極7の下方に存在する部分のシリコン酸化膜6は、ゲート絶縁膜として機能する。ゲート電極7の側面には、シリコン酸化膜8を挟んで、シリコン窒化膜9が形成されている。シリコン酸化膜8及びシリコン窒化膜9は、シリコン酸化膜6上に形成されている。ゲート長方向に関するシリコン酸化膜8の幅W1は、シリコン酸化膜6の膜厚T1よりも大きい。

(もっと読む)

半導体装置

【課題】同一基板上に混載された他の素子の誤動作を抑制できる半導体装置を提供する。

【解決手段】半導体装置は、p形半導体層12と、n形のソース領域13と、絶縁体23と、n形半導体領域20と、n形のドレイン領域14と、p形のチャネル領域12aと、ゲート絶縁膜15と、ゲート電極16と、ソース電極18と、ドレイン電極19と、電極21とを備える。前記絶縁体は、前記p形半導体層の表面から前記p形半導体層の厚み方向に延びて形成されたトレンチt1内に設けられている。前記n形半導体領域は、前記ドレイン領域と前記絶縁体との間の前記p形半導体層の表面に設けられる。前記電極は、前記n形半導体領域に接続される。

(もっと読む)

半導体装置

【課題】出力トランジスタの形成領域から他の素子の形成領域への電子の移動を抑制する効果が高く、素子の誤動作を抑制できる半導体装置を提供する。

【解決手段】半導体基板SUBと、1対の注入元素子DRと、アクティブバリア構造ABと、p型接地領域PGDとを備える。半導体基板SUBは主表面を有し、かつ内部にp型領域を有する。1対の注入元素子DRは、p型領域上であって主表面に形成される。アクティブバリア構造ABは、主表面において1対の注入元素子DRに挟まれる領域に配置される。p型接地領域PGDは、主表面において1対の注入元素子DRに挟まれる領域を避けて1対の注入元素子DRおよびアクティブバリア構造ABよりも主表面の端部側に形成され、かつp型領域に電気的に接続された、接地電位を印加可能な領域である。p型接地領域PGDは、1対の注入元素子DRに挟まれる領域と隣り合う領域において分断されている。

(もっと読む)

半導体装置およびその製造方法

【課題】工程が簡単で、よりラッチアップに強いCMOS構造を得る。

【解決手段】1×1018cm−3から1×1019cm−3の高不純物濃度の半導体基板2を用い、CMOS構造のP型ウェル4とN型ウェル5の境界に設けられた溝分離部13の先端部分がその高不純物濃度領域に達する(エピタキシャル層3を貫通して半導体基板2の領域に至る)ように深く形成することにより、従来のように溝分離部13よりも更に深い領域(溝分離部13の下側)を電子が通過することなく、従来のようにウェル領域内にN+埋め込み層やP+埋め込み層を基板深く埋め込む必要もなく、簡便な方法で、よりラッチアップに強いCMOS構造を得ることができ、コスト性能の両方に優れた半導体装置1を得ることができる。

(もっと読む)

半導体装置

【課題】半導体基板に向かって流れ込む回生電流又は寄生バイポーラトランジスタのオン電流を、チップサイズを増大させることなく低減できるLDMOSトランジスタの実現が課題となる。

【解決手段】N+型ドレイン層13等が形成されたN型エピタキシャル層5からなるN型層5aを、N型エピタキシャル層5の表面からN+型埋め込み層2まで延在するP型ドレイン分離層6で取り囲む。P型ドレイン分離層6とP型素子分離層3に囲まれたN型エピタキシャル層5からなるN型層5bにその表面から内部に延在するP型コレクタ層7を形成する。これにより第1導電型のドレイン分離層6をエミッタ、前記第2導電型の分離層5bをベース、前記コレクタ層7をコレクタとする寄生バイポーラトランジスタを形成しサージ電流を接地ラインに流す。

(もっと読む)

半導体集積回路のESD保護素子およびそのESD保護回路

【課題】電源電圧以下の維持電圧Vhでも良好なESD保護を行う。

【解決手段】半導体集積回路のESD保護回路11は、電位端子とグランド電位間に、スナップバック動作を持つ第1のESD保護素子1としてのggMOSトランジスタと、スナップバック動作を持つESD保護素子1のスナップバック動作電圧Vt1に対して、低いブレークダウン電圧Vrを持ち、かつ高い破壊電圧Vt2を持つ第2のESD保護素子2としてのダイオードとが並列に接続されている。

(もっと読む)

半導体集積回路及び半導体集積回路装置

【課題】従来技術と比較して占有面積が小さく、かつ基板電流が流れる経路の抵抗を低く抑え、寄生バイポーラトランジスタの動作を抑制することができる半導体集積回路及び半導体集積回路装置を提供する。

【解決手段】p型半導体基板10に形成されたドレイン領域D1、ソース領域S1、及びp型活性領域Bと、ドレイン領域D1とソース領域S1との間に形成されたゲート電極TG1と、ドレイン電極TD1と、ソース電極TS1と、基板電極TB1とを備えたNMOSトランジスタMN1と、ソース領域S1とp型活性領域Bとの間に形成されたドレイン領域D2及びソース領域S2と、p型活性領域Bと、ドレイン領域D2とソース領域S2との間に形成されたゲート電極TG2と、ドレイン電極TD2と、ソース電極TS2と、基板電極TB2とを備えたNMOSトランジスタMN2とを備え、NMOSトランジスタMN2は、基板電極TB1とソース電極TS1との間に接続される。

(もっと読む)

半導体装置及びその製造方法

【課題】小さいサイズでラッチアップの発生を防止できる半導体装置を提供する。

【解決手段】第1導電型の半導体基板1と、前記半導体基板内に形成された第1導電型の第1ウェル領域4と、前記半導体基板内に形成され、第1ウェル領域と隣り合う領域に配置された第2導電型のエピタキシャル領域2と、前記エピタキシャル領域内下方の領域に形成され、前記エピタキシャル領域よりも不純物濃度が高い第2導電型の埋め込み領域6と、第1ウェル領域と前記エピタキシャル領域及び前記埋め込み領域との境界に形成されたトレンチ8と、第1ウェル領域上に形成され、第2導電型のソース及びドレイン領域を有する第1半導体素子と、前記エピタキシャル領域上に形成され、第1導電型のソース及びドレイン領域を有する第2半導体素子と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】IGBT形成領域とその制御回路等形成領域とをPN接合分離法で分離し、且つIGBTからの漏れ電流が発生せず、制御回路等のCMOSトランジスタがラッチアップ等することのない高品質の半導体装置を実現する。

【解決手段】P型半導体基板1上に多層からなるN型エピタキシャル層3等を形成する。該N型エピタキシャル層3等をP+型分離層13等によりIGBT形成領域50と制御回路等形成領域40に分離する。該IGBT形成領域50の最下層の前記N型エピタキシャル層3と前記P型半導体基板1の双方に延在するN+型埋め込みガード層2を形成する。また該N+型埋め込みガード層2の端部と接続し前記エピタキシャル層3等の表面まで延在するN+型ガードリング9等を形成する。前記N+型埋め込みガード層2と該N+型ガードリング9等に囲まれた前記エピタキシャル層3等にIGBTを形成する。

(もっと読む)

電力用半導体装置

【課題】消費電力を低減することができる電力用半導体装置を得る。

【解決手段】高耐圧ダイオードDBによりコンデンサCBを充電してハイサイド駆動回路10aの駆動電圧を得る電力用半導体装置において、高耐圧ダイオードDBは、P−型半導体基板12と、P−型半導体基板12の表面に設けられたN型カソード領域14と、N型カソード領域14内に設けられたP型アノード領域16と、P型アノード領域16内に設けられたP+型コンタクト領域20及びN+型コンタクト領域22と、N型カソード領域14に接続されたカソード電極24と、P+型コンタクト領域20及びN+型コンタクト領域22に接続されたアノード電極26とを有する。

(もっと読む)

交流スイッチ

【課題】高耐圧の用途に適用可能な交流スイッチ(半導体リレー)を提供する。

【解決手段】交流スイッチ1は、ソース(S)同士を接続した第1化合物半導体MOSFET11および第2化合物半導体MOSFET12と、第1化合物半導体MOSFET11のドレイン(D)に接続された第1出力端子13と、第2化合物半導体MOSFET12のドレイン(D)に接続された第2出力端子14とを含む。交流スイッチ1は、オフ時の第1出力端子13および第2出力端子14の間の耐圧が400V以上(より好ましくは600V以上)であり、オン時の第1出力端子13および第2出力端子14の間の抵抗が20mΩ以下(より好ましくは10mΩ以下)である。

(もっと読む)

半導体装置

【課題】キャリアのライフタイム制御に関わらず、寄生バイポーラトランジスタの動作を抑制し、耐量を向上させることができる構造の半導体装置を提供する。

【解決手段】ダイオード構造が形成された領域において、n-型ドリフト層1の裏面側に、p+型不純物領域2だけでなく部分的にn+型不純物領域3を形成する。これにより、p+型不純物領域2の幅が狭くなり、その結果、p+型不純物領域2のうちn+型不純物領域3との境界部から最も離れる場所までの距離が短くなる。したがって、n-型ドリフト層1の内部抵抗が小さくなることでバイアス電圧が小さくなり、寄生バイポーラトランジスタの動作を抑制することが可能となる。よって、キャリアのライフタイム制御に関わらず、寄生バイポーラトランジスタの動作を抑制し、耐量を向上させることが可能となる。

(もっと読む)

1 - 20 / 198

[ Back to top ]