Fターム[5F048BB11]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 材料 (10,904) | ゲート絶縁膜材料 (1,843)

Fターム[5F048BB11]に分類される特許

1,841 - 1,843 / 1,843

フロントゲート型SOI−MOSFETの製造方法

【課題】ソース/ドレイン拡張とフロントゲート(front gate)に自己整合させたバックゲートを含む、FD型SOI−CMOSデバイスの製造方法に関する。

【解決手段】

SOI−CMOS技術は、ポリシリコン、即ちポリSiバックゲートは、フロントゲート・デバイスの閾値電圧を制御するために使用され、nMOS及びpMOSバックゲートは、互いに独立に、及びフロントゲートと独立に、スイッチされる。

特に、バックゲートが、デバイスのフロントゲート及びソース/ドレイン拡張に自己整合されたバックゲートFD型CMOSデバイスの製造方法を提供する。バックゲートFD型CMOSデバイスは、SIMOX又は結合SOI−ウエハ、ウエハボンディングと薄膜化、ポリSiエッチング、LP−CVD、機械化学研磨(CMP)を用いて製造される。

(もっと読む)

三次元集積回路構造及びこれを作る方法

垂直方向の半導体装置は、電気装置そして/または相互接続を含む分離して作られた基板に付加される。多くの垂直方向の半導体装置は物理的に互いに分離され、そして同一半導体本体又は半導体基板内には配置されない。多くの垂直方向の半導体装置は取り付けられた後に個別のドープされたスタック構造を生成するため、エッチングされた数個のドーピングされた半導体領域を含む薄い層として分離して作られた基板へ付加される。あるいは多くの垂直方向の半導体装置が分離して作られた基板に取り付けるのに先立ち製作される。ドープされたスタック構造は、ダイオードキャパシタ、n‐MOSFET、p‐MOSFET、バイポーラトランジスタ、及び浮遊ゲートトランジスタのベースを形成する。強誘電体メモリー装置、強磁性体メモリー装置、カルコゲニド位相変更装置が分離して作られた基板と連結して使用するために、堆積可能なアッド‐オン層に形成される。堆積可能なアッド‐オン層は相互接続ラインを含む。

(もっと読む)

(もっと読む)

デュアルメタルゲートデバイスの形成方法

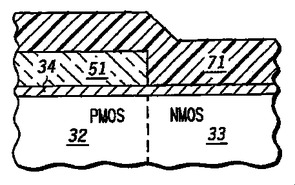

異種金属により形成されるデュアルメタルゲートを備えるMOSトランジスタ(10)を形成する方法を提供する。HfO2のようなゲート誘電体(34)を半導体基板(31)の上に堆積させる。次に、犠牲層(35)をゲート誘電体(34)を覆うように堆積させる。犠牲層(35)をパターニングして、基板(31)の第1領域(32)(例えばpMOS)の上のゲート誘電体(34)が露出し、かつ基板(31)の第2領域(33)(例えばnMOS)の上のゲート誘電体(34)が犠牲層(35)によって保護されたままになるようにする。第1ゲート導体材料(51)を残りの犠牲領域(35)の上に、かつ露出したゲート誘電体(34)の上に堆積させる。基板(31)の第2領域(33)の上の第1ゲート導体材料(51)がエッチングにより全て除去されるように第1ゲート導体材料(51)をパターニングする。第1ゲート導体材料(51)を取り除く際に、第2領域(33)上の犠牲層(35)は、下層の誘電体材料(34)にダメージが加わるのを防止するように機能することができる。  (もっと読む)

(もっと読む)

1,841 - 1,843 / 1,843

[ Back to top ]