Fターム[5F048CC12]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 保護回路の構成 (4,292) | 定電圧・定電流回路を設けたもの (12)

Fターム[5F048CC12]に分類される特許

1 - 12 / 12

半導体装置

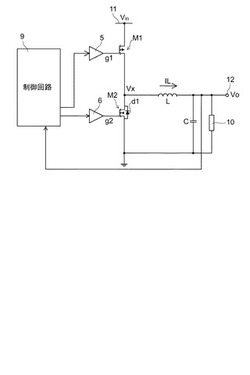

【課題】信頼性に優れた半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、入力電圧ラインと誘導性負荷との間に接続される第1のスイッチング素子と、誘導性負荷と基準電圧ラインとの間に並列接続される第2のスイッチング素子とを備えている。0<(第2のスイッチング素子の閾値電圧)<(第2のスイッチング素子の内蔵ダイオードのオン電圧)である。第2のスイッチング素子のゲート電圧が基準電位の場合に、第1のスイッチング素子と第2のスイッチング素子との接続点の電位が、−(第2のスイッチング素子の閾値電圧)より大きくなると第2のスイッチング素子はオフし、接続点の電位が、−(第2のスイッチング素子の閾値電圧)より小さくなると第2のスイッチング素子はオンする。

(もっと読む)

過電流保護回路

【課題】入力電源電圧の動作保証範囲が大きいとしても当該電圧変動の影響を抑制して正常に過電流保護を図るようにした過電流保護回路を提供する。

【解決手段】支持基板10が第1半導体層11および第2半導体層12を絶縁層13で挟んで構成されている。第1半導体層11上には絶縁膜14を介してフィールドプレート抵抗膜20が形成されている。可変電流源ISが、ゲート電極19からドレイン電極17にかけて絶縁膜14上に沿って形成されたフィールドプレート抵抗膜20(フィールドプレート抵抗R1およびR2)に生じるノードN1の電圧に応じて出力電流値を変更してセンス抵抗Rsの検出電圧V2を補正する。

(もっと読む)

半導体装置の製造方法

【課題】信頼性と電気的特性の確保を両立した半導体装置を提供する。

【解決手段】同一の半導体基板1上に形成されたパワーMOSFETと保護回路を備える。パワーMOSFETがトレンチゲート縦型PチャネルMOSFETであって、そのゲート電極6の導電型をP型とする。また、保護回路がプレーナゲート横型オフセットPチャネルMOSFETを備え、そのゲート電極10の導電型をN型とする。これらゲート電極6とゲート電極10は別工程で形成される。

(もっと読む)

半導体集積回路装置

【課題】半導体集積回路装置のESD耐量を向上する。

【解決手段】半導体集積回路装置70には、電源回路1、内部回路2、電流源3、2入力NAND回路4、コンデンサC1、ダイオードD1、出力トランジスタMDT1、端子Pin、端子Pvcc、端子Pvo、及び端子Pvssが設けられる。電流源3、コンデンサC1、及び2入力NAND回路4は、端子PVoに(+)ESDが印加されたとき、2入力NAND回路4の出力側のノードN3の信号レベルを“High”レベルにして、出力トランジスタMDT1をオンさせてESDの電荷を低電位側電源Vss側に逃がす。

(もっと読む)

静電破壊保護回路

【課題】MOS型トランジスタの静電保護回路が必須であり、一般的には被保護端子に比較的大きなMOSトランジスタのドレインを接続し、第一の電源にゲートとソースを接続していたが、しかし、プロセスの微細化に伴い、年々その閾値が低下しており、応用によっては高温時のリーク量が無視できない状況になってきた。

【解決手段】MOS型トランジスタとPN接合からなる静電破壊保護回路において、MOS型トランジスタのドレインを被保護端子に接続し、ゲートを第一の電源端子に接続するとともに、ソースをPN接合を順方向に介して第一の電源端子に接続する。

(もっと読む)

静電破壊保護回路及びこれを備えた半導体集積回路装置

【課題】本発明は、電力供給を要することなく、静電パルス等の印加によってオープンドレイン形式の出力トランジスタが意図せずオンしてしまうことを防止し、これを静電破壊から保護することが可能な静電破壊保護回路を提供することを目的とする。

【解決手段】本発明に係る保護回路は、アノードがゲート信号入力端に接続され、カソードが出力トランジスタN1のゲートに接続されたダイオードD1と;一端が前記ゲート信号入力端に接続され、他端が接地端に接続された抵抗R1と;エミッタが出力トランジスタN1のゲートに接続され、ベースが抵抗R1の一端に接続され、コレクタが接地端に接続されたpnp型バイポーラトランジスタQp1と;を有して成る構成とされている。

(もっと読む)

デバイス保護システム、デバイス保護方法、微小電子回路システム、トリクル電流設定方法(デバイスのストレスを避ける方法)

【課題】高電圧電源を含む微小電子回路内で動作する脆弱なデバイスを高電圧による過剰なストレスから保護するシステムを提供すること。

【解決手段】このシステムは、出力アップ中、出力ダウン中、および多電源システムの低電圧電源がないときに、脆弱なデバイスが故障するのを防ぐ。このシステムは、回路の出力アップ、回路の出力ダウン、および低電圧電源がないときを検出し、検出した後で制御信号を生成するように構成された低電圧電源検出回路を備える。このシステムはさらに、回路の出力アップ中、回路の出力ダウン中、および低電圧電源がないときに、低電圧電源検出回路から受け取った制御信号に応答してトリクル電流を提供して脆弱なデバイスの導電チャネルを維持するように構成された制御型電流ミラー・デバイスを備える。

(もっと読む)

半導体装置

【課題】 静電保護回路のトリガ電流が流れる経路の寄生容量を小さくし、これにより当該静電保護回路の誤動作を防止する。

【解決手段】 本発明による半導体装置は、P型半導体基板1に形成されたNウェル5と、Nウェル5に形成されたN+拡散層6及びP+拡散層7と、P型半導体基板1のNウェル5以外の部分に形成されたN+拡散層8及びP+拡散層9と、トリガ回路として機能するNMOSトランジスタ13とを備えている。P+拡散層7は、I/Oパッド10に接続され、P+拡散層9は、接地端子12に接続されている。NMOSトランジスタ13は、I/Oパッド10にサージが印加されたとき、Nウェル5からトリガ電流を引き出す役割をする。NMOSトランジスタ13は、抵抗素子31を介してN+拡散層6に接続されている。

(もっと読む)

半導体装置

【課題】 静電保護回路と終端回路を小面積で実現可能な半導体装置を提供する。

【解決手段】 信号端子INから入力バッファBufに至る信号ノードND1と電源電圧ノードVDDとの間に静電保護機能を備えたPMOSトランジスタMP1を設け、更に、PMOSトランジスタMP1のゲートに参照電圧Vrefpを供給する電圧生成回路VG_pを設け、電圧生成回路VG_pによって参照電圧Vrefpを制御し、PMOSトランジスタMP1のソース−ドレイン間の抵抗値を設定する。これによって、PMOSトランジスタMP1は、静電保護機能に加え、信号端子INに接続される伝送線路等の特性インピーダンスに応じて抵抗値を設定可能な終端抵抗として機能させることが可能になる。

(もっと読む)

パワー半導体デバイス

垂直絶縁ゲート電界効果パワー・トランジスタ(3)は、2つのトランジスタ・セル(TC3)の間毎の境界において周辺ゲート構造(G31,G32)を有する複数の並列のトランジスタ・セル(TC3)を有する。ゲート構造(G31,G32)は、独立して動作可能となるように互いに絶縁された第1(G31)および第2(G32)のゲートを含む。第1のゲート(G31)は、トレンチ・ゲート(21,22)であり、第2のゲート(G32)は、少なくとも絶縁平面状ゲート部分(13,14)を有する。第1(G31)および第2(G32)のゲートが同時に動作することによって、デバイス(3)のソース領域(16)とドレイン領域(12)の間に伝導チャネル(23c,23b)が形成される。デバイス(3)は、トレンチ・ゲート・デバイスのオン状態抵抗値に近づくオン状態抵抗値を有し、スイッチング性能がDMOSデバイスより良好であり、安全動作領域がトレンチ・ゲート・デバイスより良好である。デバイス(3)は、安定化出力電圧を供給するための回路構成(50)(図14)中でロー側パワー・トランジスタ(6)と直列に接続されたハイ側パワー・トランジスタとすることができる。デバイス(3)は、負荷(L)に電流を供給するための回路構成(60)(図15)中でスイッチとすることもできる。これらの回路構成(50,60)は、第1のゲート(G31)用の電極(G311)に、供給される固定電位を加えるための端子(Vcc,VF)と、第2のゲート(G32)用の電極(G321)に変調電位を加えるためのゲート・ドライバ回路(573、673)とを含む。  (もっと読む)

(もっと読む)

静電気放電に対する保護回路及びその動作方法

ICの高電圧耐性I/O回路と共に使用する為のESD保護回路(201)である。この回路は、I/Oパッドから相対的に小さいブースト電圧バス(BOOST:バス)への小型のESDダイオード(217)を設けることで実現できる。このブーストバスを使用して、トリガ回路(203)に電力を供給する。このトリガ回路の電流消費は最小なので、ESDの際にこの経路に流れる電流はほんのわずかである。ダイオードの電圧は降下するが、I/Oパッドからトリガ回路(203)へのIR電圧降下はわずかで済む。トリガ回路(203)が相対的に大きいカスケード接続されたクランプ型NMOSFET(207、209)を制御する。最終的には、クランプ型NMOSFETの両方のゲート‐ソース間電圧(VGS)が高まるので、カスケード接続されたクランプ型NMOSFET(207、209)の導電性が高まる。これにより、NMOSFET(207、209)の各々のオン抵抗が小さくなり、よってESD性能が改善し、強固なESD保護回路の実装に要するレイアウト面積が小さくなる。  (もっと読む)

(もっと読む)

負電圧のスイングに対して耐性のある入力段

負の信号スイングを有する入力信号(s(t))を受け取るための信号入力端(1)に接続可能なレベル・シフタ(15)を備える装置(10)。レベル・シフタ(15)は、正の信号スイングを有する出力信号(r(t))を提供するために、入力信号(s(t))のDCシフトを提供する。レベル・シフタ(15)は、第1の入力端(11)、第2の入力端(12)、および出力端(13)を有する増幅器(17)を備える。第1のコンデンサ(C1)、第2のコンデンサ(C2)、基準電圧源(16)、およびスイッチとして働くトランジスタ(14;74)は以下のように回路網に構成されている。すなわち、第1のコンデンサ(C1)が信号入力端(1)と第1の入力端(11)との間に配置され、第2のコンデンサ(C2)が出力端(13)と第1の入力端(11)との間のフィードバック・ループ(18)中に配置され、基準電圧源(16)が第2の入力端(12)に接続されている。トランジスタ(14)は、第2のコンデンサ(C2)を橋絡する枝路(19)中に配置され、それによって、レベル・シフタ(15)が時々リセットされることを可能にするために、制御信号(CNTRL)がトランジスタ(14)のゲート(14.1)に印加可能になっている。  (もっと読む)

(もっと読む)

1 - 12 / 12

[ Back to top ]