Fターム[5F048CC17]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 保護回路の構成 (4,292) | 保護対象 (863)

Fターム[5F048CC17]の下位に属するFターム

MOSIC (490)

CMOSIC (327)

Bi−MOS(Bi−CMOS)IC (37)

Fターム[5F048CC17]に分類される特許

1 - 9 / 9

半導体装置

【課題】低消費電力化及び回路面積の削減を図れるようにした半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、電源端子と接地端子の間に接続されたMOSトランジスタと、MOSトランジスタのドレインとゲートの間に接続された第1のダイオードと、MOSトランジスタのドレインとゲートの間に第1のダイオードと互いの順方向が逆向きに直列に接続された第2のダイオードと、MOSトランジスタのドレインとゲートの間に第1及び第2のダイオードと直列に接続されたキャパシタとを備えている。

(もっと読む)

保護素子及び半導体装置

【課題】半導体素子を保護する保護素子を備え、静電破壊が抑制され、信頼性の高い半導体装置を提供する。

【解決手段】半導体装置1は、チャネル層105とキャップ層112とを含む半導体積層体113と、半導体積層体113上に形成された下部電極213と上部電極216とを有する少なくとも1つの半導体素子1Xと、半導体素子1Xと共通の半導体積層体113を有し、半導体素子1Xを保護する少なくとも1つの保護素子1Yとを備えたものである。保護素子1Yは、キャップ層112を厚み方向に貫通するリセス部221と、リセス部221の底面221Bから半導体積層体113内に厚み方向に形成された絶縁領域218Yと、リセス部221を挟んで両側に形成されたキャップ層112に接続された一対のオーミック電極219、220とを備えたものである。

(もっと読む)

半導体装置

【課題】温度検出素子の温度検出素子の静電破壊に対する耐性の向上と、測定精度の向上させることができる半導体装置を提供すること

【解決手段】半導体装置100は、温度検出素子10と、一方の端子が温度検出素子10の電流入力端子に接続される抵抗器11とをそれぞれが備え、互いに並列に接続される複数の温度検出素子列12とを備える。また、複数の温度検出素子列12の抵抗器11の他方の端子が接続される第1の外部端子14を備える。

(もっと読む)

半導体装置

【課題】薄型化及び小型化を達成しながら、外部ストレス、及び静電気放電に耐性を有する信頼性の高い半導体装置を提供することを目的の一とする。または、作製工程においても外部ストレス、又は静電気放電に起因する形状や特性の不良を防ぎ、歩留まり良く半導体装置を作製することを目的の一とする。

【解決手段】互いに対向するように設けられた第1の絶縁体及び第2の絶縁体と、対向する第1の絶縁体と第2の絶縁体との間に設けられた半導体集積回路及びアンテナと、第1の絶縁体の一表面に設けられた導電性遮蔽体と、第2の絶縁体の一表面に設けられた導電性遮蔽体とを設け、第1の絶縁体の一表面に設けられた導電性遮蔽体と、第2の絶縁体の一表面に設けられた導電性遮蔽体を電気的に接続する。

(もっと読む)

静電気保護回路

【課題】通常の入力信号の伝達に影響を与えることなく静電気保護を行う。

【解決手段】入力端子Inと、接地端子GNDと、これら端子間にゲートおよびソースを接続するNchトランジスタN1と、これら端子間を接続する静電気保護素子10aと、NchトランジスタN1のドレインとゲート間を接続する静電気保護素子20と、を備える。ここで、入力端子Inに静電気放電による電圧VESDが印加された場合、静電気保護素子10aによって吸収できない放電電流Idが静電気保護素子20およびオンとなったNchトランジスタN1のドレイン・ソース間の寄生抵抗(Rex2、Rch、Rex1)を介して接地端子GNDに流れる。寄生抵抗Rex1に放電電流Idが流れることで、NchトランジスタのB点の電位が上昇し、ゲート絶縁膜間電圧Vstressの最大値が電圧VESDに比べて減少する。

(もっと読む)

静電破壊保護回路

【課題】小型で静電耐量の高い静電破壊保護回路を提供すること。

【解決手段】本静電破壊保護回路は、入力端子、出力端子、入出力端子の何れかの端子であるPAD10と電源端子Vdd,Vssとの間に寄生抵抗R21,R22を介して第1のダイオード21,22を接続し、PAD10を介して印加された静電気を第1のダイオード21,22を介して電源端子Vdd,Vssへ流す1次静電破壊保護回路31と、PAD10と電源端子Vdd,Vssとの間に更に寄生抵抗R23,R24を介して第2のダイオード23,24を接続した2次静電破壊保護回路32とを備えて成り、2次静電破壊保護回路32の寄生抵抗R23,R24が、1次静電破壊保護回路31の寄生抵抗R21,R22より小さくされている。

(もっと読む)

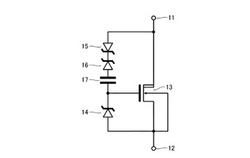

半導体装置

【課題】スイッチング回路の構成に好適な半導体装置で、高速スイッチングが可能な横型MOSトランジスタが形成されてなる半導体装置であって、スイッチング損失とサージ電圧(ノイズ)の両者を同時に抑制できる、小型で安価な半導体装置を提供する。

【解決手段】半導体基板の表層部に、横型MOSトランジスタLTa、ツェナーダイオードZDaおよび容量素子Caが形成されてなる半導体装置であって、ツェナーダイオードZDaと容量素Caが、横型MOSトランジスLTaのドレインDとゲートGの間に直列接続されてなる半導体装置101とする。

(もっと読む)

半導体集積回路装置

【課題】 ヒューズの切断面で発生する静電気放電から回路を保護する半導体集積回路を構築する。

【解決手段】 N+拡散層209とP型の半導体基板201とで、ダイオードが形成される。Nウェル206内には、P+拡散層211とN+拡散層210とでダイオード207が形成される。N+拡散層210は、電源配線208と接続される。ヒューズ204は、N+拡散層209およびP+拡散層211と接続される。

(もっと読む)

MOSFET装置および関連動作方法

本発明は、MOSFET装置(10)を提供し、このMOSFET装置(10)は、ボディダイオード構造(22)を有し、またこのボディダイオード構造(22)に関連する逆回復過渡信号を減少させるために、このボディダイオード構造(22)の逆回復中にそのMOSFET(12)のゲートに選択的に印加されるバイアス電圧を供給するように構成されるバイアス手段を供給され、このバイアス手段は、その装置(10)のゲートパス内に配置されるダイオード素子(16)を有する。  (もっと読む)

(もっと読む)

1 - 9 / 9

[ Back to top ]