Fターム[5F048CC18]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 保護回路の構成 (4,292) | 保護対象 (863) | MOSIC (490)

Fターム[5F048CC18]に分類される特許

1 - 20 / 490

半導体装置

【課題】 過電流検出による保護と、温度検出による保護とを、好適に行うことが可能な半導体装置を提供する。

【解決手段】 半導体基板を有する半導体装置であって、半導体基板が、メイン素子領域と、メイン素子領域よりも小さい電流が流れるサブ素子領域を有しており、サブ素子領域が、半導体基板を平面視したときに半導体基板の中心と重なる位置に形成されており、半導体基板上であって、半導体基板を平面視したときにサブ素子領域と重なる位置に、温度検出素子が形成されている。

(もっと読む)

半導体装置

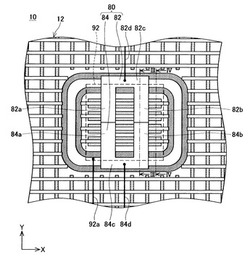

【課題】バラスト抵抗の幅を広げることなく、バラスト抵抗の許容電流量を大きくする

【解決手段】バラスト抵抗200を構成する抵抗210の少なくとも一つは、第1抵抗212及び第2抵抗214を有している。第1抵抗212は、保護素子100内で電流が流れる方向である第1の方向(図1ではX方向)に延伸している。第2抵抗214は、第1抵抗212に並列に接続され、第1の方向に延伸している。そして第2抵抗214は、第1抵抗212と同一直線上に位置している。

(もっと読む)

半導体チップ及びこれをパッケージングした半導体装置

【課題】サージ印加時における内部回路の誤動作を防止する。

【解決手段】半導体チップ(10)は、複数のパッド(P11、P12)と、複数のパッド(P11、P12)と電源ライン(15、16)との間に接続された複数の静電破壊保護素子(11H、11L、12H、12L)と、複数のパッドのうち少なくとも2つのパッド(P11、P12)に現れる印加電圧(S11、S12)が同一の論理レベルか否かを監視するサージ検出部(13)と、サージ検出部(13)の検出結果(S13)に応じてその動作が許可/禁止される内部回路(14)と、を有する。

(もっと読む)

半導体装置

【課題】静電破壊による歩留まりの低下を防ぐことができる半導体装置。

【解決手段】複数の画素を選択するための信号を走査線に供給する走査線駆動回路が、上記信号を生成するシフトレジスタを有しており、上記シフトレジスタにおいて、複数のトランジスタのゲート電極として機能する一の導電膜を複数に分割し、上記分割された導電膜どうしを、分割された導電膜と異なる層に形成された導電膜により、電気的に接続する構成を有する。上記複数のトランジスタには、シフトレジスタの出力側のトランジスタが含まれるものとする。

(もっと読む)

半導体装置

【課題】IGBT終端部でのリカバリ破壊を防ぎ、ダイオードのスナップバックを抑制することができる半導体装置を提供する。

【解決手段】N−型のドリフト層30の上に形成されたP型のチャネル層31を含む半導体基板32のうちチャネル層31側の一面33とは反対側の他面34側に、P++型のコレクタ層53とN++型のカソード層54とが同じ階層に形成されている。そして、P++型のコレクタ層53がトレンチ35の延設方向における表面IGBT専用領域10および表面ダイオード専用領域20の周辺部25にそれぞれ設けられていることによりN++型のカソード層54は四角形状にレイアウトされている。また、P++型のコレクタ層53がエミッタ領域39の終端部39aから距離aを半径とする円形状に設けられていることにより当該四角形状の角部が窪んだ形状にレイアウトされている。

(もっと読む)

半導体装置

【課題】オン抵抗を増大させることなく、ゲート−ソース間のESD耐量を向上させることのできる半導体装置を提供すること。

【解決手段】ポリシリコンゲート層を利用して形成したツェナーダイオードをESD耐量を向上させるために、並列接続させる構造を有する半導体装置とするものであって、ストライプ状または矩形状のツェナーダイオードを並列接続させて、それぞれ活性部内部に形成する半導体装置とする。

【選択図】 図3  (もっと読む)

(もっと読む)

半導体装置

【課題】信頼性に優れた半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、入力電圧ラインと誘導性負荷との間に接続される第1のスイッチング素子と、誘導性負荷と基準電圧ラインとの間に並列接続される第2のスイッチング素子とを備えている。0<(第2のスイッチング素子の閾値電圧)<(第2のスイッチング素子の内蔵ダイオードのオン電圧)である。第2のスイッチング素子のゲート電圧が基準電位の場合に、第1のスイッチング素子と第2のスイッチング素子との接続点の電位が、−(第2のスイッチング素子の閾値電圧)より大きくなると第2のスイッチング素子はオフし、接続点の電位が、−(第2のスイッチング素子の閾値電圧)より小さくなると第2のスイッチング素子はオンする。

(もっと読む)

保護回路、及び半導体装置

【課題】ESDの影響を効果的に抑制する保護回路を提供すること。またESDの影響が効果的に抑制された半導体装置を提供すること。

【解決手段】保護回路は、少なくとも2つの保護ダイオードを有し、当該保護ダイオードを、チャネルを形成する半導体層を挟んで対向する2つのゲートを有するトランジスタで構成する。さらに当該トランジスタのゲートの一方に、固定電位が入力される構成とすればよい。

(もっと読む)

半導体装置

【課題】静電気放電が印加されたときの熱破壊を抑制すること。

【解決手段】半導体装置1の半導体活性層16には、n型領域23とp型領域26とn型の埋込み領域30が形成されている。n型領域23は、カソード電極Kに電気的に接続している。p型領域26は、アノード電極Aに電気的に接続している。埋込み領域30は、半導体活性層16のうちのp型領域26の裏面側の少なくも一部を含むように形成されており、p型領域26の裏面に接触しているとともに、不純物濃度が半導体活性層16の不純物濃度よりも濃い。

(もっと読む)

半導体装置

【課題】保護素子の異なるクランプ電圧を容易に設定して形成できる構造の保護素子を含む半導体装置を提供すること。

【解決手段】回路内部のMOS型半導体装置のゲート酸化膜を保護するための保護素子を含む半導体装置であって、該保護素子は、該MOS型半導体装置とその前段回路との間に接続される横型バイポーラトランジスタであり、該横型バイポーラトランジスタのパンチスルー耐圧をクランプ電圧として利用することを特徴とする、半導体装置。

(もっと読む)

半導体装置

【課題】大規模な変更を必要とせず開発上の負荷が小さい半導体装置を提供する。

【解決手段】High SideのIGBTにおける比(コレクタコンタクト面積/コレクタ活性面積)および比(p+領域上コンタクト面積/p+領域面積)の少なくともいずれかが、Low SideのIGBTにおける上記比よりも高い。

(もっと読む)

半導体装置

【課題】パッド下のクラックによるショート不良が抑制された半導体装置を提供する。

【解決手段】パッド開口部18aの下の層間絶縁膜16はコンタクト17で囲われているので、ワイヤボンディング時に生じたパッド開口部18aの下の層間絶縁膜16のクラックはコンタクト17の外周縁17aよりも外側に入らない。よって、クラックを通し、パッド開口部18aは、外周縁17aよりも外側のアルミやポリシリコンなどの金属膜や拡散層とショートしない。

(もっと読む)

組合せ出力バッファおよびESDダイオードデバイス

【課題】改良されたESD保護デバイスおよび該動作方法が、必要とされる。

【解決手段】集積回路ESD保護回路270は、ゲートダイオード271および出力バッファMOSFET272を含有する組合せデバイスとともに形成される。第1導電性タイプのボディタイフィンガ307は、基板301、302に形成され、複数のダイオードポリフィンガ231、232を用いて第2導電性タイプ310のドレイン領域から分離される。複数のダイオードポリフィンガ231、232は、出力バッファMOSFET272を形成する複数のポリゲートフィンガ204、205と交互配置される。

(もっと読む)

トレンチポリシリコンダイオード

【課題】シリコン内にダイオード構造を位置させた半導体製造方法を提供する。

【解決手段】トレンチポリシリコンダイオードを製造する方法は、N+(P+)型基板上にN−(P−)型エピタキシャル領域を形成すること、エピタキシャル領域内にトレンチを形成すること、さらに、前記トレンチ内に絶縁層を形成し、前記トレンチをポリシリコンで充填する。さらに、P+(N+)型ドーパントをインプラントして、前記トレンチ内に前記ポリシリコンのP+(N+)型領域を、N+(P+)型ドーパントをインプラントして、前記トレンチ内に前記ポリシリコンのN+(P+)型領域を形成しトレンチ内にポリシリコンダイオードを形成することを含み、ダイオードの一部は、トレンチの上面より低い。

(もっと読む)

半導体装置およびその製造方法

【課題】素子特性を悪化させず、アクティブ領域を終端領域に対して、簡単な方法により電気的に独立させることができ、さらには素子サイズの小型化を図ることができる半導体装置およびその製造方法を提供すること。

【解決手段】エピタキシャル層23のアクティブ領域12と終端領域11との間に、エピタキシャル層23の表面24を形成するように、当該表面24に沿って全体にわたって形成されたチャネル層26を、ゲートトレンチ28の深さD1と同じ深さD2を有するアイソレーショントレンチ39で分断する。互いに同じ深さのゲートトレンチ28およびアイソレーショントレンチ39は、同一のエッチング工程で形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】高耐圧トランジスタの低濃度不純物拡散層がコンタミネーションから保護されて、半導体装置の特性を安定化できるようにする。

【解決手段】基板1の上に、ゲート絶縁膜3a及びゲート電極4aを順次形成し、ゲート電極4aをマスクとして基板1に不純物注入を行うことにより、基板1の上部におけるゲート電極4aの側方に低濃度不純物拡散層5aを形成する。続いて、ゲート電極4aの上から該ゲート電極4aの側方を通って低濃度不純物拡散層5aの上の一部までを連続して覆うように不純物拡散抑制膜7aを形成する。続いて、ゲート電極4a及び不純物拡散抑制膜7aをマスクとして基板1に不純物注入を行うことにより、基板1の上部におけるゲート電極4aの側方に、低濃度不純物拡散層5aよりも不純物濃度が高い高濃度不純物拡散層8aを形成する。その後に、不純物拡散抑制膜7aを残存させた状態で基板1に対して加熱処理を行う。

(もっと読む)

窒化物半導体装置

【課題】ダイオード等の保護素子の外付けによる部品点数の増加及び占有面積の増大を抑えた、双方向に高いアバランシュエネルギー耐量を有する窒化物半導体装置を提供する。

【解決手段】半導体基板10は、第1のn型領域12A、第2のn型領域12Bとともにトランジスタ11を構成する。半導体基板10の裏面には、裏面電極13が接合され、また、半導体基板10の上には、HFET21が形成されている。HFET21は、AlGaN層23A及びGaN層23Bを備える半導体層積層体23と、第1のオーミック電極24A、第2のオーミック電極24B、第1のゲート電極25A、第2のゲート電極25Bにより構成されている。第1のオーミック電極24Aと第1のn型領域12A、第2のオーミック電極24Bと第2のn型領域12Bはそれぞれ電気的に接続されている。

(もっと読む)

半導体装置

【課題】Finger形状のソース電極、ドレイン電極と接続される各N+型ソース層、N+型ドレイン層を取り囲むようにP+型コンタクト層が構成される場合でも、サージ電圧印加時に各Finger部の寄生バイポーラトランジスタが均一にオンする。

【解決手段】互いに平行に延在する複数のN+型ソース層9、N+型ドレイン層8を取り囲むようにP+型コンタクト層10を形成する。N+型ソース層9上、N+型ドレイン層8上及びN+型ソース層9が延在する方向と垂直方向に延在するP+型コンタクト層10上にそれぞれ金属シリサイド層9a、8a、10aを形成する。金属シリサイド層9a、8a、10a上に堆積された層間絶縁膜13に形成されたコンタクトホール14を介して、該各金属シリサイド層と接続するFinger形状のソース電極15、ドレイン電極16及び該Finger形状の各電極を取り囲むP+型コンタクト電極17を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】装置面積を増大させることなく、保護素子を有する半導体装置を提供する。

【解決手段】P型のIII族窒化物半導体からなる第1P型層200と、第1P型層200の一部上には、ゲート絶縁膜420およびゲート電極440とが設けられている。第1P型層200内のうち、ゲート電極440の両脇には、N型のソース領域340およびドレイン領域320が設けられている。また、第1P型層200の下には、N型のIII族窒化物半導体からなる第1N型層100が設けられている。基板内には、N型のIII族窒化物半導体とオーミック接続する材料からなるオーミック接続部(たとえばN型GaN層520)が、ソース領域340および第1N型層100と接するように設けられている。また、ドレイン電極600は、ドレイン領域320および第1P型層200と接するように設けられている。

(もっと読む)

金属酸化物半導体出力回路およびそれを形成する方法

【課題】金属酸化物半導体(MOS)出力回路とその形成方法の提供。

【解決手段】第一パッド61と、ゲート、第一の供給電圧に電気的接続のソース、ドレインを含む基板で第一型の第一MOSトランジスタ62と、ゲート、制御信号を受信する構成のソース、第一MOSトランジスタのゲートに電気的接続のドレイン、本体を含む基板で第一型と反対の第二型の第二MOSトランジスタ65と、バイアス信号を受信する構成のゲート、第二供給電圧に電気的接続のドレイン、第二MOSトランジスタのソースに電気的接続のソース、第一参照電圧に電気的接続の本体を含む基板で第一型の第三MOSトランジスタ66とを含み、第二MOSトランジスタの本体は第三MOSトランジスタのソースに電気的接続、一時的な信号イベントの第一パッド上の受信の場合、第二MOSトランジスタのドレインから第二供給電圧まで第二MOSトランジスタの本体を流れる電流を妨げる集積回路。

(もっと読む)

1 - 20 / 490

[ Back to top ]