Fターム[5F064AA05]の内容

ICの設計・製造(配線設計等) (42,086) | ICの形式 (1,534) | カスタムIC (1,426) | セミカスタムIC (1,415) | 標準セル、スタンダードセル (922) | ポリセル (86)

Fターム[5F064AA05]に分類される特許

1 - 20 / 86

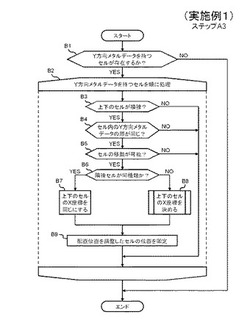

半導体集積回路のレイアウト設計方法、プログラム、及びレイアウト設計装置

【課題】チップサイズを縮小可能な半導体集積回路のレイアウト設計方法、プログラム、及びレイアウト設計装置を提供すること。

【解決手段】チップ内にY方向メタルデータを持つプリミティブセルが存在するか判定する工程(ステップB1)と、プリミティブセルが上下に隣接しているか判定する工程(ステップB3)と、各プリミティブセル内のY方向メタルデータを有する層が同じか判定する工程(ステップB4)と、各プリミティブセルのうち移動可能なスペースがあるプリミティブセルがあるか判定する工程(ステップB5)と、各判定を満たす場合に、各プリミティブセルの種類が同じか否かを判定する工程(ステップB6)と、各プリミティブセルの種類に応じてプリミティブセルのX座標の配置位置調整を行う工程(ステップB7、8)と、プリミティブセルの位置を固定する工程(ステップB9)と、を含む。

(もっと読む)

パターン密度検証方法及びプログラム

【課題】チップ全体の密度検証においてマクロセル部分での設計規則違反の判定を出さないようにすること。

【解決手段】検証エリアの内側と外側に内側補助区画と外側補助区画とをそれぞれ設定し(ステップS19)、内側補助区画のパターン占有面積に外側補助区画のパターン占有面積を加味した検証エリアのパターン密度D2が密度基準を満たすか否かを判定する(ステップS20)。

(もっと読む)

半導体装置

【課題】半導体装置のレイアウトの自由度を向上させる。

【解決手段】本発明による半導体装置は、第1行おいて、行方向に連続的に配置される第1電源供給セル20及び複数の第1セル10と、第1行に隣接する第2行において、行方向に連続的に配置され、前記第1行に隣接する複数の第2セル10とを具備する。第1電源供給セル20は、行方向に直交する第1電源配線62に接続され、第1電源配線62から供給される電圧に応じた電源電圧を、複数の第1セル10及び複数の第2セル10に供給する。第2行において、第1行に配置された第1電源供給セル20に隣接する第2セルと第1電源配線62とは、直接接続されず第1行に配置された第1電源供給セル20を介して接続される。

(もっと読む)

半導体装置及び半導体装置の補償容量の配置方法

【課題】回路セル内の領域を有効活用して十分な補償容量を確保し、電源電圧の変動を確実に抑制し得る半導体装置等を提供する。

【解決手段】本発明の半導体装置は、第1の方向に並んで配置された複数の素子を含む回路セル2と、この回路セル2の第1の方向に隣接して配置され回路セル2の電源に接続可能な補償容量C1、C2を有する基本端セル1(1a)とを備えて構成される。補償容量C1、C2を構成する拡散層10、11は、回路セル2の所定領域(素子間接続領域R1)を第1の方向に沿って延伸形成されている。また、拡散層10、11の上部にはゲート配線16、17が延伸形成されている。本発明の構成により、回路セル2の素子間接続領域R1を有効に活用しつつ、補償容量のC1、C2の容量値を増加させて電源変動の変動を確実に抑えることが可能となる。

(もっと読む)

半導体集積回路装置

【課題】チップへの回路セルの実装率を保ちつつ、微細化の進んだ半導体素子および配線の均等性を保つことのできる技術を提供する。

【解決手段】NAND回路セルを形成するnチャネル型MISFETQn2およびnチャネル型MISFETQn3のそれぞれのゲート電極4を同一ノードとし、同じ入力信号に従って同時にオン・オフ動作を行う構成とする。nチャネル型MISFETQn2およびnチャネル型MISFETQn3は隣接して配置し、電気的には直列に接続された構造とする。また、NAND回路セルを形成pチャネル型MISFETQp3およびpチャネル型MISFETQp4のそれぞれのゲート電極4を同一ノードとし、同じ入力信号に従って同時にオン・オフ動作を行う構成とする。pチャネル型MISFETQp3およびpチャネル型MISFETQp4は隣接して配置し、電気的には直列に接続された構造とする。

(もっと読む)

半導体集積回路並びにその設計装置及び設計プログラム

【課題】通常モードでの動作及びスキャンテストモードでの動作のいずれにおいても適切なタイミングで動作する半導体集積回路を提供する。

【解決手段】フリップフロップの基本回路30と、実働クロックの入力とスキャンテスト用クロックの入力とを排他的に出力端子に接続するセレクタ回路32とを含み、基本回路30のクロック端子CKinにセレクタ回路32の出力端子が接続されている回路を分割できない回路ブロック102として、回路ブロック102を組み合わせることによって半導体集積回路を構成する。

(もっと読む)

半導体集積回路及び多電源レイアウト設計方法

【課題】セルに供給される電源に依存しない自由な配置を実現し、常時通電用電源線と電源遮断用電源線を並層で構成しても、電源幹線から基準電位線への配線接続が容易な半導体集積回路を提供すること。

【解決手段】複数の回路セルを有する半導体集積回路は、当該半導体集積回路の電源幹線と、電源幹線から縞状に配線された電源配線群と、一時的に回路セルへの電源供給を遮断する電源スイッチセルと、電源スイッチセルを介して遮断用電源が供給される電源遮断対象セルと、電源スイッチセルを介さず、常時通電用電源が供給される常時通電セルと、を備える。電源配線群は、第1層メタル配線を介して電源スイッチセルと電源遮断対象セルを接続する遮断用電源供給線と、第2層メタル配線を介して電源スイッチセルと常時通電セルを接続する基準電位供給線とを含む。

(もっと読む)

半導体集積回路

【課題】レイアウトパターンに依存した基本論理セル2の特性ばらつきを抑制する。

【解決手段】論理回路の部品として機能する基本論理セル(2)と、論理回路の部品としての機能を含まないダミーセル(1、21)とを具備する半導体集積回路を構成する。基本論理セル(2)は、基板に形成される拡散層(13、14)を含むものとする。そして、拡散層(13、14)は、基本論理セル(2)が、他のセル(1、2、21)に隣接して配置されるときに、それらの境界からの距離(L3)が、第1長さとなる位置に設けられていることが好ましい。また、ダミーセル(1、21)は、基板に形成されるダミー拡散層(3、4)を備えるものとする。そして、ダミー拡散層(3、4)は、ダミーセル(1、21)が、他のセル(1、2、21)に隣接して配置されるときに、それらの境界からの距離(L1)が、第1長さになる位置に設けられることが好ましい。

(もっと読む)

半導体集積回路の設計方法、製造方法、回路設計プログラム、及び半導体集積回路

【課題】レイアウト修正による遅延変動を抑制しつつ半導体集積回路のプラズマダメージを軽減する製造方法を提供する。

【解決手段】半導体集積回路の製造方法は、コンピュータによって実行され、第1ゲート電極21に接続する金属配線と、第1ゲート電極21とのアンテナ比を検証するステップと、アンテナ比の検証結果に基づいて半導体集積回路のレイアウトを変更するステップとを具備する。レイアウトを変更するステップは、複数の論理セルから、アンテナ比の検証結果に応じたゲート面積の論理セルを選択するステップと、論理セルを、論理動作しないフィルセル40として空き領域に配置するステップと、フィルセル内の第2ゲート電極41を金属配線に接続するステップとを備える。

(もっと読む)

集積回路装置の設計方法及び製造方法並びに電子機器

【課題】ライブラリ開発工数を低減することができる集積回路装置の設計方法及び製造方法並びに電子機器を提供すること。

【解決手段】本発明の集積回路装置の設計方法は、第1〜第Nの異なる論理をそれぞれ有する第1〜第Nの論理セルの特性情報と第1〜第Mの異なる電流供給能力をそれぞれ有する第1〜第Mの電流供給セルの特性情報とを含むライブラリを作成し(ステップS20)、ライブラリを用いて論理回路の回路接続情報及びレイアウトパターンを作成し(ステップS30)、論理回路の回路接続情報及びレイアウトパターンに基づいて論理回路を含む集積回路の回路接続情報及びレイアウトパターンを作成する(ステップS40)。ステップS30において、論理回路が第n(1≦n≦N)の論理と第m(1≦m≦M)の電流供給能力を有する回路を含む場合には、第nの論理セルと第mの電流供給セルを用いて回路接続情報及びレイアウトパターンを作成する。

(もっと読む)

基本セルおよび半導体装置

【課題】チップサイズの増大を防ぎ、かつ、電源ノイズに対する耐性が向上した基本セルを提供する。

【解決手段】基板の表面から所定の深さまでの領域に第1の導電性不純物が拡散された第1のウェル拡散層と、第1のウェル拡散層の上に設けられた絶縁膜と、絶縁膜上に設けられた第1のダミーパターンとからなる容量素子を有する。

(もっと読む)

半導体集積回路の設計方法

【課題】チップ内におけるIRドロップの最大値とばらつきを低減できる半導体集積回路の設計方法を提供する。

【解決手段】本発明の半導体集積回路の設計方法は、複数のセルの接続関係を示すネットリストに基づいて、セットアップタイミング条件を満たすように複数のセルをセル配置領域に仮配置するステップと、セル配置領域を複数に分ける複数のパワーリージョンを生成するステップと、各セルごとの消費電流を示したセルパワーファイルを用いて各パワーリージョンごとの消費電流を算出するステップと、セットアップタイミング条件の違反にはならない範囲で、各パワーリージョンの消費電流を参照して、仮配置されたセルの配置位置を調整するステップとを有する。

(もっと読む)

半導体集積回路、および、スイッチの配置配線方法

【課題】スイッチの配置配線を短時間で容易に行う。

【解決手段】第1電源線(例えば実VDD線)と内部電圧線間に回路セルを有する回路ブロックと、内部電圧線に接続される2本の電圧セル線23A,23Bと、第2電源線(例えば実VSS線)に接続される2本の電源セル線24A,24Bと、スイッチ制御線29に接続される制御セル線25と、トランジスタ(TR1,TR2)と、を有するスイッチセル20Nが、回路ブロック1の周囲の四方全てに配置される。各スイッチセル20Nにおいて、制御セル線25がセル中心を通り一方向に配置され、2本の電圧セル線23A,23Bと、2本の電源セル線24A店Bの各々が、制御セル線25と並行に、かつ、制御セル線25を挟んで制御セル線25から等距離の位置に互いに並行に配置されている。

(もっと読む)

半導体装置

【課題】ウエル基板の電位制御によるリーク電流削減を行おうとした場合に、上層配線からの接続部が信号配線の多い領域に配置されていると、配線混雑が発生する。

【解決手段】基板電源供給セル100にて電源配線110をコの字状に形成することにより基板電源配線120の一部を露出させ、以て上層配線への接続部140を基板電源供給セル100の境界部に配置することにより、信号配線効率を低下させないでリーク電流を削減する。

(もっと読む)

半導体集積回路

【課題】電源ノイズを抑制する。

【解決手段】電源電圧Vddまたは基準電圧Vssが印加される主配線(第1基準電圧幹線VSS1)と、複数の副配線(基準電圧枝線VSSB)と、複数の基準電圧枝線VSSBに接続されている複数の回路セル(不図示)と、入力される制御信号に応じて、複数の基準電圧枝線VSSBのうち、所定の回路セルが接続されている基準電圧枝線VSSBと第1基準電圧幹線VSS1との接続および遮断を制御する電源スイッチセルSW1,SW2,…と、複数の基準電圧枝線VSSBを相互に接続する補助配線50と、を有する。

(もっと読む)

半導体集積回路装置

【課題】半導体集積回路装置のメモリセルの特性抽出、仕様文書の作成等の手間を軽減できるようにする。

【解決手段】メモリセルを有する半導体集積回路装置において、メモリセルは同一であり、メモリセルを構成するpチャネルMISFETとnチャネルMISFETがそれぞれ形成されるウェル領域に対する給電部を共通セルトポロジーで構成する。要するに、メモリセルの基体電位を固定または可変にする場合に固定型回路と可変型回路が共通セルトポロジーとして設計される。これによって、メモリセルの特性抽出、仕様文書の作成等の手間を軽減することができる。

(もっと読む)

集積回路設計装置

【課題】集積回路を設計するための集積回路設計装置に関し、集積回路の設計を効率よく行える集積回路設計装置を提供することを目的とする。

【解決手段】本発明は、チップ領域を分割した領域である複数の実装ブロック毎に、実装ブロックを分割した仮想配置領域であるコートを入力手段により設計者から設定し、配置することにより集積回路の設計を行う集積回路設計装置であって、コートをいずれかの実装ブロックに配置するブロック配置処理部と、論理回路を機能毎にまとめたブロックである機能ブロックを、実装ブロック上に配置されたコート上に配置する領域割付処理部と、実装ブロックにおけるコートの配置状態を評価するブロック評価処理部とを有し、評価処理部は、機能ブロックの面積が実装ブロックに配置されたコートの面積に占める割合を算出し、算出された機能ブロックとコートとの面積の割合をコート毎に図形により表示する。

(もっと読む)

半導体集積回路のレイアウト方法、半導体集積回路設計支援装置およびプログラム

【課題】ハードマクロが、その上層の配線から受ける影響を最小限に抑え、ハードマクロ上を効率的に使った配線を実現する。

【解決手段】半導体集積回路(28)のレイアウトを、以下の方法で実行する。まず、記憶部(6)から半導体集積回路(28)の回路情報(32)を読み込む。そして、予めハードマクロ(21)(31)に設定された配線配置可能方向条件を読み込んで、ハードマクロ(21)(31)上の所定の領域において配置が可能な配線の方向条件を決定する。そのうえで、回路情報(32)と方向条件とに基づいて配線処理を行う。この配線処理は、ハードマクロ(21)(31)上を配置する配線のうち、方向条件を満たす配線を配置する。

(もっと読む)

半導体集積回路のレイアウト方法、レイアウトプログラム、及びレイアウト装置

【課題】半導体集積回路においてゲートのデータ密度に起因するトランジスタの特性バラツキを抑制する。

【解決手段】本発明による半導体集積回路の自動レイアウト装置10は、セルをゲート方向に隣接して配置する際、セルの境界付近に配置済みのゲートを基準ゲート111とし、その周辺の所定の領域内に存在するゲート数を規定の範囲内とするように、配置するセルを決定する。

(もっと読む)

半導体集積回路のレイアウト設計方法および半導体集積回路

【課題】パワーゲーティング回路を備えて、容易に電源配線を行うことができ、コストが削減される。

【解決手段】論理合成が行われ、論理合成結果から、被制御回路のセルが特定され、レベルシフタ11およびトランジスタスイッチ12を格子状に配列し、セルが配置される被制御領域13が形成され、レベルシフタ11およびトランジスタスイッチ12に電源配線14a,14bがそれぞれ形成され、被制御領域13にセルが配置されるようになる。これにより、被制御領域13の消費電力の上限が一定となり、被制御回路のセルの配置や配線の自動化が容易になって、レイアウトの短TAT化およびコストダウンを行うことができる。

(もっと読む)

1 - 20 / 86

[ Back to top ]