Fターム[5F064EE42]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線(又は配線間)の物理的性質 (2,766) | 配線抵抗 (638)

Fターム[5F064EE42]に分類される特許

621 - 638 / 638

自動設計方法、自動設計プログラム及び半導体集積回路

【課題】 マルチカットビアへの置換率を高くでき、歩留まりの高い半導体集積回路を製造可能な自動設計方法、自動設計プログラム及び半導体集積回路を提供する。

【解決手段】 始点領域S及び終点領域Eを矩形領域リスト格納部25に格納するステップと、始点領域Sから終点領域Eへの配線経路の探索を矩形領域1つ分進める毎に配線コストを加算するステップと、配線領域rにマルチカットビアを配置するためのビアコストを配線コストに乗算するステップと、障害物リスト格納部24に格納された障害物情報に基づいて障害物コストを加算するステップと、配線コスト、ビアコスト及び障害物コストを集計するステップと、集計した結果に基づいて始点領域Sから終点領域Eへの配線経路を探索するステップと、始点領域Sと終点領域Eとを結線するステップと、マルチカットビアを配置するステップとを備える。

(もっと読む)

半導体回路寄生容量素子抽出装置、抽出方法、および抽出プログラム

【課題】 配線間に挿入されるメタルダミーパターンによる容量変動を、誘電体の誘電率を補正して計算可能とする。

【解決手段】 半導体回路寄生容量素子抽出装置1が、回路配線間に存在する誘電体の誘電率を、メタルダミーパターンの挿入に対応して補正する手段2と、補正された誘電率と回路レイアウトに基づいて、回路配線間の寄生容量素子を抽出する手段3とを備える。手段2は、ダミーメタルを無限大の誘電率を持つ誘電体として、またダミーメタルの配線間面積に対する面密度を用いて誘電率の補正を行う。

(もっと読む)

半導体装置

【課題】 内部回路への配線に制約を与えることなく、静電破壊の耐性を向上させることのできる半導体装置を提供することを目的とする。

【解決手段】 電源電圧が供給される電源パッド2及び3と、電源パッド2及び3に夫々接続される電源配線4及び5と、信号を入出力する入出力パッドP1、P2、・・・、P14と、該入出力パッドP1等に電気的に接続され、且つ電源配線4及び5を夫々介して電源パッド2及び3に電気的に接続される静電保護素子Q1、Q2、・・・、Q14と、信号配線R1等を介して入出力パッドP1等と電気的に接続される内部回路6と、を備えたICチップ1において、静電保護素子Q1等並びに電源配線4及び5を、入出力パッドP1等の外側に配置する。

(もっと読む)

半導体装置におけるパッド部の配線構造

【課題】 パッド部の下の空いた空間に配線を配置させて空間活用度を上げることにより、増加された配線を安定に配置させることができる半導体装置のパッド部配線構造を提供すること。

【解決手段】本発明は、半導体装置の中央部分に配列された複数のパッドと、複数のパッドと同一層に形成され、該複数のパッドの両側に配列されて、所定量の信号のための複数の第1バイアス配線と、第1バイアス配線及びパッドの下において、第1バイアス配線と垂直な方向に配列され、所定量の信号のための複数の第2バイアス配線とを備え、第2バイアス配線が、隣接するパッドの間に向かって第1バイアス配線と垂直な方向に延伸し、パッドの間で折れ曲がり、複数のパッドの下を通って第1バイアス配線と平行な方向に延伸する形状を有することを特徴とする。

(もっと読む)

ジッタ解析方法、ジッタ解析装置及びジッタ解析プログラム

【課題】 LSIの外部出力信号について、電源ノイズの発生とそれに起因するジッタの両者を統合的に実時間で解析できる方法、装置、プログラムを提供する。

【解決手段】LSIレイアウト設計データ601から電源配線の抵抗、容量、インダクタンスを抽出し電源LRCモデル606を作成する。解析モデル作成手段812は、これにトランジスタ回路モデル610、ノイズ源モデル607、シリコン基板モデル608、静電容量モデル609、パッケージ/ボードモデル611を接続し、電源ノイズ解析用モデル813とジッタ解析用モデル817を作成する。解析実行手段814は、最初のシミュレーションで電源ノイズ波形データ816を得、2回目のシミュレーションで電源ノイズ波形データ816を用いてジッタ解析データ815を得る。

(もっと読む)

ネットリスト作成装置

【課題】 寄生RCの抽出の容易化を図るとともに、回路シミュレーションの解析精度を高める。

【解決手段】 トップ階層のブロック内の電源配線及びグランド配線を示すアブストラクトが適用されたレイアウトデータZから配線の寄生RCを抽出し、その抽出結果をネットリストCに適用するとともに、その寄生RCのノードのレイアウトデータ上の座標情報を特定する一方、座標ファイルF1に格納された回路素子の端子のレイアウトデータ上の座標情報と寄生RCのノードのレイアウトデータ上の座標情報とを比較して、その寄生RCの抽出結果が適用されたネットリストEにおける回路素子と寄生RCの接続関係を適正化する。

(もっと読む)

半導体集積回路における特性検証用ネットリストの生成方法

【課題】 半導体集積回路の遅延シミュレーション等の特性検証において、精度を損なうことがなく、かつデータ量の少ないシミュレーション用ネットリストを生成するための、リダクション方法を提供する。これによって、大規模なブロックに対しても短時間で、かつ高精度に、効率的な特性検証の実行を可能とする。

【解決手段】 リダクションルール提供手段2より与えられるリダクションルール3に従って、レイアウト設計データから寄生素子情報を抽出して得られたLPEネットリスト1を、目的とする特性検証結果への影響を無視できる範囲でリダクションして、特性検証用ネットリスト5を生成する。

(もっと読む)

半導体集積回路装置の設計方法

【課題】 半導体集積回路装置の高性能化および高速化を実現できる設計方法を提供する。また、既存のEDAツールを用いた自動化設計フローに融合し、既存技術よりも更なる高性能化および高速化を行うことができる設計方法を提供する。

【解決手段】 半導体集積回路装置内のパスのうち所望する信号到達時間を超えるパスに対し、そのパスに属する構成要素の出力に接続される他の構成要素の数が減少するようにパスを分離する。

(もっと読む)

半導体集積回路のレイアウト設計システムおよびレイアウト設計方法

【課題】

従来のレイアウト設計法では、半導体集積回路上で局所的に消費電流が大きくなる場合などの消費電流分布の偏りが考慮されていなかった。

【解決手段】

本発明は、最上層配線と下層配線とを電気的に接続する電源接続セルを配置する半導体集積回路のレイアウト設計方法であって、半導体集積回路上に複数の機能ブロックの配置を設定する工程と、機能ブロック配置領域外の半導体集積回路形成領域に電源接続セルを複数配置する工程と、電源接続セルの配置に基づいて、最上位配線の電圧降下の影響を解析する工程とを有している。

(もっと読む)

回路検証方法、回路検証システム、集積回路及び集積回路の製造方法

【課題】 実用的な速度のシミュレーションによりエレクトロマイグレーションの検証をすることができる回路検証方法、回路検証システム、集積回路及び集積回路の製造方法を提供すること。

【解決手段】 検証目的の回路の構成及び前記検証目的の回路に備わる各配線の幅を示す回路データを入力する回路データ入力工程と、前記回路データに基づいて直流動作点解析を行うことにより、前記各配線節点における直流電流値を算出する直流電流値算出工程と、前記直流電流値算出工程で算出される前記各配線節点における直流電流値と、前記回路データが示す前記各配線節点の幅と、に基づいて前記各配線節点における電流密度値を算出する電流密度値算出工程と、前記電流密度算出工程で算出される前記各配線節点における電流密度値と所定許容値とをそれぞれ比較する比較工程と、前記比較工程における比較結果を出力する比較結果出力工程と、を含む。

(もっと読む)

半導体集積回路装置

【課題】3値出力多チャンネル半導体集積回路のレイアウトに関し、半導体集積回路の集積度向上と、出力特性を安定化させるための、最適な半導体集積回路レイアウトの設計を提供する。

【解決手段】3値出力回路は、出力ボンディングパッドを中心に一方に第2ハイサイドトランジスタ5、ダイオード8、第2レベルシフト回路7を配置し、もう一方にはローサイドトランジスタ10、第1ハイサイドトランジスタ4、第1レベルシフト回路6、プリドライバ9を配置することによって、各セルを1列に配置し、第2ハイサイドトランジスタ5とローサイドトランジスタ10は出力ボンディングパッド11を挟み、前記第1レベルシフト回路6と前記第2レベルシフト回路7と前記プリドライバ9のセル幅は、前記ローサイドトランジスタ10のセル幅に相当する。

(もっと読む)

半導体装置の評価設計装置、半導体装置の評価設計方法、半導体装置の評価設計プログラムおよび記録媒体

【課題】半導体装置の評価設計を、現実的かつ高精度におこなうこと。

【解決手段】ゲート電極のパターンデータ323bのゲート長情報lgを抽出する。また、ゲート電極のパターンデータ323bと、パターンデータ323bに隣接するゲート電極のパターンデータ323a,323cとの距離情報sg1、sg2を算出する。ゲート電極のパターンデータ323bのばらつきパラメータを、ばらつきパラメータテーブル254から端辺ごとに抽出する。そして、端辺ごとにばらつき情報を算出する。ネットリスト600の記述内のゲート長情報lg(lg=120nm)に、算出されたばらつき情報Dgを加算する。

(もっと読む)

半導体集積回路の階層化レイアウト設計方法

【課題】 回路の配線設計処理時に生じる配線混雑を低減し、設計の後戻りを防止するレイアウト設計方法を提供する。

【解決手段】 半導体集積回路の接続情報に基づいて、ブロックのブロック枠にとらわれることなく、隣接する異なる階層の配線領域を利用して、各ブロックの配線処理を実施する。その際、ブロックのブロック枠を越えて接続する配線に対し、外部ピンを設けず、かつ、隣接する異なる階層の配線としない。その後、各ブロック同様に半導体集積回路の接続情報に基づいて、ブロックのブロック枠にとらわれることなく、隣接する異なる階層の配線領域を利用して、トップ階層配線処理を行う。これによって、配線混雑を緩和できるため、配線混雑が原因のフロアプラン変更に伴う面積増加及び設計後戻りを防止できる。

(もっと読む)

レイアウト設計装置、レイアウト設計方法、レイアウト設計プログラム、および記録媒体

【課題】クロストークエラーの検出を簡単かつ効率的におこなってTATまたは作業工数を短縮化することにより、レイアウト設計の作業効率の向上を図ること。

【解決手段】レイアウト設計装置700は、任意のネットリストを入力するネットリスト入力部704と、入力されたネットリストから得られるセルをLSIチップ上に配置する配置部706と、配置されたセルの集合の中から検査対象となる任意のネットを抽出するネット抽出部707と、回路モデル200の回路シミュレーションをおこなった結果発生したクロストークによって生じる遅延時間に基づいて作成された相関テーブル500に基づいて、抽出されたネット内のセルの内部抵抗値RDと相関関係のある配線長情報Lを抽出する配線長情報抽出部708と、抽出された配線長情報Lに基づいて、クロストーク遅延時間を抑制する遅延時間抑制セルをネットに挿入する挿入部711と、を備える。

(もっと読む)

半導体集積回路のレイアウト処理におけるタイミング調整方法

【課題】 本発明の課題は、挿入するセル及び移動させるセルを既配線上に最適に配置することによって、タイミングECOの回数を削減することを目的とする。

【解決手段】 本発明の課題は、コンピュータが、タイミングエラーを回避するための対象となる既配線上の少なくとも1つ以上の対象セルの出力側の前段セルから該対象セルの入力側の後段セルまでを1つのネットとして定義するネット定義手順と、前記1つのネット内の対象セルの個数より多い数を、前記対象セルを配置する候補となる候補点の個数として算出する候補点個数算出手順と、前記既配線上に複数の前記候補点を配置させ、複数の前記候補点のうち前記タイミングエラーの値が最もゼロに近い候補点を前記対象セルの配置位置として決定する配置位置決定手順とを有する半導体集積回路のレイアウト処理におけるタイミング調整方法によって達成される。

(もっと読む)

集積回路チップ内のボルテージアイランド上で電力ルーティングを行なうための方法、コンピュータープログラム、およびシステム

【課題】集積回路チップ内のボルテージアイランド上で電力ルーティングを行なう方法を提供する。

【解決手段】第1の電力網(31)は、金属レベル1からN1においてボルテージアイランドのために生成される。次いで、第2の電力網は、金属レベルN以上(32)において生成される。前記第2のロバスト電力網の境界領域が決まる(33)。最後に、1セットの電源からの最短距離接続は、前記第2の電力網(34)に対してルートが決められる。

(もっと読む)

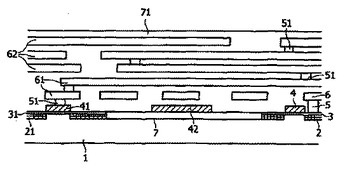

機密性を要する半導体製品、特にスマートカード・チップ

機密性を要する半導体製品、特にスマートカード・チップを提供するため、チップ設計によって実現されうる電気的に活性な構造(2、3、4、5、6)が、例えばシリコンからなるウェーハ(1)内及びウェーハ(1)上に、回路機能の形態で製造されるだけでなく、残りの領域に、それらの下に置かれた機密性を要する回路構造を解析するリバース・エンジニアを大幅に妨げる、互いに絶縁された充てん構造のさらなる導電性部分(42、61、62)(タイル)が設計プログラムによって形成される。形成された部分を説明された偶然の信号経路と連結するための形成された部分間のコンタクトは、「手で」、又は、当該設計プログラムと対応するルーティング・プログラムとの組合せによって配置されることができる。充てん導電性部分はさらに、さらなる回路機能(例えば解析回路)を提供するために、トランジスタ、ダイオード、抵抗器又はコンデンサなどの回路構成部品に接続されてもよい。  (もっと読む)

(もっと読む)

同期式回路のレイアウト設計方法

【課題】タイミング制約ある素子を最適に配置し、配線長を短くでき、かつ後工程の配線工程でCADツールの負担を軽くし、迂回配線の可能性の低減をし、配線によるクロストークノイズの影響を低減し、配線の信頼性悪化を防ぐ。

【解決手段】タイミング制約のある同期式半導体集積回路の自動レイアウト設計方法において、タイミング制約が付与された経路の素子から分岐配線を抽出し(S1)この分岐配線の分岐点に分岐バッファを挿入し(S3)前記経路で与えられたタイミング制約値より始点素子から終点素子までの配線の遅延値のみを求めてから前記各素子の配線長とその総和を求め(S4)前記総配線長の範囲内に前記始点素子と前記終点素子を優先配置し、前記経路で与えられ前記始点素子から前記終点素子の間にある中間素子の配置を、前記各素子の出力抵抗とその配線抵抗との大きさの比較により判定して最適配置する(S8,S9 )ことを特徴とする。

(もっと読む)

621 - 638 / 638

[ Back to top ]