Fターム[5F064EE58]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線順序 (64)

Fターム[5F064EE58]に分類される特許

1 - 20 / 64

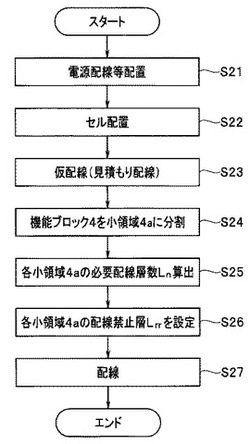

半導体集積回路の設計装置、及び半導体集積回路の設計方法

【課題】チップサイズを縮小することができる、半導体集積回路の設計装置、及び半導体集積回路の設計方法を提供する

【解決手段】下位階層の機能ブロック4に配置された複数のセル間を接続する第一の配線を設計する下位階層配線設計部311と、上位階層の機能ブロック間を接続する第二の配線を設計する上位階層配線設計部312とを備えており、下位階層配線設計部311は、機能ブロック4を複数の小領域4aに分割し、小領域4aごとに機能ブロック4内配線に必要となる必要配線層数Lnを算出して、最下部の配線層から必要配線層数Ln枚の配線層を配線可能領域として同領域内に第一の配線を配置し、上位階層配線設計部312は、第一の配線における配線可能領域以外の機能ブロック4の配線層に第二の配線を配置する。

(もっと読む)

レイアウト設計装置、レイアウト設計方法およびレイアウト設計プログラム

【課題】マクロの全端子で配線が引き出し可能かを判定できるレイアウト設計装置、レイアウト設計方法およびレイアウト設計プログラムを提供する。

【解決手段】記憶部11は内部にマクロを含んだ多層回路の階層レイアウトの設計データを記憶する。チャネル数算出部13は設計データに基づいて、マクロの各端子から所定の配線層まで配線を引き出すために使用可能なチャネル数を端子毎に算出する。経路算出部15は算出したチャネル数の少ない端子から順に、端子から所定の配線層まで配線を引き出すための経路を算出する。経路判定部16はマクロの全ての端子について引き出し経路を算出できたか否かを判定する。

(もっと読む)

半導体集積回路のレイアウト設計方法

【課題】LSIのレイアウト設計において、TAT(Turn Around Time)を増加させることなくタイミング収束を実現する。

【解決手段】LSIのレイアウト設計方法は、レイアウト対象の集積回路のネットリストに基づいて、前記集積回路をクロックドメインに分けることでクロックドメイン回路集合体に区分する工程と、前記クロックドメイン回路集合体の各々に対するタイミング制約を作成する工程と、所定の基準に基づいて前記クロックドメイン回路集合体間の配置順序を決定する工程と、前記クロックドメイン回路集合体を前記配置順序に従って配置し配線することにより前記集積回路のレイアウトを作成する工程とを備える。レイアウト設計後のタイミング収束のTATを短縮することが可能となる。

(もっと読む)

リコンフィギュラブルロジック装置

【課題】セット全体のコストダウンや小型化、ないしは、起動時間の短縮を実現することが可能なリコンフィギュラブルロジック装置を提供する。

【解決手段】リコンフィギュラブルロジック装置において、ルックアップテーブル11は、コンフィギュレーションデータを不揮発的に記憶する手段として、強誘電体素子のヒステリシス特性を利用した不揮発性フリップフロップFFを有する。コンフィギュレーションデータは、ルックアップテーブル11に任意の入出力論理値表を実装するための設定データであり、プログラミングによって設定される。

(もっと読む)

半導体装置の配線構造及びそれを備えた半導体装置

【課題】信号配線が電源配線と長距離に亘って並走することを回避して、信号配線の寄生容量を低減してノイズの影響を低減する半導体装置の配線構造及びそれを備えた半導体装置を提供すること。

【解決手段】第1方向X1に延びる複数の第1配線1Vから構成される第1配線層110と、第1配線層110の上に配設され、第1方向X1に交差する第2方向X2に延びる複数の第2配線2Vから構成される第2配線層120とを備え、第1配線層110および第2配線層120は、第1方向X1および第2方向X2により規定される平面内に設定された配線領域R内に配設され、第1配線1Vは、配線領域Rの第1方向X1における一端から他端までの全長よりも短い長さでそれぞれ形成され、第2配線2Vは、配線領域Rの第2方向X2における一端から他端までの全長よりも短い長さでそれぞれ形成されている半導体装置100の配線構造。

(もっと読む)

半導体集積回路装置の設計方法

【課題】タイミング最適化後のタイミング、および面積を見積もることにより、タイミング最適化後のセルの配置変更を大幅に低減し、レイアウト設計にかかる期間を短縮する。

【解決手段】ネットリスト1、タイミング制約2、フロアプラン3、レイアウトライブラリ4、およびタイミングライブラリ5などを用いた初期配置処理中に、タイミング最適化後のタイミング、面積を見積もるためのタイミング・面積見積もり用ライブラリを予め作成しておき、タイミング制約2を満たすことができるかを見積もる。タイミング制約2を満たすことが困難なパスにあるセルは、近接配置し、逆に容易なパスは離して配置する。その際、面積増加も見積もり、配線混雑が発生しないようにする。

(もっと読む)

半導体装置

【課題】電源電圧の電圧降下を抑制しつつ、信号配線リソースを大きく確保可能な電源配線構造を実現する。

【解決手段】第1配線層に、電源電位配線101a〜101dおよび基板電位配線102a〜102dが形成されており、配線層全体の真ん中より下層側の配線層に、電源ストラップ配線103a,103b,104a,104bが形成されている。上方ビア部114は、下方ビア部112よりも、電源ストラップ配線103a,103b,104a,104bが延びる方向における配置密度が低くなっている。

(もっと読む)

半導体回路の設計装置および設計方法

【課題】配線のしやすさを損なうことなく、ビアの不良による歩留まりの低下を抑制可能な半導体回路の設計装置および設計方法を提供する。

【解決手段】半導体回路の設計方法は、論理回路を構成するセルの配置およびセル間の配線を行い、複数箇所にビアが設けられる配線を含むレイアウトパターンを生成するステップ(ステップS1、S2)と、ビアから、配線上の信号を受信するレシーバセルまでの負荷容量をビア毎に算出するステップ(ステップS4)と、ビアごとの、負荷容量に基づいて、負荷容量が大きいビアを優先的に低抵抗のビアに置換するステップ(ステップS6、S7)を備える。

(もっと読む)

配線レイアウト方法及び配線レイアウト装置

【課題】配線領域を無駄なく使用することが可能な配線レイアウト方法及び配線レイアウト装置を提供することを目的とする。

【解決手段】配線層上に設けられたグリッド線に沿って配線レイアウトを行う配線レイアウト装置であって、信号線端部の突き出し部分の長さに基づいて決定されるグリッド幅となるように、前記配線層毎にグリッド線をグループ分けして複数のグループを設定するグループ設定手段と、前記配線層毎に、選択順に従って前記グループを選択して、信号線の配線をレイアウトする配線手段と、を有する。

(もっと読む)

設計支援装置、設計支援方法、および設計支援プログラム

【課題】タイミングドリブン配置された順序セルのタイミングを維持しながら消費電力の低減化を図ること。

【解決手段】まず、初期情報を取得する(S1801)。つぎに、順序セルがタイミングドリブン配置されたセル配置可能領域に、所定数のROW領域候補を設定する(S1802)。そして、ランキング処理を実行して(S1803)、ROW領域候補riの優先順位を付ける。このあと、実際にチップに使用するROW領域の必要個数Nを算出する(S1803)。ROW領域候補の中からROW領域を決定する(S1805)。そして、順序セルの整列化処理を実行する(S1806)。

(もっと読む)

電子デバイスレイアウト設計のためのヒューリスティックルーティング

【課題】電子デバイス設計レイアウトを修正する方法を提供すること。

【解決手段】電子デバイス設計レイアウトを修正する方法であって、設計レイアウトの一部分を識別することであって、該設計レイアウトの該一部分は、電子デバイスの物理的レイアウトを表現しており、該設計レイアウトの該一部分は、1つ以上のバイアスフィーチャを含んでいる、ことと、該バイアスフィーチャのそれぞれに一部基づいてレイヤーバイアスを決定することと、デバイス設計レイアウトの該一部分に1つ以上のトレースを追加することにより、該設計レイアウトの該一部分を修正することであって、該1つ以上の追加されたトレースの配置は、該決定されたレイヤーバイアスに少なくとも一部基づいている、ことと、該設計レイアウトの該修正された部分をメモリ格納位置に格納することとを含む、方法。

(もっと読む)

配線パターン生成装置、配線パターン生成プログラム、および、半導体装置の製造方法

【課題】配線のレイアウトパターンを決定する際の処理モードを適宜選択し得るようにして、配線パターンの自動生成を良好に行えるようにする。

【解決手段】配線パターンを自動生成に必要な情報を取得する情報取得手段4aと、前記情報取得手段4aが取得した各情報に基づき、接続対応関係にあるパッド同士の間を導通させる配線のレイアウトパターンを決定するとともに、当該レイアウトパターンの決定を予め規定された互いに異なる複数の処理モードのいずれかに対応して行う配線処理手段4bと、前記配線処理手段4bが対応する処理モードを選択し、その選択結果を前記配線処理手段4bに指示するモード選択手段4cと、を備えて配線パターン生成装置を構成する。

(もっと読む)

配線パターン生成装置、配線パターン生成プログラム、および、半導体装置の製造方法

【課題】限られた大きさの配線領域であっても、当該配線領域の形状とパッド位置との関係を考慮することで、当該配線領域に対する配線パターンの自動生成を良好に行えるようにする。

【解決手段】配線パターンを自動生成に必要な情報を取得する情報取得手段4aと、前記情報取得手段4aが取得した各情報を基に、接続対応関係にあるパッド同士の位置関係によって、前記各パッドを複数のパッド群にグループ分けするグループ分け手段4bと、前記グループ分け手段4bがグループ分けした複数のパッド群についての処理優先順を決定する優先順決定手段4cと、前記優先順決定手段4cが決定した処理優先順に従いつつ、前記パッド群毎に個別に、当該パッド群で接続対応関係にあるパッド同士の間を導通させる配線のレイアウトパターンを決定する配線処理手段4dと、を備えて配線パターン生成装置を構成する。

(もっと読む)

3次元集積回路の設計方法及び3次元集積回路の設計プログラム

【課題】 積層数をさほど増やすことなく、配線長が100μmを越える配線の数を減少させることができ、回路性能の向上をはかる。

【解決手段】 3次元集積回路の設計方法であって、集積回路を、X方向に短くY方向に長いXY平面上の仮のレイアウト領域に配置した後(S1)、仮のレイアウト領域をY方向に2N個以上の小領域に分割すると共に、N個の小領域毎に1つのブロックを構築し(S2)、小領域のkN番目及びkn+1番目が最上層又は最下層になるように、各ブロックを小領域単位でY方向に折り畳み、N層の集積回路を積層する(S3)。

(もっと読む)

半導体回路設計装置および半導体回路設計方法

【課題】レイアウトパターン修正による遅延変動を正確に見積もる。

【解決手段】本発明に係る半導体回路設計装置は、パターン修正部1と、パターン変更抽出部2と、相関関係データベース3と、遅延変動見積もり部4と、タイミング検証部5と、比較判定部6と、タイミング再検証部7と、を備えている。予め相関関係データベース3に格納されたパターン変更の種類ごとに分類された変動量と遅延変動の相関関係情報を用いて遅延変動値を見積もるため、レイアウトパターン修正後に再度のタイミング検証が必要かどうかを短時間で判別できる。その結果、遅延変動値が余裕度を超えない場合は再度のタイミング検証を行わずにすむので、設計時間を短縮できる。すなわち、本実施形態によれば、レイアウトパターン修正による遅延変動を正確に見積もることができ、タイミングの再検証を行う頻度を削減できる。

(もっと読む)

半導体装置の設計装置、設計方法及びプログラム

【課題】アレイ状に配置される接続ピンからの配線引出し方向を決定する設計装置を提供する。

【解決手段】半導体装置の設計装置は、アレイ状に配置される接続ピンのピン割当て情報に基づいて、接続ピンに接続される配線の引出し方向を演算する引出し方向演算部9を備える。配線引出し方向情報演算部9は、ピンアサイン情報演算部8が演算したピンアサイン情報、又は、ピンアサイン入力部5から入力するピンアサイン情報に基づいて、各配線の引出し方向を決定し、配線引出し方向情報として出力する。配線引出し方向情報は、配線引出し方向情報出力部12から出力され、また、配線優先順位情報演算部10に入力される。

(もっと読む)

半導体集積回路及び半導体集積回路のレイアウト方法

【課題】上地層における信号配線を妨げることなく電源配線パターンの強化を行うことができる、半導体集積回路及び半導体集積回路のレイアウト方法を提供する。

【解決手段】論理素子が設けられた下地層と、前記下地層上に設けられた上地層とを備える半導体集積回路のレイアウト方法において、前記上地層に複数本に延びる電源配線をレイアウトし、電源配線データを生成するステップと、前記下地層に前記論理素子をレイアウトし、論理素子データを生成するステップと、前記電源配線データ及び前記論理素子データに基づいて、前記下地層に、導電性である電源強化用パターンをレイアウトし、電源強化用パターンデータを生成するステップとを具備し、前記電源強化用パターンデータを生成するステップは、前記電源強化用パターンを、前記下地層における前記論理素子がレイアウトされていない領域に、前記複数本に延びる電源配線パターン同士が接続されるようにレイアウトするステップを備えている。

(もっと読む)

配線レイアウト方法及び配線レイアウト装置

【課題】同一ノードの配線抵抗を効率的に低減し得る配線レイアウト方法を提供する。

【解決手段】配線層のレイアウトパターンから対象ノードの配線の図形データを抽出する工程と、対象ノードの配線を、設計ルールを満たす範囲で頂点数が変わらないように平行移動して拡張した平行移動領域を生成する工程と、対象ノードが含まれる配線層のレイアウトパターンから、対象ノードの配線拡張可能領域を抽出する工程と、平行移動領域と配線拡張可能領域との論理和により配線拡張領域A3を抽出する工程と、配線拡張領域A3に対象ノードの配線を平行移動した束配線を生成する工程とを備えた。

(もっと読む)

半導体集積回路のレイアウト設計方法

【課題】設計した半導体集積回路のレイアウトを少ない戻り量で容易に修正する。

【解決手段】レイアウト設計装置は、半導体集積回路のコア領域上に、スタンダードセル領域及びハードマクロ領域を定め(S105c)、スタンダードセル領域及びハードマクロ領域上に、複数の通常メッシュ電源配線を一定の間隔で配置する(S110b)とともに、ハードマクロ領域上の通常メッシュ電源配線と通常メッシュ電源配線との間に、細密メッシュ電源配線を配置した(S110d)後、スタンダードセル領域及びハードマクロ領域上に、信号配線を配置し(S145)、ハードマクロ領域上に配置された信号配線に対して収束しているか否かを判定し(S150)、信号配線が収束していない場合に、信号配線の収束を阻害している細密メッシュ電源配線を削除して(S152)から、信号配線を配置し直す(S145)。

(もっと読む)

自動配置配線方法および半導体装置

【課題】コストの削減および製造容易性の向上を図りつつ、配線の配置の修正およびビアの分布の均一化を図れる自動配置配線方法を提供する。

【解決手段】この自動配置配線方法は、配線層間において複数のビアvを自動配置配線の対象領域の全体または一部に縦横に間隔を空けて配置し、前記配線層の配線M2s,M1sを前記複数のビアvの間を通る様に配置し、前記配線M2s,M1sの端部をその端部近傍のビアvs,vA,vBに接続する様にしたものである。

(もっと読む)

1 - 20 / 64

[ Back to top ]