Fターム[5F064FF48]の内容

ICの設計・製造(配線設計等) (42,086) | 切り換え、選択 (3,709) | 切り換え、選択実行方法 (1,017) | 配線の作成、変更 (178)

Fターム[5F064FF48]の下位に属するFターム

ボンディング (21)

Fターム[5F064FF48]に分類される特許

1 - 20 / 157

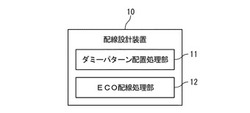

配線設計装置、配線設計方法、及びプログラム

【課題】半導体集積回路に対し、ダミーパターン配置後に、ダミーパターンを使用したECO(Engineering Change Order)配線設計を行う。

【解決手段】配線設計装置は、半導体集積回路にダミーパターンを配置し、ダミーパターンをECO配線に変更し、ダミーパターンの再配置及び電気的ショートを発生することなくECO配線を行う。これにより、ECO配線を行う時に、ダミーパターン再挿入や、既存配線とのショートを発生せずに、設計TAT(Turn Around Time)増を抑制することを可能とする。

(もっと読む)

半導体集積回路

【課題】半導体集積回路において消費電力を低減するとともに、ノイズの発生を低減する。

【解決手段】半導体集積回路は、複数のDFFを有し、その少なくとも1つが冗長回路とされる。半導体集積回路が通常動作モードである際に、ANDゲート1によって冗長回路であるDFF3−3に印加されるクロック信号を停止する。冗長回路へのクロック信号が停止されると、当該冗長回路においてクロック信号が停止された状態における冗長回路のドレイン−グランド間容量よりもその容量を増加させる。

(もっと読む)

集積回路の配線方法、集積回路の配線プログラム及びそれを記憶した記憶媒体

【課題】 要求性能を満たすとともに、消費電力を削減することができる配線方法を提供すること。

【解決手段】 本発明の実施形態による集積回路の配線方法は、所定の動作周波数を満たすように第1の配線を求め、前記所定の動作周波数と前記第1の配線のクリティカルパスとを用いて最大迂回配線長を算出し、集積回路の配線を複数の群に分けた場合に、配線群に含まれる前記第1の配線を、前記第1の配線を含む他の配線群内の配線を用いて迂回させることで第2の配線を求め、前記第2の配線と前記第1の配線との差分が前記最大迂回配線長以下ならば、前記第2の配線によって前記第1の配線を更新し、前記第2の配線と前記第1の配線の差分が前記最大迂回配線長よりも大きければ、前記第1の配線を更新しないことを特徴としている。

(もっと読む)

メモリセル

【課題】拡散層等のバルクが固定であってメタル層、コンタクト層の少なくとも何れか1層を変更して複数の仕様に対応可能なメモリセルを提供すること。

【解決手段】メモリユニットが列方向に沿って鏡面対称に行方向に沿って並置されて、2行2列に配置されメモリセルを構成する。メモリユニットは、行方向に沿って並置され列方向に伸長される第1〜第4拡散層を備え一対の記憶ノードが構成される。第1および第2ワード線は第1〜第4拡散層の両端部外方に配置される。第1及び第2ワード線の間に行方向に沿って第1のメタル配線領域が確保され、第1メタル層が配線可能とされる。列方向に隣接配置されるメモリユニットの境界領域でありは第3、第4拡散層が配置される列方向の位置には列方向に沿って第2のメタル配線領域が確保され、第2メタル層が配線可能とされる。

(もっと読む)

レイアウト設計方法、および、レイアウト設計プログラム

【課題】チップ面積の増大を抑制しつつ、ダミー配線パターンの配置にかかる工数を低減する。

【解決手段】レイアウト設計方法は、レイアウト設計装置が、レイアウト領域に対して、半導体集積回路の配置配線(S1)を行った後、レイアウト領域に配置されているバルクセルを抽出し(S2)、レイアウト領域において、抽出したバルクセルの周囲に、所定の大きさを備える空き配線領域が存在するかどうかを検索し(S3)、検索の結果、所定の大きさを備える空き配線領域を検出した場合、抽出したバルクセルの座標を基準にして、検出した空き配線領域にダミー配線パターンを配置(S4)する。

(もっと読む)

プログラマブル論理の特定用途向け集積回路等価物および関連の方法

【課題】FPGAのASIC等価物をより効率的、経済的に提供すること。

【解決手段】FPGAのASIC等価物の提供は、複数のいわゆるハイブリッド論理素子(HLE)を含むASICアーキテクチャを使用することによって、促進され、より効率的、経済的に実行される。各HLEは、FPGA論理素子(LE)の完全機能の一部を提供可能である。ユーザの論理設計を実装する各FPGA LEの機能は、ユーザの論理を再合成することなく単一または複数のHLEへとマッピング可能である。必要な数のHLEだけが、各LEの関数を実行するために使用される。LE間および(1)単一のHLEまたは(2)HLE群間の1対1の等価性によって、FPGA設計とASIC設計との間のいずれの方向においてもマッピングが(再合成することなく)促進される。

(もっと読む)

デューティ調整回路の設計装置及び設計方法

【課題】任意のデューティ比であるデューティ調整回路が設計可能なデューティ調整回路の設計装置を提供する。

【解決手段】調整方法決定部は、デューティ調整回路のネットリストと、デューティ調整回路の初期状態のタイミング情報と、ドライバビリティ指定情報と、デューティ比の目標値と、を入力し、立ち上がり時間と立ち下がり時間のどちらの調整によりデューティ比の調整をするか決定する。置換セル数決定部は、調整方法決定部の決定に基づいて置き換える遅延セルの数と種類を遅延調整セルライブラリの中から選択する。遅延調整セル置換部は、置換セル数決定部の決定に基づいて、デューティ調整回路に含まれる複数の遅延調整セルの中から選択した遅延調整セルを初期状態とは異なる遅延調整セルに置き換える。

(もっと読む)

半導体装置

【課題】裏面FIB加工における場所特定を容易にする。

【解決手段】半導体装置は、第1方向および前記第1方向に直交する第2方向の平面内に広がる第1導電型の半導体基板60の表面上に形成された回路部65と、前記半導体基板内の表面側に形成され、前記回路部を構成し、素子として機能する、前記第1導電型と異なる第2導電型の複数のウェル61と、前記半導体基板内の表面側に形成され、前記回路部を構成せず、素子として機能しない、前記第2導電型の複数のダミーウェル62と、を具備する。

(もっと読む)

集積回路装置、電子機器及び集積回路装置の製造方法

【課題】 出力端子から出力される電圧値に応じて複数種の中から選択される耐圧に設定される集積回路装置等の提供すること。

【解決手段】 第1の耐圧を有する第1の出力トランジスター構造Tr_M1,Tr_M2と、第1の耐圧よりも高い第2の耐圧を有する第2の出力トランジスター構造Tr_H1,Tr_H2とが形成された半導体基板に、マスクを変えて配線して所定の耐圧に設定される集積回路装置である。配線により第1の耐圧が選択されると、第1,第2の出力トランジスター構造の双方が出力端子OUTと接続され、第2の出力トランジスター構造は、ダイオード接続されて静電気保護素子D1,D2を形成する。配線により第2の耐圧が選択されると、第1の出力トランジスター構造は出力端子OUTに非接続とされ、第2の出力トランジスター構造が出力端子OUTと接続される第2耐圧出力段トランジスターを形成する。

(もっと読む)

半導体製造方法および半導体装置

【課題】ウェーハテスト後のウェーハ状態において所望の回路を印刷処理により容易に形成することが可能な半導体製造方法および半導体装置を提供することを課題する。

【解決手段】本発明に係る半導体製造方法は、ウェーハの被描画パターン形成領域に所定の深さを有する溝部を形成する工程、ウェーハに対してトリミング要否の検査を行う工程、前記ウェーハにおけるトリミング必要なウェーハの前記溝部に導電性溶剤を射出し描画パターンを描画する工程、描画パターンを描画した後、脱気および低温アニールする工程、脱気および低温アニールした成膜後、当該成膜表面を平坦化する工程、および平坦化した後、高温アニールする工程、を有する。

(もっと読む)

半導体装置の製造方法

【課題】半導体素子単体の駆動力にはバラツキがあっても、搭載回路の駆動力のウェーハ間のバラツキを抑制することのできる半導体装置の製造方法を提供する。

【解決手段】実施形態の製造方法は、複数の半導体素子が並列に配置された回路を有する半導体装置の製造方法であって、上層配線形成工程用に、複数の半導体素子の並列接続数がそれぞれ異なる複数のマスクを製作しておき(工程S01)、半導体基板上に半導体素子を形成し(工程S02)、上層配線を形成する工程の前に、半導体基板上に形成された半導体素子のオン電流の測定を行い(工程S03)、その測定の結果にもとづいて、上層配線形成工程用の複数のマスクから1枚のマスクを選択し(工程S04)、選択したマスクを用いて上層配線を形成する(工程S05)。

(もっと読む)

電子素子の製造方法および電子素子

【課題】有機絶縁層を有する電子素子の配線短絡を簡素な工程により絶縁することが可能な電子素子の製造方法および電子素子を提供する。

【解決手段】配線層21,22の上に有機絶縁層12を形成したのち、配線層21,22の短絡部23に、有機絶縁層12に対して透過性を持つ波長のレーザ光LBを有機絶縁層12を介して照射、または基板11に対して透過性を持つ波長のレーザ光LBを基板11を介して照射する。レーザ照射領域24では短絡部23が消失して、配線層21と配線層22との間の絶縁が回復する。短絡部23の上下に接する有機絶縁層12または基板11は残されている一方、レーザ照射領域24(短絡部23が消失した部分)には空洞25が生じる。

(もっと読む)

半導体装置およびその配線変更方法

【課題】カスタマイズ化によるコストの上昇を抑制できる半導体装置およびその配線変更方法を提供する。

【解決手段】半導体装置に、第1の配線層に設けられた第1の予備配線、第2の配線層に設けられた第2の予備配線、第1の配線層の第1の予備配線と第2の予備配線とが交差する位置に設けられた中継パッド、中継パッドを介して第1の予備配線と第2の予備配線とを接続する、該中継パッドの端部に設けられたビアとを備えておく。そして、第1の配線層に設けられた中継パッドをビア間で切断する工程と、第2の予備配線とビアを介して接続された中継パッドの断片と変更対象である所要の部位とを接続するための配線を追加する工程とを含んで設計された第1の配線層用のレチクルを作成し、該レチクルを用いて第1の配線層を形成する。

(もっと読む)

半導体集積回路の設計方法

【課題】設計期間の短縮が可能な半導体集積回路の設計方法を提供する。

【解決手段】本実施形態によれば、半導体集積回路の設計方法は、第1配線層、前記第1配線層上に設けられる第2配線層、及び前記第2配線層上に設けられる第3配線層を有する半導体集積回路の設計方法である。この方法は、前記第2配線層に、第1方向に沿って複数のスペア配線を配置し、前記第3配線層に、前記第1方向に直交する第2方向に沿って複数のスペア配線を配置する工程を備える。さらに、この方法は、前記スペア配線の配置後に、前記第1配線層に素子を配置する工程と、前記素子の配置後に、前記第1乃至第3配線層の少なくともいずれか1つに信号配線を配置する工程と、前記スペア配線を用いて、配線の設計変更を行う工程と、を備える。

(もっと読む)

半導体集積回路装置及びその製造方法

【課題】複数の電源を使用する半導体集積回路装置において、接続対象の接続する電源配線を容易に選択ないし変更できる半導体集積回路装置及びその製造方法を提供すること。

【解決手段】半導体集積回路装置は、静電気保護素子及び入出力回路素子のうちの少なくとも1つを含む接続対象と、1以上の電源配線及びパッドから選択される2以上の要素と、同一層に形成された複数の配線と、複数の配線のうちのいずれか1つの配線と、接続対象とを電気的に接続する第1コンタクトと、を備える。複数の配線は、電源配線、パッド、又は電源配線及びパッドのうちのいずれかと電気的に接続された配線である。

(もっと読む)

集積回路の設計および製造のための方法およびアーキテクチャ

【課題】集積回路の設計及び製造の問題点に対応する新規の設計プラットフォームを提供する。

【解決手段】集積回路の設計のためのシステム。構造マルチプロジェクトウエハ5(SMPW)は、あらかじめ製造されており且つあらかじめ確認されている多数の機能ブロックを有する。SMPWは、ユーザーが、該ユーザーの要求に応じて、SMPWの異なるブロックをカスタマイズ及びプログラムできるように、コンタクト層まで形成される。SMPWのプロバイダーは、SMPWの在庫を保持する。もし、SMPWの一つがユーザーのIC設計要求の全てを満足できるか、又は市場/コンセプトの確認やIPの確認のような、ユーザーのIC設計プロセスの中間ステップに役立つならば、SMPWは、上記ユーザーへ提供される。ユーザーは、1-3ヶ月のサイクルタイムを有する合理的な設計フローを用いて直接生産へ進む。又は、ユーザーは、もっと長いサイクルタイムを有する普通の設計フローを用いる生産へ進む。

(もっと読む)

半導体装置

【課題】機能修正を行う場合でも速やかに製造することができるとともに、仕掛品の廃棄量を削減することが可能な半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、レビジョン信号発信回路が形成されたベース層と、前記ベース層上に積層された3層以上の配線層と、最上位の配線層に形成された電源配線あるいはグランド配線と、前記レビジョン制御回路を前記最上位の配線層の電源配線あるいはグランド配線にのみ接続するレビジョン信号線と、を備えている。

(もっと読む)

半導体装置および配線用マスク判別方法

【課題】使用した配線用マスクを簡単かつ確実に判別でき、確認工数を削減する。

【解決手段】所定の配線パターンと共に両端に端子を備えた抵抗素子の複数41、42、43、を含む抵抗素子領域を形成するための所定配線用マスクを用いたリソグラフィステップと、半導体ウエハ特有の配線パターンと共に特有の配線パターンに応じて抵抗素子の端子間にて直列およびまたは並列接続された接続配線を含む識別領域50を形成するための識別配線51用マスクを用いたリソグラフィステップと、接続配線に接続され露出したパッド19を形成するためのパッド配線用マスクを用いたリソグラフィステップと、を含む。第1配線層および第2配線層の抵抗素子領域および識別領域の組がTEGチップまたはスクライブラインに形成されている。露出したパッドを介して抵抗素子の直列およびまたは並列接続された接続配線の抵抗値を測定するステップを更に含む。

(もっと読む)

設計装置、設計方法、及び設計プログラム

【課題】タイミング違反の修正の問題を解消する。

【解決手段】設計装置10は、クロックツリーを生成するクロックツリー生成部121と、クロックツリー生成部121により生成されたクロックツリーに対応する回路データについて、セットアップタイミングを考慮せずにホールド違反を修正するように、遅延素子を論理的に挿入する論理修正部122と、論理修正部122の処理結果に基づいて、半導体集積回路のレイアウトを修正するレイアウト修正部123と、レイアウト修正部123により修正された半導体集積回路のレイアウトを出力する出力部124と、を備える。

(もっと読む)

半導体集積回路、半導体集積回路の設計方法

【課題】I/Oバッファ変更があった場合であっても、リワーク性を有する半導体集積回路を提供する。

【解決手段】半導体集積回路(7)のチップの外周部に沿って形成されたI/O配置領域(2)と、その外周部の内側に形成されたプリミティブブロック配置領域(3)とを具備する半導体集積回路(2)を構成する。その半導体集積回路(7)は、そのプリミティブブロック配置領域(3)は、容量セルの配置を許容する許容領域(3)と、そのI/O配置領域(2)に沿って形成され、その容量セルの配置が禁止された禁止領域(11)とを含む。

(もっと読む)

1 - 20 / 157

[ Back to top ]