Fターム[5F064HH13]の内容

ICの設計・製造(配線設計等) (42,086) | 設計、製造における計算機技術 (6,629) | 入力 (247)

Fターム[5F064HH13]に分類される特許

1 - 20 / 247

設計支援装置

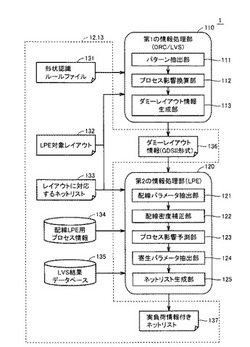

【課題】配線レイアウトのパターン形状に依存した効果をLPEに容易に取込む。

【解決手段】半導体集積回路の設計支援装置は、図形演算機能を有する第1の情報処理部110と、第2の情報処理部120とを備える。第1の情報処理部110は、レイアウト情報に含まれる各配線層のレイアウトパターンに対して図形演算を施すことによって、予め定める特定形状の配線パターンを抽出する。第2の情報処理部120は、製造プロセスに依存した配線または配線層間の絶縁層の厚みの設計値からのずれの大きさを、レイアウト情報から抽出した配線幅および配線密度の情報と、抽出された特定形状の配線パターンに関する情報とに基づいて予測する。そして、第2の情報処理部120は、予測した設計値からのずれの大きさを取り入れた配線および配線層間の絶縁層の厚みに基づいて、配線の寄生パラメータを抽出する。

(もっと読む)

半導体設計装置、半導体設計方法及びプログラム

【課題】レイアウトデータの検証を行うLVS処理やDRC処理と、OPC処理には、プログラムの実装に重複(冗長)な処理が存在する。そこで、これらの処理を、統合することも考えられる。しかし、そのような統合を実際に行えば、プログラムの変更が大規模になり、半導体設計装置のコストを上昇させてしまう。そのため、既存のリソースを有効活用しつつ、OPC処理の処理スピードを向上させた半導体設計装置が、望まれる。

【解決手段】半導体設計装置は、半導体集積回路のレイアウトデータの検証を行うレイアウトデータ検証部と、レイアウトデータ検証部が生成するOPC処理用中間データを用いて、OPC処理を行うOPC処理部と、を備えている。

(もっと読む)

半導体集積回路のレイアウト方法、レイアウト装置およびプログラム

【課題】複数の階層ブロックが互いに重なり合うことを許容しつつレイアウト設計を行う際に、設計期間の長期化を防ぐこと。

【解決手段】複数の内部要素をそれぞれ含む複数の階層ブロックを、内部要素を割り当て可能な内部要素リソースが配置された実装領域に対してレイアウトする場合に、第1の階層ブロックと第2の階層ブロックとが重複領域において重なり合うとき、第1の階層ブロックの内部要素のうちの重複領域に含まれる第1の内部要素の個数と、第2の階層ブロックの内部要素のうちの重複領域に含まれる第2の内部要素の個数との合計が、重複領域に含まれる内部要素リソースの個数以下となるように、第1の階層ブロックおよび第2の階層ブロックを配置し、第1の内部要素の個数と第2の内部要素の個数との比に応じて、重複領域に含まれる内部要素リソースを、第1の階層ブロックと第2の階層ブロックに割り当てる。

(もっと読む)

半導体集積回路のチップサイズ見積もり装置、及び半導体集積回路のチップサイズ見積もり方法

【課題】精度よく簡便にチップサイズを見積もることができる、半導体集積回路のチップサイズ見積もり装置、及び半導体集積回路のチップ見積もり方法を提供する。

【解決手段】回路の機能の実現に最小限必要なゲート数である最小機能ゲート数を入力する入力部1と、セルライブラリごとに所定の動作速度の達成に必要となるゲート数と前記最小機能ゲート数との比率である性能考慮ゲート数係数が予め設定された設定値保持部21と、前記最小機能ゲート数と前記性能考慮ゲート数係数とから算出されるゲート数を用いて前記回路の総面積を見積もる計算部22と、を備えたことを特徴とする。

(もっと読む)

クロックツリー生成方法、クロックツリー生成プログラム、記録媒体、およびクロックツリー生成装置

【課題】外部電源電圧が変動した場合でも、安定に動作する半導体装置を実現することが可能なクロックツリー生成方法を提供する。

【解決手段】プログラム5のCTS部8は、電源領域Aから電源領域Bにクロック信号CLK1,CLK2を伝達する経路L1,L2を設け、電源領域A内の経路L1,L2にそれぞれアンカーバッファB1,B2を配置し、遅延回路D1,D2を電源領域B内の経路L1,L2にそれぞれ配置し、遅延回路D3,D4をアンカーバッファB1,B2の入力ノード側の経路L1,L2にそれぞれ配置する。したがって、外部電源電圧VDD1,VDD2が変動した場合でも、クロック信号CLK1,CLK2の遅延時間は同じになる。

(もっと読む)

タイミング解析方法、タイミング解析装置、およびタイミング解析プログラム

【課題】遅延計算に要する処理時間を短縮して、タイミング解析全体に要する処理時間を短縮可能とする。

【解決手段】タイミング解析方法は、半導体チップ上にレイアウトされた回路に対して電圧降下解析を行い、電圧降下解析結果に基づいて、チップ上の電圧降下を所定の電圧範囲ごとの領域として電圧降下領域ファイルを作成し、遅延のばらつきを表現する第1OCV係数が電圧降下を考慮して所定の電圧ごとに対応付けられたOCV係数ファイルを用いて、電圧降下領域ファイルの所定の電圧範囲に対応する第2OCV係数を領域ごとに算出し、算出した第2OCV係数と領域とを対応付けてOCV領域ファイルを作成し、遅延ライブラリを用いてレイアウトされた回路に対して遅延計算を行い、遅延計算結果とOCV領域ファイルの領域ごとの第2OCV係数を用いてタイミング解析を行う。

(もっと読む)

半導体設計支援装置、タイミング制約生成方法、およびプログラム

【課題】半導体集正規回路の設計時に論理合成以後にあたる下流工程に用いる設計ツールに、設計者に依存することなく適切なタイミング制約を与える。

【解決手段】半導体設計支援装置に、非同期回路を内在する電気回路の設計時に ソースコードに対して行われたCDC検証結果と 当該ソースコードのコーディングに用いられた仕様策定工程で定められた既知情報とから、ソースコードに含まれる全てのクロックについて明確化処理してCDC検証用設定ファイルとして収集取得する手段と、CDC検証用設定ファイルとCDC検証結果から得られた非同期パス毎の入出力パスと から、下流工程で用いられる設計ツールで読み込み可能な形式に合わせるように所定の情報を抽出処理してタイミング制約ファイルを生成出力する手段を設ける。

(もっと読む)

設計支援装置及び設計支援方法

【課題】設計効率の向上を図ること。

【解決手段】設計支援装置10は、既存の半導体集積回路に含まれる機能マクロの情報と、機能マクロ間の接続情報を含むアーキテクチャ情報が品種毎に管理されたデータベースから、作成する半導体集積回路に搭載する機能マクロを含む品種を検索する。そして、設計支援装置10は、検索により得られた品種のアーキテクチャ情報を前記データベースから抽出し、作成する半導体集積回路のアーキテクチャ情報と、抽出した前記品種のアーキテクチャ情報を比較し、設計する半導体集積回路のアーキテクチャ情報に類似するアーキテクチャ情報の品種を抽出する。

(もっと読む)

クロックツリー生成装置及びクロックツリー生成方法

【課題】クロック遅延などを調整し易くすることで、タイミングエラーを適切に収束させる。

【解決手段】クロックツリー生成装置は、クロックツリーに関する情報と、クロックツリーに含まれる複数のフリップフロップが用いている複数のクロックに関する情報とを取得する取得手段と、取得手段によって取得された複数のクロックごとに、それぞれのクロックで駆動されるフリップフロップの数を特定するフリップフロップ数特定手段と、フリップフロップ数特定手段によって特定された複数のクロックごとのフリップフロップの数に基づいて、複数のクロックの中でフリップフロップの数が少ない上位のクロックを所定数だけ特定するクロック特定手段と、クロック特定手段によって特定されたクロックで駆動されるフリップフロップを基準にして、クロックツリーを分割する分割手段と、を備える。

(もっと読む)

設計支援装置、制御方法および制御プログラム

【課題】配線の効率化を図ること。

【解決手段】設計支援装置1は、表示部2に接続されており、記憶部1aと、選択部1bと、配置部1cと、判断部1dと、配線部1eと、確定部1fとを有している。記憶部1aは、回路の論理接続情報と配置対象のセルのセル情報を記憶する。選択部1bは、記憶部1aに記憶されたセル情報のうち、配置対象のセルのセル情報を選択する。配置部1cは、入力された座標に基づき、選択されたセル情報のセルの仮の配置を行う。判断部1dは、配線モードであるか否かを判断する。配線部1eは、判断部1dが配線モードであると判断した場合、仮の配置がされたセルに接続する配線について仮の配線を行う。確定部1fは、セルの配置位置の確定に基づいて、配線されたセルの仮の配線の配置位置を確定する。

(もっと読む)

LSIの電源遮断領域拡張方法及びそのプログラム

【課題】LSIにおける電源遮断領域を拡張する方法及びそのプログラムを提供する。

【解決手段】回路要素とネット情報とを記述したハードウエア記述ファイルに対して,電源遮断領域の入力端子Aから第1のノードBであるラッチ回路または入力ポートをトレースによって抽出し,さらに,遮断領域の出力端子に接続される第1のアイソレーションセルの出力端子A’から第2のノードB’であるラッチ回路または出力ポートをトレースによって抽出する第1の抽出工程と,第1のノードBから第3のノードCとなるラッチ回路または出力ポートをトレースによって抽出し,さらに,第2のノードB’から第4のノードC’であるラッチ回路または入力ポートをトレースによって抽出する第2の抽出工程とにより,無駄に動作する組み合せ回路を抽出し、前記回路をハードウエア記述ファイルと電源仕様ファイルに追加するとともに,アイソレーションセルを移動する工程とを有する。

(もっと読む)

半導体集積回路及びその設計方法

【課題】消費電力を削減した半導体集積回路及びその設計方法を提供する。

【解決手段】半導体集積回路の設計方法は、複数の標準フリップフロップ回路及び低消費電力フリップフロップ回路を配置するステップと、セルタイプを指標に含む評価関数を用いて、配置されたフリップフロップ回路を複数のクラスタにグループ化するステップと、標準フリップフロップ回路のみで構成されたクラスタに対して第1クロックバッファを割り当て、低消費電力フリップフロップ回路を含むクラスタに対して前記第1クロックバッファよりサイズの大きい第2クロックバッファを割り当てるステップと、クロック配線するステップと、を備える。

(もっと読む)

レイアウト設計装置、レイアウト設計方法、及びレイアウト設計プログラム

【課題】

複数階層を有する半導体集積回路の階層レイアウトを行なう際に、複数個所で使用される下位モジュールについての各配置箇所における下位モジュール近傍の上位階層の配線状況を考慮して、下位モジュールのレイアウト設計を行なうことを課題とする。

【解決手段】

上記課題を解決するために、本発明に係るレイアウト設計装置は、複数階層を有する半導体集積回路のレイアウト設計装置であって、複数個所で使用される下位モジュールについて、前記下位モジュールが配置される上位モジュール内のそれぞれの配置箇所近傍の上位階層の配線情報を抽出し、抽出した上位階層の配線情報を、前記下位モジュールのレイアウト設計を行なう際の配線禁止領域として設定し、前記下位モジュールのレイアウトを行なう。

(もっと読む)

ガードリング設計装置、ガードリング設計方法、プログラム及び記録媒体

【課題】半導体集積回路の素子及び配線のレイアウトにおけるガードリングの設計の自由度を高める。

【解決手段】設計装置は、デザインルールを記憶するデザインルール記憶部11、予め設計されたレイアウトを記憶するレイアウト記憶部12、デザインルールに適合したガードリング幅を設定幅として設定するガードリング幅設定部21、レイアウト上にガードリングの形成経路を指定するための経路指定部32、指定経路に基づいてガードリング形成経路を認識する経路認識部22、ガードリング形成用のレイヤーリストを記憶するガードリング形成用レイヤー記憶部13、認識経路の下地レイヤーに応じたガードリング形成用のレイヤーを設定するガードリング形成用レイヤー設定部23及び認識経路に設定幅で設定レイヤーを反映させてガードリングを生成するガードリング生成部24を備えている。

(もっと読む)

半導体集積回路のレイアウト装置

【課題】 本発明の課題は、半導体集積回路のレイアウト処理におけるセル配置の際に、隣り合う2つのセルの特性を考慮した配置によって最適化することことを目的とする。

【解決手段】 上記課題は、隣接して配置されるセルの組み合せ毎にショート可否とセル枠のオーバーラップ可能な距離との対応付けを含む最適化ライブラリを格納する第一記憶領域と、デザインルールを満たすセル配置において、前記第一記憶領域に格納されている前記最適化ライブラリを参照することによって、前記ショート可能なセルの組み合せに対して前記セル枠をオーバーラップさせて配置する第一最適化手段とを有することを特徴とする半導体集積回路のレイアウト装置により達成される。

(もっと読む)

フロアプランデータ生成装置及び方法

【課題】チップの設計期間を短縮する。

【解決手段】CPU1は、設計対象の回路を構成するセルのうち、所定のサイズより大きいセルサイズを有するセルのみの回路情報をゲートレベルで記述した簡易ネットリスト43と、所定のサイズより大きいセルサイズを有するセルのみの仕様データを含むセルリスト44とを用いてフロアプランを行い、仮フロアプランデータ47を生成する。CPU1は、ユーザによって回路全体のフロアプランが行われるときに、回路を構成するセルの仕様データである全体ライブラリ42と、回路を構成するセルの回路情報をゲートレベルで記述した全体ネットリスト45と、仮フロアプランデータ47と、簡易ネットリスト43を全体ネットリスト45に整合させるためのセルリスト44とを出力する。

(もっと読む)

半導体集積回路のレイアウト装置及びレイアウト方法

【課題】集積度の高い半導体集積回路の場合でもレイアウト設計における配線に係る時間を短縮する。

【解決手段】半導体集積回路のレイアウト方法は、回路構成要素の配置された領域へ配線を実施後に、予め設定された条件よりも配線が混雑する配線混雑箇所を抽出するステップと、配線混雑箇所を含む領域に、配線の実施が禁止される複数の配線禁止領域を生成するステップと、複数の配線禁止領域を迂回して配線を実施するステップと、迂回して配線を実施した後に、複数の配線禁止領域を削除するステップと、複数の配線禁止領域を削除した後に、再配線を実施するステップとを具備する。複数の配線禁止領域を生成するステップは、配線層毎に、配線の混雑に対応した領域内に配線禁止領域を発生させる割合に基づいて、複数の配線禁止領域の大きさ及び間隔を算出するステップと、算出結果に基づいて、領域に複数の配線禁止領域を生成するステップとを備える。

(もっと読む)

パス調整方法及び設計支援装置

【課題】設計期間の短縮化を図ること。

【解決手段】設計支援装置は、クロックツリー合成処理(ステップ23)にて生成したクロックツリーに含まれるクロックパスについて、電圧・温度の遅延感度をそれぞれ算出し、2つのクロックパスの遅延感度の差を0に近づけるように、クロックパスの遅延感度を調整する。

(もっと読む)

半導体装置の製造方法

【課題】 ソース領域側だけに不活性イオン注入領域が形成される非対称型SOI電界効果トランジスタを容易に実現する半導体装置の製造方法を提供する。

【解決手段】 イオン注入前にトランジスタが形成される半導体層のゲート電極について対称構造をなす2つの電極のいずれか一方をソース又はドレインとして指定する電極指定データを予め保持する設計工程と、電極指定データに応じてソース領域側だけのイオン注入を可能にするためのイオン注入用マスクを製作するマスク製作工程と、対称をなす2つの電極を有する半導体層表面にフォトレジストを塗布しイオン注入用マスクを用いて露光してフォトレジストの少なくともソース領域に対応する部分を除去するレジスト形成工程と、レジスト形成工程の実行後、イオン注入用マスクに対応して残されたフォトレジストを有する半導体層表面からイオンを注入する工程と、を備える。

(もっと読む)

設計装置、設計方法、及び設計プログラム

【課題】タイミング違反の修正の問題を解消する。

【解決手段】設計装置10は、クロックツリーを生成するクロックツリー生成部121と、クロックツリー生成部121により生成されたクロックツリーに対応する回路データについて、セットアップタイミングを考慮せずにホールド違反を修正するように、遅延素子を論理的に挿入する論理修正部122と、論理修正部122の処理結果に基づいて、半導体集積回路のレイアウトを修正するレイアウト修正部123と、レイアウト修正部123により修正された半導体集積回路のレイアウトを出力する出力部124と、を備える。

(もっと読む)

1 - 20 / 247

[ Back to top ]