Fターム[5F082BA19]の内容

Fターム[5F082BA19]に分類される特許

1 - 9 / 9

バイポーラ・トランジスタ及びその製造方法

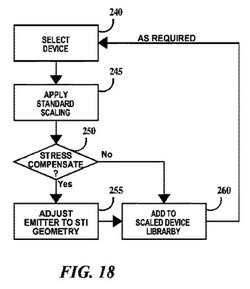

【課題】 バイポーラ・トランジスタ構造体、バイポーラ・トランジスタを設計し製造する方法、及びバイポーラ・トランジスタを有する回路を設計する方法を提供する。

【解決手段】 バイポーラ・トランジスタを設計する方法は、バイポーラ・トランジスタの初期設計を選択するステップ(図25の240)と、バイポーラ・トランジスタの初期設計をスケーリングしてバイポーラ・トランジスタの縮小設計を生成するステップ(245)と、バイポーラ・トランジスタの縮小設計の応力補償が必要かどうかを、スケーリング後のバイポーラ・トランジスタのエミッタの寸法に基づいて判断するステップ(250)と、バイポーラ・トランジスタの縮小設計の応力補償が必要な場合に、縮小設計のトレンチ分離レイアウト・レベルのレイアウトを、縮小設計のエミッタ・レイアウト・レベルのレイアウトに対して調節して(255)バイポーラ・トランジスタの応力補償縮小設計を生成するステップ(260)と、を含む。

(もっと読む)

半導体装置

【課題】 同一基板上に形成された半導体素子間に流れる寄生電流による半導体素子の誤動作を抑制する構造を有する半導体装置を提供することを目的とする。

【解決手段】

p型半導体基板1に電気的に接続されたn型のコレクタ引き出し層53を備えた小信号素子であるバイポーラトランジスタ50と、p型半導体基板1に電気的に接続されたn型拡散層67を備えたパワートランジスタ素子であるDMOSトランジスタ60と、p型半導体基板1に電気的に接続され、かつ、ダミー電極13に接続されたn型のダミーN島10と、p型半導体基板1に電気的に接続され、かつ、フィールド電極23に接続されたp型のフィールド部20と、ダミー電極13とフィールド電極23を接続し、ボンディングパット70に接続する配線30とを備える。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】半導体集積回路装置の設計工数を低減する。

【解決手段】SOI基板1の半導体層において、互いに完全に電気的に分離された複数の単位バイポーラトランジスタQuを並列接続することにより、大電流容量を必要とするバイポーラトランジスタを構成する。また、所望の電流容量を与えるトランジスタは、幾何学的寸法が、実質的に同一サイズである複数の単位バイポーラトランジスタを、互いに電気的に並列接続することにより構成する。

(もっと読む)

バンドギャップ基準電圧発生回路

【課題】光照射による電圧変動が低減されたバンドギャップ基準電圧発生回路を提供する。

【解決手段】第1導電型の半導体からなる基板と、前記基板上に形成された第1のトランジスタと、前記基板上に形成され、前記第1のトランジスタに対してベースが共通に接続された第2のトランジスタと、前記基板上に形成され、第2導電型を有し、前記第2のトランジスタのコレクタ層と前記基板との間に並列に接続された光吸収領域と、前記第1及び第2のトランジスタの前記ベースに共通接続された基準電圧出力端子と、を備え、前記第1のトランジスタのコレクタ層の面積は、前記第2のトランジスタの前記コレクタ層の面積よりも大きいことを特徴とするバンドギャップ基準電圧発生回路が提供される。

(もっと読む)

半導体装置

【課題】バイポーラトランジスタを用いたESD保護回路の面積効率を向上する。

【解決手段】集積回路は、回路用バイポーラトランジスタ124を含む内部回路121と、内部回路121をサージから保護するための保護用バイポーラトランジスタ120とを備え、保護用バイポーラトランジスタ120におけるエミッタとベースとは短絡されている。

(もっと読む)

半導体装置

【課題】高電圧側絶縁分離トレンチの寿命を延ばすことができる半導体装置を提供すること。

【解決手段】埋め込み酸化膜30を有する半導体基板に、低電圧素子201が複数形成された低電圧回路領域200と高電圧素子301が複数形成された高電圧回路領域300とが設けられた半導体装置であって、高電圧回路領域300を囲い、埋め込み酸化膜30に達するように形成された絶縁分離トレンチ61と、絶縁分離トレンチ61にて囲われた領域内において、埋め込み酸化膜30に達するように形成された絶縁分離トレンチ62と、絶縁分離トレンチ62によって囲われた各高電圧素子301が形成された高電圧側素子形成領域e2と、絶縁分離トレンチ61と絶縁分離トレンチ62との間の素子が形成されない高電圧側フィールド領域f2とを備え、高電圧側素子形成領域e2の電位と高電圧側フィールド領域f2の電位とを略同電位とする。

(もっと読む)

貼り合わせ基板の製造方法およびそれによって製造される貼り合わせ基板

【課題】安価に製造することができ、そこに形成される各種半導体素子の特性を阻害することなく高集積化できる貼り合わせ基板の製造方法および貼り合わせ基板を提供する。

【解決手段】SOI層1aとなる第1基板11aの一方の第1面1S側に、埋め込み絶縁分離トレンチTを形成する、埋め込み絶縁分離トレンチ形成工程と、第1面1S側に、埋め込み拡散層1b,1cとなる不純物層1ib,1icを形成する、不純物層形成工程と、第1基板11aにおける第1面1S側を支持基板2となる第2基板11bに対向するようにして積層し、第1基板11aと第2基板11bを互いに貼り合わせる、基板貼り合わせ工程と、貼り合わされた第1基板11aのもう一方の第2面2S側を研磨して、埋め込み絶縁分離トレンチTを基板表面に露出し、SOI層1aとする基板研磨工程とを有する貼り合わせ基板11の製造方法とする。

(もっと読む)

通信用電力増幅器

【課題】デュアルバンド電力増幅器の最終段トランジスタにおける電流集中を、バンド間アイソレーションを劣化させることなく回避する。

【解決手段】最終段電力増幅トランジスタ(Trg3,Trd3)の単位トランジスタについて、最終出力増幅トランジスタ形成領域(PW3)内に単位トランジスタを交互にまたは取囲むように混在して配置する。また、これらの最終出力段トランジスタが結合する出力信号線の間に、インダクタンス素子(Lcc)を接続する。

(もっと読む)

電子回路及び電子回路の製造方法

【課題】回路の特定部分における過熱を回避し、回路一面に適切な温度分布を実現する電子回路を提供する。

【解決手段】本発明にかかる電子回路は、第1端子(100)と、第2端子(200)と、並列に配列された少なくとも3つのトランジスタ(1)とを備え、各トランジスタは、前記第1端子(100)に接続され、制御信号を受け入れる制御端子(2)と、前記第2端子(200,300)に接続され、前記制御信号に依存した出力信号を供給する出力端子(3,4)とを有する。前記トランジスタ(1)は、他のトランジスタから受ける熱に起因するトランジスタの配熱が全ての前記トランジスタにおいて略同一になるように、対称点を基準に対称に配列されている。本発明はまた、電子回路の製造方法にも関する。

(もっと読む)

1 - 9 / 9

[ Back to top ]