Fターム[5F083BS16]の内容

Fターム[5F083BS16]の下位に属するFターム

LDD(Lightly Doped Drain) (149)

Fターム[5F083BS16]に分類される特許

61 - 61 / 61

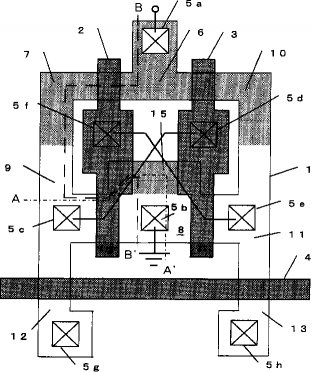

半導体装置及びその製造方法

【課題】 より優れたソフトエラー耐性を有するSOI基板を用いた高信頼性のCMOS・SRAMセルを備える半導体装置及びその製造方法を提供することを目的とする。

【解決手段】 SOI基板の表面半導体層上にゲート絶縁膜を介して形成されたゲート電極と、該ゲート電極の両側の表面半導体層に形成された第1導電型ソース/ドレイン領域とから構成される半導体装置であって、前記第1導電型ソース/ドレイン領域の双方又は一方に接して第2導電型引出拡散層が形成され、少なくとも前記第1導電型ソース/ドレイン領域上から第2導電型引出拡散層上にわたってシリサイド層が形成されており、シリサイド層に接地電位が与えられてなる半導体装置。

(もっと読む)

61 - 61 / 61

[ Back to top ]