Fターム[5F083BS30]の内容

Fターム[5F083BS30]に分類される特許

21 - 25 / 25

半導体装置及びその製造方法、並びにメモリ回路

【課題】本発明は、ボディ浮遊効果を抑制することが可能な半導体装置及びその製造方法を提供する。

【解決手段】シリコン基板1と、シリコン基板1上に形成された埋め込み絶縁層2と、埋め込み絶縁層2上に形成された半導体層3とを備えるSOI構造の半導体装置であって、半導体層3は、第1導電型のボディ領域4、第2導電型のソース領域5及び第2導電型のドレイン領域6を有し、ソース領域5とドレイン領域6との間のボディ領域4上にゲート酸化膜7を介してゲート電極8が形成され、ソース領域5は、第2導電型のエクステンション層52と、エクステンション層52と側面で接するシリサイド層51を備え、シリサイド層51とボディ領域4との境界部分に生じる空乏層の領域に結晶欠陥領域12が形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】 ON状態/OFF状態に加えて、OFF状態よりも大きくON状態よりも小さい電流がソース/ドレイン領域間に流れるリークモードを有する半導体装置およびその製造方法を提供する。

【解決手段】 トランジスタ1は、第1と第2ゲート電極G1,G2を備える。第1と第2ゲート電極は、同一のソース/ドレイン領域を共有し、第1と第2トランジスタが形成される。第1と第2ゲート電極G1,G2にはそれぞれ独立して電圧が印加される。トランジスタ1は、少なくとも第1トランジスタがON状態である第1の状態(ON状態)と、第1と第2トランジスタG1,G2がOFF状態である第2の状態(OFF状態)と、第1トランジスタがOFF状態であり第2トランジスタがON状態である第3の状態(リークモード)とを実現する。

(もっと読む)

半導体装置

【課題】 半導体基板の主表面に対して平行な方向における面積を小さくすることができる薄膜トランジスタを有するラッチ回路を備えた半導体装置を提供する。

【解決手段】 1つのメモリセル領域100を横切る同一層に形成されたビット線15および他のビット線とは別の層にグラウンド配線層16が形成されている。このグラウンド配線層16は、メモリセル領域100内のほぼ全ての領域にわたって形成されている。また、メモリセル領域100内においてプラグ18および19がグラウンド配線層16を上下に貫通しているが、絶縁膜18aおよび絶縁膜19aによってグラウンド配線層16とプラグ18および19のそれぞれとが絶縁されている。

(もっと読む)

半導体装置およびその製造方法

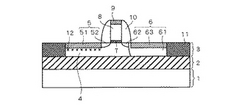

【課題】ボディコンタクトを有するSOIデバイスにおいて、ボディコンタクトとボディ領域との間に所望の抵抗値を持たせると共に、当該抵抗値のばらつきを抑制する。

【解決手段】SOI層3におけるコンタクト61との接続部分(即ち、素子分離絶縁膜41の下)に、不純物濃度の高いP+領域を形成せずに、SOI層3とボディコンタクト61とをショットキー接合させる。また、ボディコンタクト61の表面にはバリアメタル61aが形成されており、ボディコンタクト61とSOI層3との間に、バリアメタル61aとSOI層3とが反応したシリサイド70が形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】 より優れたソフトエラー耐性を有するSOI基板を用いた高信頼性のCMOS・SRAMセルを備える半導体装置及びその製造方法を提供することを目的とする。

【解決手段】 SOI基板の表面半導体層上にゲート絶縁膜を介して形成されたゲート電極と、該ゲート電極の両側の表面半導体層に形成された第1導電型ソース/ドレイン領域とから構成される半導体装置であって、前記第1導電型ソース/ドレイン領域の双方又は一方に接して第2導電型引出拡散層が形成され、少なくとも前記第1導電型ソース/ドレイン領域上から第2導電型引出拡散層上にわたってシリサイド層が形成されており、シリサイド層に接地電位が与えられてなる半導体装置。

(もっと読む)

21 - 25 / 25

[ Back to top ]