Fターム[5F083BS42]の内容

Fターム[5F083BS42]に分類される特許

1 - 5 / 5

半導体装置およびその製造方法

【課題】オフ電流を増加させることなく電源供給配線の電気抵抗を下降させることが可能な、TFTを有する半導体装置を提供することである。

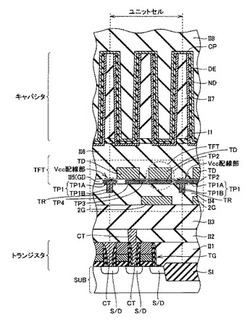

【解決手段】表面を有する絶縁膜II4と、絶縁膜II4の表面上に形成され、かつチャネル領域TP2と、チャネル領域TP2を挟む1対のソース/ドレイン領域TP1,TP4とを含む半導体層と、ソース領域TP1に電源を供給するための電源供給配線TP1とを備えている。上記絶縁膜II4の表面には凹部TRが形成されている。上記電源供給配線TP1は、半導体層と同一の層から形成された層を含み、かつ絶縁膜II4の表面上に形成された第1の部分TP1Aと、凹部内に形成された第2の部分TP1Bとを有している。上記第2の部分TP1Bの底面全体が絶縁体II4で覆われている。

(もっと読む)

半導体記憶装置、及び半導体記憶装置の製造方法

【課題】半導体記憶装置の面積を縮小する技術を提供する。

【解決手段】高抵抗付加型ラッチ回路(12)と、その高抵抗付加型ラッチ回路(12)に保持されるデータの読み出しと書込みとを制御する選択回路(13)とを具備する半導体記憶装置(11)を構成する。その高抵抗付加型ラッチ回路(12)は、第1駆動トランジスタ(22)と、第2駆動トランジスタ(24)と、第1抵抗(121)と、第2抵抗(123)とを備えることが好ましい。また、その選択回路(13)は、第1選択トランジスタ(31)と、第2選択トランジスタ(32)とを備えることが好ましい。ここにおいて、その第1抵抗(121)と第2抵抗(123)とは、サイドウォール状の導電性材料(21)(23)で形成されるものである。

(もっと読む)

半導体装置

【課題】SRAM回路の動作速度を向上させる。

【解決手段】駆動MISFETと転送MISFETとそれらの上部に形成された縦型MISFETとでメモリセルを構成したSRAMにおいて、周辺回路を構成するMISFET間の電気的接続を、メモリセルの縦型MISFET(SV1、SV2)よりも下部に形成されるプラグ28および中間導電層46、47で行うとともに、縦型MISFET(SV1、SV2)よりも上部に形成されるプラグ、第1および第2金属配線層を用いて行うことにより、配線の自由度を向上でき、高集積化できる。また、MISFET間の接続抵抗を低減でき、回路の動作スピードを向上できる。

(もっと読む)

半導体装置及びその製造方法

【課題】SOIウエハ上に、従来のCMOSプロセスと親和性のよいプロセスで、面積を増大させることなく、高抵抗素子タイプのSRAMの構造及びその製造方法を提供する。

【解決手段】半導体装置は、シリコン支持基板130と、支持基板130上に形成される絶縁層132と、絶縁層132上に形成されるSOI層134とからなるSOI基板を用いて製造されるSRAMに適用される。そして、ホトリソとエッチングで所望の領域に支持基板130に達するホール142を形成し、ポリシリコン114を堆積して、シリコン支持基板130に達するポリシリコンプラグによって形成される抵抗素子150を備えている。

(もっと読む)

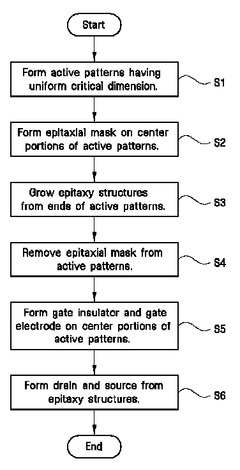

均一な臨界寸法のアクティブパターンで形成されたマルチゲートトランジスタ及びその製造方法

本発明は、均一な臨界寸法のアクティブパターンで構成されたマルチゲートトランジスタの製造方法を提供する。本発明はまた、均一な臨界寸法のアクティブパターンを具備するマルチゲートトランジスタを提供する。マルチゲートトランジスタの製造方法は先に少なくとも一つのアクティブパターンを形成する。以後、前記アクティブパターンの露出した領域から少なくとも一つのエピタキシ構造を成長させる。続いて、前記アクティブパターンの少なくとも2個の面にチャネル領域を形成する。  (もっと読む)

(もっと読む)

1 - 5 / 5

[ Back to top ]