Fターム[5F083EP72]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423) | 拡散領域 (1,645) | トンネル拡散領域 (17)

Fターム[5F083EP72]に分類される特許

1 - 17 / 17

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得る。

【解決手段】トンネル領域を有する半導体不揮発性メモリにおいて、トンネル領域の周囲部分は掘り下げられており、掘り下げられたドレイン領域には、空乏化電極絶縁膜を介して、トンネル領域の一部を空乏化するための電位を自由に与えることが可能な空乏化電極を配置する。

(もっと読む)

半導体不揮発性メモリ装置

【課題】 占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得ることを目的とする。

【解決手段】 ドレイン領域内のトンネル領域と微細穴に埋め込まれる形で形成されたフローティングゲート電極の側面との間にはトンネル絶縁膜を設け、微細穴に接するドレイン領域の表面付近には、電気的にフローティング状態である第1導電型のトンネル防止領域を設けた。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得ることを目的とする。

【解決手段】ドレイン領域内のトンネル領域には、ドレイン領域と同一の電位に固定されたドレイン領域に比べて不純物濃度の低い第2導電型の領域と、不純物濃度の低い第1導電型の領域とを形成し、不純物濃度の低い第2導電型の領域と、不純物濃度の低い第1導電型の領域のそれぞれの上面に、フローティングゲート電極への電子注入用と電子引き抜き用のトンネル絶縁膜を独立して設けた。また、データ書き換え時に印加されるストレスが偏らないように、電子引き抜き用のトンネル絶縁膜に比べて電子注入用のトンネル絶縁膜の面積を大きくあるいは厚くした。

(もっと読む)

半導体不揮発性メモリ装置

【課題】トンネル絶縁膜にエッジ部があることによるトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得る。

【解決手段】トンネル絶縁膜の上部であって、トンネル領域のエッジ部から離間した位置に、電荷受け渡し用電極を配置し、電荷受け渡し用電極とフローティングゲート電極とが、電気的に接続されるようにした。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】スプリットゲート型メモリセル構造を採用し、電荷蓄積層として窒化膜を用いる不揮発性メモリを有する半導体装置において電気的特性を向上させる。

【解決手段】半導体基板1Subの主面にn型の半導体領域6を形成した後、その上にスプリットゲート型のメモリセルのメモリゲート電極MGおよび電荷蓄積層CSLを形成する。続いて、そのメモリゲート電極MGの側面にサイドウォール8を形成した後、半導体基板1Subの主面上にフォトレジストパターンPR2を形成する。その後、フォトレジストパターンPR2をエッチングマスクとして、半導体基板1Subの主面の一部をエッチングにより除去して窪み13を形成する。この窪み13の形成領域では上記n型の半導体領域6が除去される。その後、その窪み13の形成領域にメモリセル選択用のnMISのチャネル形成用のp型の半導体領域を形成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセル間の干渉を抑制できる不揮発性半導体記憶装置を提供する。

【解決手段】NAND型メモリ1において、半導体基板11の表面上に、トンネル絶縁層12、電荷蓄積層13、電荷ブロック層14を設け、その上に、チャネル長方向に沿ってそれぞれ複数の制御ゲート電極15及びセル間絶縁膜16を交互に設ける。そして、電荷ブロック層14におけるセル間絶縁膜16の直下域に相当する部分14bに塩素を導入し、部分14bの誘電率を電荷ブロック層14における制御ゲート電極15の直下域に相当する部分14aの誘電率よりも低くする。

(もっと読む)

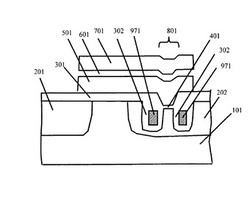

半導体装置

【課題】セルサイズのさらなる縮小を図ることができる、半導体装置を提供すること。

【解決手段】半導体層2に、トレンチ5が形成されている。半導体層2の表層部には、第1拡散領域3およびドレイン領域が形成されている。第1拡散領域3は、トレンチ5に対して所定方向の一方側に形成され、トレンチ5に隣接している。第2拡散領域6は、所定方向においてトレンチ5に対して第1拡散領域3と反対側に形成され、トレンチ5に隣接している。トレンチ5の底面および側面上には、第1絶縁膜8が形成されている。第1絶縁膜8上には、フローティングゲート11が設けられている。フローティングゲート11は、第1絶縁膜8を挟んで、トレンチ5の底面および側面と対向している。フローティングゲート11上には、第2絶縁膜12が形成されている。第2絶縁膜12上には、コントロールゲート13が設けられている。

(もっと読む)

不揮発性半導体記憶装置

【課題】選択トランジスタに隣接するメモリセルの誤書き込みを抑制する。

【解決手段】シリコン基板11上に絶縁膜12を介して浮遊ゲート13と制御ゲート15とが積層された構造を有する複数のメモリセルMCを直列に接続してなるメモリセル列と、このメモリセル列の両端と共通ソース線及びビットBL線との間に接続された選択トランジスタST1,ST2とを備えた不揮発性半導体記憶装置において、選択トランジスタST1と、これに隣接するメモリセルMC0との間のシリコン基板の表面に凹部19が形成され、凹部19の選択トランジスタST1側のエッジが選択トランジスタST1のメモリセルMC0側の端部に接している。

(もっと読む)

FLOTOX型EEPROM

【課題】FLOTOX型EEPROMにおいて、ドレイン領域の接合耐圧を低下させることなく、十分に高い書き込み電圧を印加できる構成で、かつ、セル面積が縮小されたものが望まれていた。

【解決手段】トンネルウインドウ12を有し、トンネルウインドウ12を介して電子の注入、引き抜きを行える整列配置された複数のフローティングゲート11と、複数のフローティングゲート11に個別に対応付けて設けられた複数のセレクトゲート13と、複数のフローティングゲート11に共有に設けられたコントロールゲート16と、複数のフローティングゲート11に共有に設けられたソース17と、複数のフローティングゲート11に共有に設けられたドレイン18とを含む構成とする。

(もっと読む)

FLOTOX型EEPROM

【課題】Wセル方式のFLOTOX型EEPROMの設計においては、微細化のため、セルのレイアウトを工夫しなければならないという課題があった。

【解決手段】Wセル方式のFLOTOX型EEPROMとするため、対をなす2つのフローティングゲート25a,25bと、2つのトンネルウインドウ30a,30bと、共有のソース27と、共有のコントロールゲート26と、セレクトゲート29a,29bとを設けるとともに、ドレイン28を共有とした。

【効果】高信頼性設計、高耐圧設計が実現されたWセル方式のFLOTOX型EEPROMを実現できる。

(もっと読む)

FLOTOX型EEPROM

【課題】Wセル方式のFLOTOX型EEPROMの設計においては、微細化のため、セルのレイアウトを工夫することが必須であるという課題があった。

【解決手段】Wセル方式のFLOTOX型EEPROMとするため、対をなす2つのフローティングゲート25a,25bと、2つのトンネルウインドウ30a,30bと、2つのソース26a,26bと、共有のコントロールゲート31と、共有のセレクトゲート32とを設けるとともに、ドレイン27も共有とした。

【効果】高信頼性設計、高耐圧設計が実現されたWセル方式のFLOTOX型EEPROMを実現できる。

(もっと読む)

第1の酸化物層および第2の酸化物層を形成するための方法

【課題】非常に薄い酸化物層の品質を改良するための方法を提供する。

【解決手段】濃くドープされたN+層上の半導体本体の表面領域上にかつゲート領域の表面上に初期の酸化物層(104)を形成するために半導体本体をはじめに酸化させることによって、EEPAL装置などのプログラマブル装置に適切な高品質のトンネル酸化膜が濃くドープされたN+層上の半導体本体の表面領域上に形成され、さらにゲート酸化膜がゲート領域上に形成される。次に、濃くドープされたN+層の上層の初期の酸化物層(104)の少なくとも一部分が取除かれる。初期の酸化膜の残りの部分の厚みを増しそれによってゲート酸化膜を形成するために、さらに濃くドープされたN+層上にトンネル酸化膜を形成するために、半導体本体は酸化に適切な環境にその後さらされる。半導体本体を窒素源に導入することによって、ある濃度の窒素がゲートおよびトンネル酸化膜両方に導入される。

(もっと読む)

NAND型不揮発性メモリのデータ消去方法

【課題】NAND型不揮発性メモリの消去動作として、PウェルやNウェルなどの基板端子を用いないで、不揮発性メモリ素子における電荷蓄積部に注入された電荷を放出する、すなわちNAND型不揮発性メモリのデータの消去動作する方法を提供することを課題とする。

【解決手段】NAND型不揮発性メモリにおけるデータの消去方法において、不揮発性メモリ素子における電荷蓄積層に格納された電荷の放出について、ビット線、ソース線、及び制御ゲートに電位を印加することにより行う。そして、不揮発性メモリ素子における電荷蓄積層に格納された電荷の放出を、電荷を放出する不揮発性メモリ素子のソース端子、ドレイン端子、及び制御ゲートに電位を印加することにより行う。

(もっと読む)

EEPROM及びその製造方法

【課題】EEPROM及びその製造方法を提供する。

【解決手段】メモリトランジスタ領域及び選択トランジスタ領域を含む半導体基板の所定領域に活性領域を定義する素子分離膜パターンを形成し、活性領域上にトンネル領域を有するゲート絶縁膜を形成し、ゲート絶縁膜が形成された結果物上に第1導電膜を形成した後、第1導電膜をパターニングして素子分離膜パターンの上部面を露出させる開口部を形成する段階を含む。この時、開口部とこれに隣接する活性領域との間の距離を選択された開口部の下の素子分離膜パターンの幅によって変えるように形成する。

(もっと読む)

不揮発性メモリ素子

【課題】本発明は集積度を向上させた不揮発性メモリ素子を提供する。

【解決手段】本発明の不揮発性メモリ素子は、一対のメモリトランジスタと一つの選択トランジスタで構成されたメモリセルユニットで構成される。選択トランジスタは半導体基板内の活性領域に形成された一対のメモリトランジスタの間に配置される。互いに異なる2つのビットラインが一対のメモリトランジスタにそれぞれ連結される。

(もっと読む)

不揮発性メモリ及びその製造方法

【課題】 センス電圧のマージンを大きくし、従来に比べてより厳しい条件下において不揮発性メモリの書き換え寿命を向上させ、更に不揮発性メモリとしての信頼性を高めることを可能とした不揮発性メモリ及びその製造方法を提供する。

【解決手段】 基板16のアクティブ領域102と浮遊ゲート電極12との間に介在するトンネル酸化膜領域13aを有し、このトンネル酸化膜領域13aはその平面視での形状が円形であり、且つその直径が0.64μm以上、0.76μm以下となっている。このような構成であれば、メモリセルの書き換え寿命を向上できる。

(もっと読む)

不揮発性半導体記憶装置

【課題】 2層ゲート構造であって、コントロールゲート5の表面上に紫外線を透過しない膜を備える場合であっても、紫外線照射により、フローティングゲート4の電荷を平衡状態にすることができる不揮発性半導体記憶装置を提供する。

【解決手段】 例えば、2層ゲート構造のEEPROMにおいて、フローティングゲート4の形状を、突出部21を有する形状とする。そして、この突出部21を、フィールド領域2上であって、平面レイアウトにおいて、コントロールゲート5から突きだすように配置する。このようにして、フローティングゲート4の一部(突出部の一部)22をコントロールゲート5から露出させる。これにより、EEPROMが、コントロールゲート5の表面上に、WSi2膜6のような紫外線を透過しない膜を備える場合であっても、紫外線照射により、フローティングゲート4の電荷を平衡状態にすることができる。

(もっと読む)

1 - 17 / 17

[ Back to top ]