Fターム[5F083FR10]の内容

Fターム[5F083FR10]に分類される特許

1 - 20 / 61

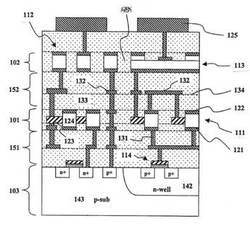

半導体構造

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、半導体構造を提供することを目的とする。

【解決手段】下部誘電層(151)へ接合された基板(103)、および、下部電極(121)を通じて前記下部誘電層(151)と接合される垂直方向半導体装置(111)を含む半導体構造であって、前記垂直方向半導体装置(111)は、n+−p−n+層(124)を有する隔離構造(135)を含む。

(もっと読む)

半導体記憶装置

【課題】強誘電体膜の膜質を均一化するチェインFeRAM型半導体記憶装置を提供する。

【解決手段】半導体記憶装置80は、同一素子形成領域に隣接配置される、一対のソース/ドレイン層5を有するメモリトランジスタTR1及びTR2と、メモリトランジスタのソース/ドレイン層5の他方とメモリトランジスタTR2のソース/ドレイン層5の一方に、ビア及びバリアメタル膜13を介して接続される強誘電体キャパシタCAP1及びCAP2とを有する。強誘電体キャパシタCAP1及びCAP2は、バリアメタル膜13上に設けられ、四角錐台形状の下部電極14と、下部電極14を覆うように設けられる強誘電体膜15とを共有し、強誘電体キャパシタCAP1は、強誘電体膜15上に設けられる第1の上部電極16aを有し、強誘電体キャパシタCAP2は、強誘電体膜15上に設けられ、第1の上部電極16aと離間して配置される第2の上部電極16bを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】強誘電体キャパシタの下部電極材料の選択自由度が高く、ビア工程の少ない半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板101上に形成されたスイッチングトランジスタ301A,301Bと、拡散層121と、トランジスタ301上に形成された層間絶縁膜131と、下部電極211、強誘電体膜212、及び上部電極213を含む強誘電体キャパシタ201A,201Bと、上部電極213の上方に形成された配線層141と、上部電極213と配線層141とを電気的に導通させる第1のプラグTWと、拡散層121と配線層141とを電気的に導通させる第2のプラグV1A,V1Bと、下部電極211の側方に配置されており、下部電極211と拡散層121とを電気的に導通させる第3のプラグCSFとを備える。

(もっと読む)

強誘電体記憶装置

【課題】強誘電体キャパシタの上部電極上にコンタクトプラグを容易に形成することができ、かつ、強誘電体キャパシタ上方の水素バリア膜の破損を抑制した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板10上に設けられた複数のトランジスタと、複数のトランジスタ上に設けられた第1の層間絶縁膜ILD1と、第1の層間絶縁膜ILD1上に設けられた複数の強誘電体キャパシタCと、複数の強誘電体キャパシタCの上面および側面を被覆する第1の水素バリア膜HB1と、強誘電体キャパシタCの上方に設けられ、並びに、隣接する2つの強誘電体キャパシタC間に間隙または空孔Hを有する状態で埋め込まれた第2の層間絶縁膜ILD2と、間隙または空孔Hの開口部を閉じるように第2の層間絶縁膜ILD2上を被覆するカバー絶縁膜CIと、カバー絶縁膜CI上を被覆する第2の水素バリア膜HB2とを備える。

(もっと読む)

半導体記憶装置

【課題】データ読出し動作において、不要なリストア動作を省略し、破壊されたデータのリストア時間を従来よりも長くすることができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、プレート駆動信号PDSと、データ書込みを示すライト信号WRITEと、センスアンプから外部へのデータ読出しまたは外部からセンスアンプへのデータ書込みの実行可能期間の終了を示す動作終了信号PRECHとを受け取り、ライト信号および動作終了信号に基づいてプレート駆動信号を有効または無効にするプレート制御回路PCCとを備え、プレート制御回路は、実行可能期間にプレート駆動信号を有効にし、プレート制御回路は、実行可能期間内に1度もライト信号が活性化されなかったときには実行可能期間終了時にプレート駆動信号を無効にし、実行可能期間内に少なくとも1度ライト信号が活性化されたときにはプレート駆動信号を有効にしたままにする。

(もっと読む)

半導体記憶装置

【課題】強誘電体キャパシタの面積を減少させることなく、チップサイズを縮小することができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、トランジスタを被覆する第1の層間膜と、第1の層間膜中に形成されトランジスタに接続された第1のプラグと、第1のプラグ上方に形成された強誘電体キャパシタと、隣接する強誘電体キャパシタ間の下にある第1の層間膜中に形成されトランジスタに接続された第2のプラグと、強誘電体キャパシタの配列方向に対してほぼ直交する第1の方向へ延伸している第1の配線と、第1の層間膜および第1の配線の上方に設けられた第2の層間膜と、第2の層間膜中に形成され、第2のプラグから第1の方向にシフトした位置において第1の配線に接続された第3のプラグと、第3のプラグと強誘電体キャパシタの上部電極とを接続する第2の配線とを備えている。

(もっと読む)

強誘電体メモリ

【課題】強誘電体メモリの信頼性を向上する。

【解決手段】本発明の例に関わる強誘電体メモリは、半導体基板50内に設けられる拡散層23,24と、拡散層23,24間のチャネル領域上にゲート絶縁膜を介して設けられるゲート電極21と、を有する電界効果トランジスタ2と、層間絶縁膜51内に埋め込まれ、拡散層23,24上に設けられるコンタクトプラグ30,31と、層間絶縁膜51上及びコンタクトプラグ30,31上に設けられる酸化防止膜40と、酸化防止膜40上に設けられる強誘電体膜10と、強誘電体膜10及び酸化防止膜40を貫通して、コンタクトプラグ30,31上に設けられる電極11,12と、を有するキャパシタ1と、電極11,12間の酸化防止膜40上に設けられ、強誘電体膜10に対して種結晶として機能するシード層41と、を具備する。

(もっと読む)

3次元垂直チャンネル構造を有する不揮発性メモリ装置のプログラム方法

【課題】本発明は、ビットラインとストリング選択ラインとの交差領域に各々形成され、各々が基板上に垂直に多層構造で形成されたメモリセルを有するストリングを含む不揮発性メモリ装置のプログラム方法を提供する。

【解決手段】本発明のプログラム方法によると、シャドープログラム方式によってYZ平面の各層に属したメモリセルがマルチビットデータにプログラムされ、YZ平面のN番目の層(ここで、Nは1、またはそれより大きい定数)のメモリセルがプログラムされる場合、YZ平面の他層のメモリセルがプログラムされる前にN番目の層に対応するXZ平面の残りのメモリセルがプログラムされる。

(もっと読む)

半導体メモリセルおよびその製造方法

【課題】スイッチング特性に優れ、セルサイズの小さい半導体メモリセルを提供することにある。

【解決手段】ゲート絶縁膜が強誘電体膜4で構成されたMFSFET21からなるメモリ素子と、ゲート絶縁膜が常誘電体膜9で構成されたMISFET22からなる選択スイッチング素子とを備えた半導体メモリセル20であって、MFSFETの第1のゲート電極3は、基板1上の結晶性絶縁膜2表面に形成された結晶性導電膜3からなり、強誘電体膜4は、第1のゲート電極3を覆って結晶性絶縁膜2上に形成され、常誘電体膜9は、半導体膜5を介して強誘電体膜4上に形成され、MISFET22の第2のゲート電極10は、常誘電体膜9上に形成されている。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】メモリセルの高集積化と動作電圧の低電圧化を実現する半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体基板10上に、第1半導体領域、第2半導体領域、及びゲート電極を有するセルトランジスタが形成されている。さらに、半導体基板10上に、電極19、強誘電体膜19、及び電極20が形成されている。電極18は、半導体基板面に対して垂直な方向に沿った膜面を有し、強誘電体膜19側の膜面に突起部18Aを有する。電極20は、電極18に対向するように配置されている。さらに、電極18と電極20との間には強誘電体膜19が形成されている。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】強誘電体キャパシタの下部電極とバリアメタル膜との間の酸化膜の形成を防止する半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、トランジスタTのソース/ドレイン拡散層11に接続するように形成された第1、第2のビアコンタクト23、24と、バリアメタル膜31を介して第1、第2のビアコンタクト23、24に接続された強誘電体キャパシタCとを備える。強誘電体キャパシタCは、バリアメタル膜31上に設けられた下部電極32と、強誘電体膜33と、上部電極34とを備える。下部電極32は、錐台形状の上部322と、この上部322に比べ水平方向に突出した鍔部を有する底部321とからなり、下部電極32の底部321は、バリアメタル膜31の上面を全て覆い、バリアメタル膜31の端面、鍔部の端面、及び強誘電体膜33の端面が水平方向において整合している。

(もっと読む)

強誘電体、圧電体及びこれらの製造方法

【課題】強誘電特性及び圧電特性の劣化が抑制され、リーク特性が改善された強誘電体及び圧電体を提供する。

【解決手段】BiFeO3を主成分とする強誘電体及び圧電体13は、BiFeO3の複数のFeサイトが、Tiと、Mn、Ni及びCuのいずれかとに元素置換されている。BiとFeとTiとMn、Ni及びCuのいずれかとからなるターゲットにパルスレーザを照射することで、基板11上に、BiとFeとTiとMn、Ni及びCuのいずれかとを堆積させることにより、BiFeO3を主成分とする強誘電体又は圧電体13の製造方法。

(もっと読む)

半導体記憶装置

【課題】強誘電体キャパシタの水素による特性劣化および上部電極へのダメージを抑制しつつ、微細化に適した半導体記憶装置の提供。

【解決手段】第1の層間膜ILD1を貫通してトランジスタのソースまたはドレインの一方に接続された第1のプラグPLG1と、第1の層間膜を貫通してトランジスタのソースまたはドレインの他方に接続された第2のプラグPLG2と、第1のプラグの上方に設けられ第1のプラグに電気的に接続された下部電極LE、強誘電体膜FE、および、上部電極UEを含む強誘電体キャパシタFCと、強誘電体キャパシタを被覆する水素バリア膜HBと、水素バリア膜上に設けられた第2の層間膜ILD3と、第2の層間膜および水素バリア膜上に設けられ、水素バリア膜を貫通して上部電極に接続されたローカル配線LICと、ローカル配線、第2の層間膜および水素バリア膜を貫通して第2のプラグに接続された貫通プラグPPLGとを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】水素バリア膜の成膜時に生じるダストを効果的に除去することができる半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体記憶装置は、半導体基板10上に設けられたトランジスタSTと、トランジスタST上に形成された第1の層間絶縁膜ILD1と、第1の層間絶縁膜ILD1内に設けられ、トランジスタSTの拡散層DL1に接続された下部コンタクトプラグCP1と、下部コンタクトプラグCP1および第1の層間絶縁膜ILD1上に形成された下部電極LE、強誘電体膜FEおよび上部電極UEを含む強誘電体キャパシタFCと、強誘電体キャパシタFCの周辺に設けられた第2の層間絶縁膜ILD2と、強誘電体キャパシタFCの側面と第2の層間絶縁膜ILD2との間に形成されたトレンチ50の内部を充填し、強誘電体キャパシタFCの側面を被覆し、水素の透過を抑制する第1のバリア膜BM1とを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】強誘電体膜のダメージを抑制した縦型の強誘電体キャパシタを有する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板11と、半導体基板11上に互いに離間して配設されたソース及びドレインのいずれかとなる拡散層16を有するトランジスタ13と、半導体基板11表面にほぼ垂直に縦方向に伸び、拡散層16にコンタクトプラグ19を介して接続された電極35と、電極35に対向し、半導体基板11表面にほぼ垂直に縦方向に伸び、拡散層16にコンタクトプラグ19を介して接続された電極36と、対向する両面が電極35及び電極36にそれぞれ接した強誘電体膜33と、強誘電体膜33に接してトランジスタ13の側に配設され、対向する電極35及び電極36のいずれか一方に接したシード膜23とを備えている。

(もっと読む)

キャパシタ、強誘電体メモリ装置、アクチュエータおよび液体噴射ヘッド

【課題】結晶性の良好な誘電体膜を有し、良好なヒステリシス特性を有することができるキャパシタを提供する。

【解決手段】本発明に係るキャパシタ100は,下部電極4と、下部電極4の上方に形成され、ニオブ酸チタン酸ジルコン酸鉛からなる第1誘電体膜11と、第1誘電体膜11の上方に形成され、チタン酸ジルコン酸鉛、または、前記第1誘電体膜を構成するニオブ酸チタン酸ジルコン酸鉛よりもNb組成が小さいニオブ酸チタン酸ジルコン酸鉛からなる第2誘電体膜13と、第2誘電体膜13の上方に形成された上部電極6と,を含む。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】強誘電体キャパシタの側壁残渣を除去し、かつ、水素による強誘電体キャパシタの特性劣化を抑制する半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体記憶装置は、半導体基板上に設けられたスイッチングトランジスタと、スイッチングトランジスタ上に形成された層間絶縁膜と、層間絶縁膜中に形成されたコンタクトプラグと、コンタクトプラグおよび層間絶縁膜の上方に形成され、下部電極、強誘電体膜および上部電極を含む強誘電体キャパシタと、半導体基板に形成され、コンタクトプラグとスイッチングトランジスタとの間を電気的に接続する拡散層と、強誘電体キャパシタの側面に形成された水素バリア膜と、上部電極の上面全体を被覆しかつ該上部電極の上面に接触するTiN膜またはTiAlN膜を含む配線とを備えている。

(もっと読む)

半導体記憶装置

【課題】メモリトランジスタの上部に、メモリトランジスタと平行に配置される強誘電体キャパシタを構成する強誘電体膜の膜厚バラツキを低減する。

【解決手段】強誘電体メモリ70では、メモリトランジスタのソース及びドレインの一方に接続される台座電極FDD上には、側面が強誘電体膜12と接する電極FDが設けられる。メモリトランジスタのソース及びドレインの他方に接続される台座電極SDD上には、電極SDが設けられる。電極SDの下部側面を除く両側面には、電極TDが設けられる。電極SD及び電極TDは電極STDを構成し、電極FDと電極STDの間に強誘電体膜12が設けられる。電極FD、強誘電体膜12、及び電極STDは強誘電体キャパシタを構成する。強誘電体膜12はMOCVD法により電極SDの両側面に形成され、電極TDはCVD法により強誘電体膜12の側面に形成される。

(もっと読む)

半導体記憶装置

【課題】メモリセルの強誘電体キャパシタの分極特性のバラツキを低減しつつ、回路面積の縮小を図ることが可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板に第1の方向に延びる素子領域上に形成され、ビット線とプレート線との間で複数個直列に接続された同一導電形のセル選択MOSトランジスタと、素子領域上に層間絶縁膜を介して形成された強誘電体膜と、セル選択MOSトランジスタのソース拡散層に電気的に接続され強誘電体膜の下方に形成された下部電極と、セル選択MOSトランジスタのドレイン拡散層に電気的に接続され強誘電体膜の上方に形成された上部電極と、を有し、セル選択MOSトランジスタに一対一に並列に接続された複数の強誘電体キャパシタと、備え、強誘電体キャパシタは、隣接する2つの素子領域上において、第1の方向に交互に配置されている。

(もっと読む)

半導体記憶装置

【課題】温度の変化に対し常に信号量の変化を最大化した形での読み出し動作を可能とした半導体記憶装置を提供することができる。

【解決手段】ビット線電圧制御回路3は、読み出し時に選択ビット線に結合されてその電位を引き下げるためのカップリング用キャパシタC1、C2と、その一端N1、N2を選択的にビット線対/BL、BLに接続するためのNMOSトランジスタQ11、Q21を有する。キャパシタC1、C2の他端は電圧発生回路4に接続され、制御信号線V1、V2から所定の電圧を与えられる。この制御信号線V1、V2の電圧は、所定の温度特性を与えられている。

(もっと読む)

1 - 20 / 61

[ Back to top ]