Fターム[5F083GA28]の内容

Fターム[5F083GA28]に分類される特許

541 - 550 / 550

強誘電体メモリ及びその製造方法

【課題】 製造プロセスの簡略化及び信頼性の向上が図れる強誘電体メモリ及びその製造方法を提供することにある。

【解決手段】 強誘電体メモリは、基体10と、基体10の上方に形成された絶縁層12と、絶縁層12を貫通するコンタクトホール20と、コンタクトホール20の内部に形成されたプラグ34と、プラグ34の上方に形成され、かつ、コンタクトホール20の内部に一部が形成された第1の部分62と、第1の部分62と一体化して絶縁層12の上方に形成された第2の部分64と、を含むバリア層60と、プラグ34の上方を含む領域に、下部電極42、強誘電体層44及び上部電極46が順に積層して形成された強誘電体キャパシタ40と、を含む。

(もっと読む)

強誘電体メモリ及びその製造方法

【課題】 製造プロセスの簡略化及び信頼性の向上を図ることにある。

【解決手段】 強誘電体メモリの製造方法は、(a)基体10の上方に形成された絶縁層20に、第1及び第2のコンタクトホール22,24を形成すること、(b)第1及び第2のコンタクトホール22,24のそれぞれの内部に、絶縁層20の上面よりも低い上面を有するプラグ42,44を形成すること、(c)第1及び第2のコンタクトホール22,24のそれぞれのプラグ42,44の上方に、バリア層52,54を形成すること、(d)下部電極82、強誘電体層84及び上部電極86を順に積層して積層体81を形成すること、(e)積層体81をエッチングすることによって、第1のコンタクトホール22のプラグ42の上方を含む領域に、強誘電体キャパシタ80を形成すること、を含む。バリア層52,54は、下部電極82よりもエッチングされにくい性質を有する。

(もっと読む)

磁気抵抗効果装置およびその製造方法

【課題】磁界を効率よく記憶素子に集束させることができ、配線間のショートが防止された磁気抵抗効果装置およびその製造方法を提供する。

【解決手段】互いに平行に配置される複数の第1配線11と、第1配線11の上方に離間して配置されるとともに、互いに平行に配置される複数の第2配線12と、第1配線11と第2配線12との間の一領域に、磁気抵抗型のTMR素子13とを備えた磁気抵抗効果装置であって、各第2配線12上を覆うとともに、隣接する第2配線12間に連続して設けられた絶縁性の高透磁率材料からなる第2磁性体層22bを備えたことを特徴とする磁気抵抗効果装置およびその製造方法である。

(もっと読む)

半導体装置およびその製造方法

【課題】 標準CMOSロジックプロセスに不揮発メモリを混載するために必要な追加マスク枚数を削減し、製造期間短縮とコスト低減を図る。

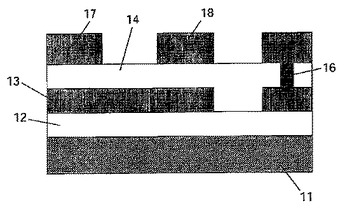

【解決手段】 サイドウォール構造を利用し、ゲート電極がシリサイド化されたスプリットゲート型メモリセルにおいて、選択ゲート電極12に隣接して、孤立した補助パターン22を配置する。両者の間隙にサイドウォールゲートのポリシリコンが充填され自己整合的に形成された配線部23に対してコンタクト21を取る。コンタクト21は補助パターン22および素子分離領域に重なっても良く、占有面積を考慮して設計最適化できる。選択ゲート電極12との距離をx、ONO膜の堆積厚さをt、ポリシリコン膜の堆積厚さをdとおけば、x<2×(t+d)となる距離xだけ離れて補助パターン22を配置すればよい。

(もっと読む)

半導体装置およびその製造方法

【課題】 トンネル絶縁膜の特性を確保した上で消去動作後のVth素分布幅の拡大を防止し、さらに所定の場合デバイス動作速度を向上させることができる半導体装置およびその製造方法を提供する。

【解決手段】 トレンチに絶縁膜を充填して分離絶縁膜5を形成する工程と、分離絶縁膜を保護膜が露出されるまで平坦化する工程と、保護膜を除去して第1ポリシリコン層3と分離絶縁膜5との上に第2ポリシリコン層4を形成する工程とを有し、第1ポリシリコン層形成工程では、第1ポリシリコン層としてノンドープのシリコン層を形成し、第2ポリシリコン層形成工程では、第2ポリシリコン層としてドープトシリコン層を形成するか、またはノンドープシリコン層を形成してその後に不純物を注入するかして、その第2ポリシリコン層中の不純物を、その後の熱履歴により、第1ポリシリコン層へと熱拡散させる。

(もっと読む)

電気デバイスおよびその製造方法

本発明は、パンチスルーダイオード(S)と直列に接続されたプログラマブル抵抗器(PR)を有する電気デバイス(図6)に関する。本発明はまた、そのような電気デバイスの製造方法に関する。前記方法は、第1の導電型とは反対の第2の導電型の半導体材料からなる第2の層と第3の層との間に配置された、第1の導電型の半導体材料からなる第1の層を含む積層体を設けるステップと、プログラマブルな抵抗率を有する材料の層であって、半導体材料の第2および第3の層のうちの1つと電気的に接触している、プログラマブルな抵抗率を有する材料の層を設けるステップとを含む。  (もっと読む)

(もっと読む)

不揮発性強誘電体メモリ装置の製造方法及びその方法によって得られるメモリ装置

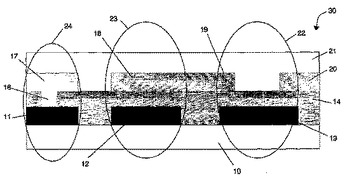

本発明は、トランジスタ22及びキャパシタ23を含んでいる不揮発性強誘電体メモリ装置30に関し、特に、不揮発性で、電気的に消去可能、かつプログラム可能な強誘電体メモリ素子及びそのような不揮発性強誘電体メモリ装置30を生産する方法に関する。本発明による方法は、トランジスタ22のゲート誘電体層及びキャパシタ23の誘電体層は同一の有機又は無機強誘電体層から作られるので、限られた数のマスクステップを含む。  (もっと読む)

(もっと読む)

有機両極性半導体を使用する不揮発性強誘電体薄膜デバイス及びそのようなデバイスを処理するための方法

有機強誘電体高分子と有機両極性半導体との組み合わせを備える不揮発性強誘電体メモリデバイスが提案されている。本発明に係るデバイスは、高分子に適合し、また、高分子の利点、即ち、溶液処理、低コスト、低温層堆積及びフレキシブル基板との適合性を十分に活用している。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置

【課題】 メモリセルの書込み特性のばらつきに起因する書込みベリファイ回数の増加を抑制し、書込み時間の短縮をはかり得るEEPROMを提供すること。

【解決手段】 Si基板1上に浮遊ゲート4と制御ゲート6を積層し、電気的書替え可能としたメモリセルが2次元配置されたメモリセルアレイと、基板1とゲート6の間に消去パルスを印加する消去機構と、基板1とゲート6の間に消去パルスと逆極性の低い電圧の事前書込みパルスを印加する事前書込み機構と、事前書込みパルス印加後の状態を検知するしきい値ベリファイ機構と、基板1とゲート6の間に消去パルスと逆極性の高い電圧の書込みパルスを印加する書込み機構とを備えたEEPROMであって、消去動作の後、事前書込み動作としきい値ベリファイ動作を、最も速く変動するメモリセルのしきい値が消去状態の所望の値に達するまで繰返し、次いで書込み動作によってデータ書込みを行うことを特徴とする。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】ビット線とセルコンタクト部の容量接続用コンタクトとのショートを防止し、容量接続用コンタクトとビット線とのマージンを大きくすることができる半導体記憶装置及びその製造方法の提供。

【解決手段】STIにより活性領域が分離形成された半導体基板上の第1の層間絶縁膜4に活性領域まで貫通するコンタクト孔5を設け、その内部に第1の層間絶縁膜上面よりも低い位置まで多結晶シリコン6を充填した後、多結晶シリコン上部にシリサイド膜12を形成し、第1の層間絶縁膜上の所定領域にポリサイド膜又はメタル膜を含むビット線7とビット線の上面及び側面にシリコン窒化膜を形成した後、ビット線で覆われていないコンタクト孔内部のシリサイド膜を除去することにより、シリンダ型容量と接続されるコンタクト孔内部の導電体とそのコンタクト孔に隣接するビット線とを分離する。その後、第2の層間絶縁膜10を堆積し、シリサイド膜を除去したコンタクト孔まで貫通するシリンダ型容量パターンを形成する。

(もっと読む)

541 - 550 / 550

[ Back to top ]