Fターム[5F083PR05]の内容

Fターム[5F083PR05]に分類される特許

1,301 - 1,312 / 1,312

半導体記憶装置およびその製造方法

【課題】半導体記憶装置の製造方法。

【解決手段】領域10Cを画定する素子分離溝を形成する工程と、半導体層10の上部コーナー部11を熱酸化によりラウンディング形状にする第1ラウンド酸化工程と、半導体層10の上方に、耐酸化膜50を形成する工程と、領域10A,10Bにおいて、素子分離溝に隣接した半導体層10の上部のコーナー部11を熱酸化によりラウンディングする第2ラウンド酸化工程と、素子分離溝に分離絶縁層20を形成する工程と、半導体層10の上方にトンネル絶縁層31を形成する工程と、トンネル絶縁層31の上方にフローティングゲート電極32を形成する工程と、フローティングゲート電極32に印加する電圧を制御するコントロールゲート42を形成する工程と、半導体層10にソースおよびドレイン領域を形成する工程とを含み、第1ラウンド酸化工程における熱酸化温度は、第2ラウンド酸化工程に熱酸化温度より高い。

(もっと読む)

不揮発性記憶装置

【課題】 FNトンネル電流を利用して動作する不揮発性記憶装置において、トンネル絶縁膜の膜厚を制御することで、動作特性が向上した不揮発性記憶装置の製造方法を提供する。

【解決手段】 本発明の不揮発性記憶装置は、半導体層10と、

前記半導体層10に形成された第1のトレンチ20aと、

前記第1のトレンチ20aに形成された第1の分離絶縁層20と、

前記第1の分離絶縁層20により画定された第1の領域10Cと、

少なくとも前記第1の領域10Cの前記半導体層10の上方に設けられた絶縁層30と、

前記絶縁層30の上方に設けられたフローティングゲート電極32と、

前記フローティングゲート電極32に印加する電圧を制御するコントロールゲート42と、を含み、

前記第1の分離絶縁層20と前記第1の領域10Cの前記半導体層10との境界部である第1の境界部分の上方に設けられた前記絶縁層30の膜厚は、該第1の境界部分の上方以外に設けられている前記絶縁層30の膜厚と比して小さい。

(もっと読む)

ゲート型電界効果デバイス及びその製法

本発明はゲート型電界効果デバイスに関し、その製法にも関する。一例では、ゲート型電界効果デバイスはソース/ドレーン領域ペアを含み、チャンネル領域をそれらの間に有している。ゲートはソース/ドレーン領域間でチャンネル領域に近接して受領される。ゲートはソース/ドレーン領域間にゲート幅部を有している。ゲート誘電体はチャンネル領域とゲートに近接して受領される。ゲート誘電体は少なくとも2つの異なる領域をゲートの幅部に沿って有している。これら異なる領域はそれぞれ異なる誘電率kを有する2つの異質領域を提供するように異なる材料で提供される。 (もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】シリコン基板にダメージを与えることなく、ウェットエッチングにより剥離することなく、小さい径のトンネル窓を形成できる不揮発性半導体記憶装置の製造方法の提供。

【解決手段】第1に反射防止膜7を介してKrF線レジスト8を塗布する。これによりレジストの開口寸法自体を小さくすると共に密着性を向上させてウェットエッチング中の剥離を防止する。第2に反射防止膜7のドライエッチングの際に第1の絶縁膜2の途中でエッチングを止める。これにより反射防止膜7を除去すると共に第1の絶縁膜2をドライエッチングにより薄膜化することによってその後のウェットエッチングの時間を短くして基板面方向への広がりを抑制する。第3に第1の絶縁膜2をウェットエッチングにより除去する。これによりシリコン基板1にプラズマダメージが入ることがなくなり、トンネル絶縁膜の信頼性を向上させる。

(もっと読む)

容器コンデンサ及び作製方法

【課題】半導体構造体、及び複数のコンデンサ装置の作製方法を提供する。

【解決手段】本発明の例示的方法においては、絶縁材(28)中の開口部内に導電性蓄積ノード部材(60)が形成されて導電性容器が作製される。保持構造体(30)が容器の少なくとも一部と物理的接触状態となるように形成され、次いで絶縁材(28)が除去されることにより容器の外側表面が露出される。保持構造体(30)によって容器構造体のぐらつきあるいは他の構造上の欠陥が減じられる。導電性容器は第一コンデンサ電極に相当する。容器の外側側壁が露出された後、絶縁材(100)が容器内に露出された外側側壁に沿って形成される。その後に第二コンデンサ電極(103)が絶縁材上へ形成される。これら第一及び第二コンデンサ電極と絶縁材とによって複数のコンデンサ装置が作製される。

(もっと読む)

2−トランジスタメモリセル及びその製造方法

本発明は、メモリゲートスタック(1)を有する記憶トランジスタ(1)及び選択トランジスタを有する2-トランジスタメモリセルを基板(50)上に製造する方法であって、トンネル誘電層(51)が前記基板(50)と前記メモリゲートスタック(1)との間にもたらされる方法を提供する。前記方法は、第一の導電層(52)及び第二の導電層(54)をもたらし、前記第二の導電層(54)をエッチし、それによってコントロールゲートを形成し、前記第一の導電層(52)をエッチし、それによってフローティングゲートを形成することによって前記メモリゲートスタック(1)を形成するステップを有する。前記方法は更に、前記第一の導電層(52)がエッチされる前に、前記トンネル誘電層(51)の下に形成されるべきチャネルの方向で前記コントロールゲートに対してスペーサ(81)を形成するステップと、その後、前記第一の導電層(52)をエッチするために前記スペーサ(81)をハードマスクとして使用し、それによって前記フローティングゲートを形成し、それによってフローティングゲートをコントロールゲートに自己整合させるステップとを有することを特徴とする。本発明は、前記コントロールゲート(54)は前記フローティングゲート(52)よりも小さくなり、スペーサ(81)が、前記コントロールゲート(54)に隣接してもたらされるメモリセルも提供する。  (もっと読む)

(もっと読む)

半導体装置作製における垂直向きコンデンサ用支持体

半導体装置に用いる両面コンデンサの作製方法であって、該方法は、ウェハー加工間、コンデンサ底板(110)を支持する絶縁体構造体(86)を形成する工程を含む。前記構造体は、底板外側を露出させて両面コンデンサを作製するため底部絶縁体層(84)の除去中底板を支える点において特に有用である。支持構造体によって、セル誘電体層(200)、コンデンサ上板(202)及び最終絶縁体(204)の作製中も底板が支持される。また本発明による構造体についても開示されている。

(もっと読む)

(もっと読む)

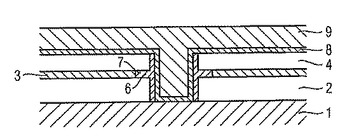

デバイス内にバリア層を有するコンタクトホールを形成する方法及び得られるデバイス

デバイスの下層(2)にコンタクトを形成する方法は、コンタクトホール(5)を形成するステップと、デバイスのコンタクトホール内にバリア材からなるコンタクトホールバリア層(7)を形成するステップと、コンタクトホールの底面のコンタクトホールバリア層をエッチングするステップと、コンタクトホール内にライナ材(8)を堆積するステップと、コンタクトホールに導電性材料(9)を充填するステップとを有する。半導体、受動素子、キャパシタ又はFeRAMなどのデバイスが上記方法に従って形成される。コンタクトホールの側壁にあるコンタクトホールバリア層(7)が、水素及び/又は酸素の側方拡散を抑制する。コンタクトホールバリア層は、ウェットエッチングプロセスによって生じる既存のバリア層(3)内のボイド(6)を充填するために上記プロセス後に、又は既存のバリア層への損傷を抑制するために上記プロセス前に行うことができる。

(もっと読む)

(もっと読む)

垂直方向の突起部を有するフローティングゲート構造

基板面から離れて延在する突起部を有するフローティングゲート構造を開示する。この突起部によって、フローティングゲートとコントロールゲートとを結合するための増加した表面積をフローティングゲートに提供することが可能となる。1つの実施形態では、フローティングゲートの個々の側面でワードラインが下方へ延在して、同じ列の隣接するフローティングゲートを遮蔽する。別の実施形態では、突起部を有するフローティングゲートの組立て製造処理工程を開示する。残りのフローティングゲートに対して自己位置合せを行うために突起部を形成してもよい。  (もっと読む)

(もっと読む)

半導体記憶装置及びその製造方法

【課題】ビット線とセルコンタクト部の容量接続用コンタクトとのショートを防止し、容量接続用コンタクトとビット線とのマージンを大きくすることができる半導体記憶装置及びその製造方法の提供。

【解決手段】STIにより活性領域が分離形成された半導体基板上の第1の層間絶縁膜4に活性領域まで貫通するコンタクト孔5を設け、その内部に第1の層間絶縁膜上面よりも低い位置まで多結晶シリコン6を充填した後、多結晶シリコン上部にシリサイド膜12を形成し、第1の層間絶縁膜上の所定領域にポリサイド膜又はメタル膜を含むビット線7とビット線の上面及び側面にシリコン窒化膜を形成した後、ビット線で覆われていないコンタクト孔内部のシリサイド膜を除去することにより、シリンダ型容量と接続されるコンタクト孔内部の導電体とそのコンタクト孔に隣接するビット線とを分離する。その後、第2の層間絶縁膜10を堆積し、シリサイド膜を除去したコンタクト孔まで貫通するシリンダ型容量パターンを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】 強誘電体キャパシタに保護膜を設け、強誘電体膜の還元を抑制する。

【解決手段】 前記保護膜としてAl2 O3 膜を、3.0〜3.1g/cm3 、あるいはそれ以上の密度に形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 実効的な素子特性を向上させ、または素子領域の基板表面が露出することを防止することが可能な半導体装置及びその製造方法を提供する。

【解決手段】 半導体基板101の表面上にシリコン酸化膜102を形成し、この表面上に埋め込み酸化膜の平坦化ストッパー材となるシリコン窒化膜103を形成する。半導体基板101にトレンチ105を形成した後、シリコン酸化膜102の側面にエッチングを行って後退させる。半導体基板101の露出している表面に酸化を行って素子領域の表面に丸みを付ける。これにより、素子領域の実効寸法を実寸法よりも大きくすることができる。

(もっと読む)

1,301 - 1,312 / 1,312

[ Back to top ]