Fターム[5F083PR13]の内容

Fターム[5F083PR13]に分類される特許

1 - 20 / 77

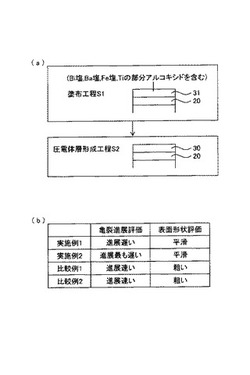

圧電体前駆体溶液、圧電セラミックスの製造方法、圧電素子の製造方法、液体噴射ヘッドの製造方法、及び、液体噴射装置の製造方法

【課題】少なくともBi、Ba、Fe及びTiを含む圧電体層を有する圧電素子、液体噴射ヘッド及び液体噴射装置の性能を向上させることにある。

【解決手段】少なくともビスマス、バリウム、鉄及びチタンを含むペロブスカイト型酸化物を形成するための圧電体前駆体溶液は、少なくとも、ビスマス塩、バリウム塩、鉄塩、並びに、チタンの部分アルコキシド(チタンにアルコキシ基及び該アルコキシ基以外の官能基が結合したチタン化合物)を含む。圧電セラミックスの製造方法は、前記圧電体前駆体溶液を塗布する工程と、該塗布した前駆体溶液を結晶化させてペロブスカイト型酸化物を含む圧電セラミックスを形成する工程と、を備える。圧電素子の製造方法は、前記圧電セラミックスに電極を形成する工程を備える。液体噴射ヘッドの製造方法は、前記圧電素子の製造方法により圧電素子を形成する工程を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】 対象セルのワード線に隣接するワード線の電位の影響に伴う対象セルのビット線への電界を緩和する。

【解決手段】 半導体基板100に形成され、半導体素子101を形成するための活性領域と、半導体基板100内に形成され、活性領域を分離するための素子分離領域(STI102、NF104)と、素子分離領域(STI102、NF104)内に設けられた空洞部105を有する半導体装置。

(もっと読む)

不揮発性記憶素子および不揮発性記憶装置

【課題】電極と抵抗変化層の界面に小さな突起を形成することなく、低電圧での初期化が可能な不揮発性記憶素子を提供する。

【解決手段】下部電極105と上部電極107との間に介在され、両電極間に与えられる電気的信号に基づいて可逆的に抵抗値が変化する抵抗変化層116を備える。抵抗変化層116は、第1の抵抗変化層1161と第2の抵抗変化層1162との少なくとも2層から構成され、第1の抵抗変化層1161は第1の遷移金属酸化物116bから構成され、第2の抵抗変化層1162は、第2の遷移金属酸化物116aと第3の遷移金属酸化物116cとから構成され、第2の遷移金属酸化物116aの酸素不足度は第1の遷移金属酸化物116bの酸素不足度及び第3の遷移金属酸化物116cの酸素不足度のいずれよりも高く、第2の遷移金属酸化物116a及び第3の遷移金属酸化物116cは、第1の抵抗変化層1161と接している。

(もっと読む)

記憶素子および記憶装置

【課題】良好なデータ保持特性を維持しつつ、安定したスイッチング特性を有する記憶素子および記憶装置を提供する。

【解決手段】下部電極10、記憶層20および上部電極30をこの順に積層した記憶素子1において、記憶層20はイオン源層21と、抵抗変化層22と、抵抗変化層22よりも高い導電率を示すバリア層23とを有する。これにより、データ消去時における電流パスあるいは不純物準位を形成する金属イオンの移動効率が改善される。

(もっと読む)

不揮発性半導体記憶装置

【課題】柱状のチャネル層となる半導体層に沿って、複数の浮遊ゲート型の不揮発性メモリセルが積層された構造の不揮発性半導体記憶装置を提供する。

【解決手段】実施形態によれば、柱状の半導体膜131の側面にトンネル誘電体膜141、浮遊ゲート電極膜142、ゲート間絶縁膜143および制御ゲート電極膜144を備えるメモリセルMCが半導体膜131の延在方向に複数設けられるメモリセル列を、半導体基板101上に略垂直に複数配置した不揮発性半導体記憶装置が提供される。ここで、浮遊ゲート電極膜142と制御ゲート電極膜143は、柱状の半導体膜131の全周のうち特定の方向の側面にのみ形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の製造工程を増加させることなく絶縁破壊耐性に優れた信頼性に懸念のない、小さな占有面積で所期の容量を確保する容量密度の高いパスコンを備えた半導体装置を実現する。

【解決手段】パスコンについて、第1の容量絶縁膜が、記憶素子のトンネル絶縁膜と共に第1の絶縁膜23で形成され、下部電極である第1の電極26が、記憶素子の浮遊ゲート電極25と共にドープト・アモルファスシリコン膜24(結晶化されたもの)で形成され、第2の容量絶縁膜が、周辺回路の5Vのトランジスタのゲート絶縁膜と共に第2の絶縁膜33で形成され、上部電極である第2の電極37が、記憶素子の制御ゲート電極36及び周辺回路のトランジスタのゲート電極41と共に多結晶シリコン膜34で形成される。

(もっと読む)

半導体記憶装置

【課題】信頼性が高い半導体記憶装置を提供する。

【解決手段】実施形態に係る半導体記憶装置は、基板と、前記基板上に設けられ、それぞれ複数の絶縁膜及び電極膜が交互に積層され、対向する第1の階段及び第2の階段を有する積層体と、前記第1及び第2の階段が形成されている領域外の前記積層体内に設けられ、前記絶縁膜及び前記電極膜の積層方向に延びる半導体部材と、前記電極膜と前記半導体部材との間に設けられた電荷蓄積層とを備える。そして、前記電極膜は、前記第1の階段に形成された第1のテラスと、前記第2の階段に形成された第2のテラスと、前記第1のテラス及び前記第2のテラスを接続するブリッジ部とを有する。

(もっと読む)

周期的な酸化およびエッチングのための装置と方法

半導体記憶装置及びその製造方法

【課題】1メモリセルが6トランジスタを有するSRAMにおいて、コンタクトの微細化をするとリークの発生を回避できる半導体記憶装置及びその製造方法を提供する。

【解決手段】1メモリセルが第1及び第2ドライバトランジスタ(DTr1、DTr2)、第1及び第2転送トランジスタ(TTr1,TTr2)並びに第1及び第2ロードトランジスタ(LTR1,LTr2)の6トランジスタを有するSRAMにおいて第1ドライバトランジスタと第2ドライバトランジスタのソースドレイン領域に基準電位を印加するための接地コンタクトCgと、第1ロードトランジスタと第2ロードトランジスタのソースドレイン領域に電源電位を印加するための電源電位コンタクトCcの径が、共通コンタクトCsを除く他のコンタクト(Cb,Cn,Cw)の径より大きく形成された構成とする。

(もっと読む)

半導体装置の製造方法

【課題】同一の半導体基板上にゲート絶縁膜の膜厚の異なる半導体素子領域を容易に形成することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板に素子分離絶縁膜を形成することにより、第1の半導体素子領域と第2の半導体素子領域とを画定する工程と、前記第2の半導体素子領域と前記第2の半導体素子領域を囲う前記素子分離絶縁膜を覆い、前記第1の半導体素子領域と前記第1の半導体素子領域を囲う前記素子分離絶縁膜を露出させるマスクを形成する工程と、前記マスクを用いて、前記第1の半導体素子領域を囲う前記素子分離絶縁膜をエッチングする工程と、前記素子分離絶縁膜をエッチングする工程の後、前記マスクを用いて前記第1の半導体素子領域に対して異方性エッチングを行う工程と、前記マスクを除去する工程と、前記マスクを除去した後に熱酸化により第1の半導体素子領域と第2の半導体素子領域とにゲート酸化膜を形成する工程と、を有することを特徴とする半導体装置の製造方法により上記課題を解決する。

(もっと読む)

MOS型半導体メモリ装置、その製造方法およびコンピュータ読み取り可能な記憶媒体

【課題】 電荷蓄積領域として機能する絶縁膜積層体のバンドギャップ構造を長期間維持し、優れたデータ保持特性と、高速でのデータ書換え性能と、低消費電力での動作性能と、高い信頼性と、を同時に兼ね備えたMOS型半導体メモリ装置を提供する。

【解決手段】 MOS型半導体メモリ装置601は、大きなバンドギャップを持つ第1の絶縁膜111および第5の絶縁膜115と、最も小さなバンドギャップを持つ第3の絶縁膜113との間に、両者の中間の大きさのバンドギャップを持つ第2の絶縁膜112および第4の絶縁膜114を備えている。第2の絶縁膜112と第3の絶縁膜113との間には、第1のブロック層112Bが設けられ、第3の絶縁膜113と第4の絶縁膜114との間には、第2のブロック層113Bが設けられている。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】メモリセル部と周辺回路部との段差を低減させつつ、メモリセル部を積層する。

【解決手段】メモリセル部R1には、層間絶縁膜11と半導体層9とが交互に積層された積層構造をフィン状に半導体基板1上に配置し、周辺回路部R2には、ゲート絶縁膜3を介してゲート電極4を半導体基板1上に配置し、ゲート電極4の上面の高さは、層間絶縁膜11と半導体層9とが交互に積層された積層構造の上面の高さと実質的に等しくなるように設定する。

(もっと読む)

半導体装置およびその製造方法

【課題】拡散層と拡散層に接続されるコンタクトとの接触抵抗を低減した半導体装置およびその製造方法を提供するものである。

【解決手段】本発明の半導体装置の製造方法は半導体基板にピラー部を設ける工程と、前記ピラー部の基端部近傍に第1の不純物拡散領域を形成する工程と、ピラー部の側面を被覆する第1の絶縁膜を形成するとともに、第1の絶縁膜を介してピラー部の側面に対向する電極層を形成する工程と、ピラー部及び第1の絶縁膜の周囲を埋める第2の絶縁膜を形成する工程と、第1の層間膜を除去して前記ピラー部の先端面を露出させる工程と、ピラー部の先端部に第2の不純物拡散領域を形成する工程と、第1の絶縁膜をエッチングして前記ピラー部の先端部の側面を露出させる工程と、ピラー部の先端面及びピラー部の先端部の側面を覆うようにコンタクトプラグを形成する工程と、を具備してなる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】抵抗変化型の半導体記憶装置において、記憶層の薄膜化と素子間のバラツキ抑制を両立させる。

【解決手段】抵抗変化型のメモリセルがアレイ状に並べられて構成されており、上記のメモリセルは、半導体基板10に形成された第1電極15と、第1電極の上層に形成されたイオン源層17と、イオン源層の上層に形成された第2電極19とを有し、第1電極とイオン源層の界面において、第1電極の表面あるいはイオン源層の表面が酸化されて抵抗変化型の記憶層16が形成された構成とする。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法においてSRAMのセルサイズを縮小することを目的とする。

【解決手段】メモリセルCの活性領域31a、31bが画定されたシリコン基板31と、素子分離絶縁膜32上に形成され、第1の方向に延在するゲート電極35と、シリコン基板31とゲート電極35の上に形成された第1の絶縁膜42と、第1の絶縁膜42を貫通し、ゲート電極35と第1の活性領域31aに重なり、第1の方向に直交する第2の方向に延在する第1の銅プラグ45aと、第2の活性領域35b上の第1の絶縁膜42を貫通する第2の銅プラグ45bと、第1の絶縁膜42上に形成された第2の絶縁膜44と、第2の絶縁膜44に埋め込まれ、第1の銅プラグ45aの側面45xから第2の延在方向に後退して形成され、第1の銅プラグ45aの上面の一部のみを覆う銅配線48aとを有する半導体装置による。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリホールの直径が均一な不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】シリコン基板10上にバックゲート電極13を形成し、バックゲート電極13の上面に凹部23を形成し、凹部23内に犠牲材を埋め込んだ後、絶縁膜14及び電極膜15を交互に積層して積層体11を形成する。次に、積層体11の中央部21にメモリホール24を形成し、その後、酸化処理を施す。これにより、メモリホール24の内面を起点として、電極膜15における絶縁膜14に接する部分が酸化され、その結果、中央部21において電極膜15が薄くなり、絶縁膜14が厚くなる。次に、積層体11の端部22において、電極膜15毎にステップ30を形成し、端部22を埋め込むように層間絶縁膜40を形成し、層間絶縁膜40中にステップ30に到達するようにプラグホール41を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】リーク電流が確実に抑制される、メモリセルを内蔵したマイコン等のロジック製品に係る半導体装置と、その製造方法を提供する。

【解決手段】ロジック領域RLにロジック部のトランジスタT1のゲート電極13bを形成する。ゲート電極13bの側壁をドライ酸化により酸化して、ゲート電極13bと半導体基板1との間に第1ゲートバーズビーク17を形成する。次に、メモリセル領域RMの表面上にフラッシュのメモリセルのトランジスタT2のフローティングゲート電極7a等を形成する。フローティングゲート電極7aの側壁をISSG酸化により酸化して、フローティングゲート電極7aと半導体基板1との間に第2ゲートバーズビークを形成する。

(もっと読む)

抵抗メモリのコントロールされた局在的欠陥パス

第1の電極上に金属酸化物層を形成する第1の電極を形成することと、金属酸化物の表面の露出部域および隠蔽部域を生成するために金属酸化物層をマスキングすることと、金属酸化物の露出部域を変化させ、露出部域の下方の局在的欠陥パスを生成することとを備えるコントロールされた局在的欠陥パスを形成する方法を含む、抵抗メモリのコントロールされた局在的欠陥パスが記載される。 (もっと読む)

半導体装置の製造方法

【課題】本発明の目的は、欠陥の少ない良質な塗布型酸化シリコン膜の製造方法を提供することにある。

【解決手段】本発明の一態様にかかる半導体装置の製造方法は、半導体基板に素子分離溝を形成し、前記素子分離溝の内部に、前記素子分離溝を埋め込むように、シリコン化合物膜を形成し、第1の温度での第1の酸化処理により、前記シリコン化合物膜の表面を、酸化剤及び不純物の通過を許容しつつもシリコン原子を含む揮発物が通過不可能な揮発物放出防止層に、改質し、前記第1の温度よりも高い第2の温度での第2の酸化処理により、前記素子分離溝の内部に、塗布型酸化シリコン膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】欠陥の発生を防止し且つ電気的特性に優れた強誘電体キャパシタを用いた半導体装置の製造方法を提供する。

【解決手段】第1の導電層40を形成し、第1の導電層40の表面に酸化膜10を形成し、酸化膜10を大気にさらし、酸化膜10を、減圧下且つ第1の温度で減圧加熱処理し、減圧加熱処理された酸化膜10を大気にさらすことなく、減圧下且つ第1の温度よりも低い第2の温度で、非晶質の第1の誘電体層41を酸化膜10上に形成し、第1の温度よりも高い第3の温度で、非晶質の第1の誘電体層41を結晶化する。

(もっと読む)

1 - 20 / 77

[ Back to top ]